# HIGH-SPEED HARRIS CORNER DETECTION USING RESIDUE NUMBER SYSTEM

YONG KUN MING

UNIVERSITI TEKNOLOGI MALAYSIA

# HIGH-SPEED HARRIS CORNER DETECTION USING RESIDUE NUMBER SYSTEM

YONG KUN MING

A project report submitted in fulfilment of the requirements for the award of the degree of Master of Engineering (Computer and Microelectronic Systems)

> School of Electrical Engineering Faculty of Engineering Universiti Teknologi Malaysia

### DEDICATION

This thesis is dedicated to my father, who taught me that the best kind of knowledge to have is that which is learned for its own sake. It is also dedicated to my mother, who taught me that even the largest task can be accomplished if it is done one step at a time.

### ACKNOWLEDGEMENT

In preparing this thesis, I was in contact with many people, researchers, academicians, and practitioners. They have contributed towards my understanding and thoughts. In particular, I wish to express my sincere appreciation to my main thesis supervisor, Dr Muhammad Afiq Nurudin bin Hamzah, for encouragement, guidance, critics and friendship. Without his continued support and interest, this thesis would not have been the same as presented here.

My fellow postgraduate student should also be recognised for their support. My sincere appreciation also extends to all my colleagues and others who have provided assistance on various occasions. Their views and tips are useful indeed. Unfortunately, it is not possible to list all of them in this limited space. I am grateful to all my family members.

#### ABSTRACT

Harris Corner Detector (HCD) is one of the common algorithms used in computer vision to locate the corner of an image for defining features. Corners are an important feature in computer vision because they are invariant to illumination change, translation or rotation, and image noise. This feature is widely used in motion detection, object tracking and recognition and stitching application. There are four main blocks in the Harris system, mask generation in spatial derivatives block, Gaussian filter block to remove unwanted noises, Harris response computation, and follow by non-maximum suppression block, which is used to compare and determine the corner pixel. HCD determine the corner by calculating the eigenvalue or change in intensity of shifting scanning window using Taylor series expansion. The Gaussian filtering is computationally expensive and requires a costly multiplier-accumulator (MAC unit). Therefore, the speed of HCD will be highly affected or limited by the MAC operation. The main objective of this project is to design a high speed HCD by implementing Residue number system (RNS) in the Gaussian filter block. The performance of the RNS-based HCD will be assess, benchmark with the MATLAB implementation of HCD and analyse using PPA (Power Performance Area). All the designs are synthesized using 180nm SilTerra library with fast database in Synopsys Design Compiler. In a conventional binary system, a large number will have a wider bit width and will require a larger arithmetic unit that slows down the computation. RNS is a fast arithmetic algorithm that is carry-free and can support high-speed and parallel arithmetic operations. RNS converts the larger number into a group of smaller numbers and performs the same math operation using a smaller math unit to speed up the design. The conventional binary number representation in the MAC unit of the computationally intensive Gaussian blocks was replaced by an RNS-based MAC unit. RNS with three moduli set,  $\{2n-1,2n,2n+1\}$ , n=9,13 provide the appropriate dynamic range to cover all the possible numbers in the kernel multiplication to prevent overflow. The CPD of the RNS-based Gaussian filter is reduced by 38%, with almost the same power consumption and an additional 21% area or gate count. The maximum operating frequency was increased by 60%, hence providing higher throughput than the conventional binary Gaussian filter. The results show that RNS is a good approach to improve computationally intensive applications such as digital filters and cryptographic applications with some additional areas.

#### ABSTRAK

Harris Corner Detector (HCD) merupakan salah satu algoritma yang digunakan untuk mencari sudut imej. Sudut ialah ciri penting dalam penglihatan komputer kerana HCD tidak berubah kepada perubahan pencahayaan, terjemahan atau putaran, dan hingar imej. Ciri ini digunakan secara meluas dalam pengesanan gerakan, pengesanan objek dan aplikasi pengecaman dan jahitan. Terdapat empat blok utama dalam HCD, blok terbitan spatial, blok penapis Gaussian, Harris, dan diikuti dengan blok penindasan bukan maksimum, yang digunakan untuk membandingkan dan menentukan piksel sudut. HCD menentukan sudut dengan mengira nilai eigenvalue atau perubahan intensiti menggunakan Taylor series expansion. Penapisan Gaussian adalah mahal dari segi pengiraan dan memerlukan pengganda-akumulator (MAC) yang mahal. Oleh itu, kelajuan HCD akan dihadkan oleh operasi MAC. Objektif utama projek ini adalah untuk mereka bentuk HCD berkelajuan tinggi dengan melaksanakan sistem nombor Residu (RNS) dalam blok penapis Gaussian. Prestasi akan dinilai, berbanding dengan MATLAB dan dianalisis menggunakan PPA. Semua reka bentuk disintesis dengan teknologi SilTerra 180nm mengunakan Synopsys Design Compiler. Nombor besar mempunyai lebar bit yang luas dan memerlukan unit aritmetik yang besar. RNS ialah algoritma aritmetik pantas yang bebas dibawa dan boleh menyokong operasi aritmetik berkelajuan tinggi. RNS menukar nombor besar kepada kumpulan nombor yang lebih kecil dan melakukan operasi matematik dengan unit matematik yang lebih kecil. Perwakilan nombor konvensional dalam unit MAC bagi blok Gaussian intensif pengiraan telah digantikan dengan unit MAC berasaskan RNS. RNS dengan tiga set moduli, {2n-1,2n,2n+1}, n=9,13 merangkumi semua nombor yang mungkin dalam pendaraban kernel. CPD bagi penapis Gaussian berasaskan RNS dikurangkan sebanyak 38%, dengan penggunaan kuasa yang hampir sama dan tambahan 21% kawasan atau kiraan pintu. Kekerapan operasi maksimum telah meningkat sebanyak 60%, justeru memberikan daya pemprosesan yang lebih tinggi daripada penapis Gaussian binari konvensional. Keputusan menunjukkan bahawa RNS ialah pendekatan yang baik untuk menambah baik aplikasi intensif pengiraan seperti penapis digital dan aplikasi kriptografi.

### TABLE OF CONTENTS

### TITLE

| DEC                         | CLARATION                          | iii  |

|-----------------------------|------------------------------------|------|

| DEL                         | iv                                 |      |

| ACH                         | v                                  |      |

| ABS                         | vi                                 |      |

| ABS                         | TRAK                               | vii  |

| TAE                         | viii                               |      |

| LIST                        | Γ OF TABLES                        | X    |

| LIST                        | Γ OF FIGURES                       | xi   |

|                             | Γ OF ABBREVIATIONS                 | xiii |

|                             | Г OF SYMBOLS                       | xiv  |

| LIST                        | Γ OF APPENDICES                    | XV   |

| CHAPTER 1                   | INTRODUCTION                       | 1    |

| 1.1                         | Introduction                       | 1    |

| 1.2                         | Problem Statement                  | 2    |

| 1.3                         | Research Goal                      | 3    |

| 1.4                         | Scope of Work                      | 4    |

| CHAPTER 2 LITERATURE REVIEW |                                    | 5    |

| 2.1                         | Introduction                       | 5    |

| 2.2                         | Overview of Harris Corner Detector | 5    |

| 2.3                         | Overview of Residue Number System  | 9    |

|                             | 2.3.1 Conversion of PNS to RNS     | 10   |

|                             | 2.3.2 Conversion of RNS to PNS     | 11   |

|                             | 2.3.3 Arithmetic Operation of RNS  | 11   |

| 2.4                         | Related Works                      | 13   |

| 2.5                         | Research Gap                       | 17   |

| CHAPTER 3                             | <b>RESEARCH METHODOLOGY</b>                 |          |  |

|---------------------------------------|---------------------------------------------|----------|--|

| 3.1                                   | Introduction                                | 19       |  |

| 3.2                                   | Algorithm of Harris Corner Detector         | 21       |  |

|                                       | 3.2.1 Spatial Derivatives                   | 22       |  |

|                                       | 3.2.2 Gaussian Filtering                    | 23       |  |

|                                       | 3.2.3 Harris Response                       | 24       |  |

| 3.3                                   | Non-Maximum Suppression                     | 24       |  |

| 3.4                                   | RNS Implementation of HCD                   |          |  |

|                                       | 3.4.1 Modified Gaussian Kernel Block        | 26       |  |

|                                       | 3.4.2 Dataflow Graph of the Gaussian Kernel | 27       |  |

|                                       | 3.4.3 RNS Moduli Set Selection              | 29       |  |

|                                       | 3.4.4 Forward Converter                     | 30       |  |

|                                       | 3.4.5 Backward Converter                    | 30       |  |

|                                       | 3.4.6 Modulo Adder                          | 31       |  |

|                                       | 3.4.7 Modulo Multiplier                     | 32       |  |

|                                       | 3.4.8 Proposed Design                       | 32       |  |

| 3.5                                   | Design Synthesis                            | 33       |  |

| 3.6                                   | Performance Comparison                      | 34       |  |

| CHAPTER 4 RESULTS AND DISCUSSION      |                                             | 35       |  |

| 4.1                                   | Corner Detection                            | 35       |  |

| 4.2                                   | Performance Analysis                        | 39       |  |

| CHAPTER 5 CONCLUSION AND FUTURE WORKS |                                             | 45       |  |

| 5.1                                   | Conclusion                                  | 45       |  |

| 5.2                                   | Future Works                                | 46       |  |

| REFERENCES                            |                                             | 47       |  |

| Appendices A – l                      | X                                           | 50 - 197 |  |

# LIST OF TABLES

| TABLE NO. | TITLE                                                              | PAGE |

|-----------|--------------------------------------------------------------------|------|

| Table 2.1 | Parameters of RNS {8,7,5,3}.                                       | 10   |

| Table 2.2 | Summary of previous work related to Harris Corner Detector.        | 14   |

| Table 2.3 | Summary of previous work related to Residue Number System.         | 16   |

| Table 3.1 | RNS moduli set selection.                                          | 29   |

| Table 3.2 | Type of proposed hardware design.                                  | 32   |

| Table 3.3 | Parameters used for MATLAB simulations.                            | 33   |

| Table 3.4 | Design Constraints for design compiler.                            | 33   |

| Table 4.1 | Number of corners detected.                                        | 38   |

| Table 4.2 | Synthesis result comparison for the RNS converter.                 | 39   |

| Table 4.3 | Synthesis result comparison for the modulo adder.                  | 40   |

| Table 4.4 | Synthesis result comparison for the modulo multiplier.             | 40   |

| Table 4.5 | Synthesis result comparison for the Gaussian filter.               | 41   |

| Table 4.6 | Synthesis result comparison for the Harris Corner Detector system. | 43   |

# LIST OF FIGURES

| FIGURE NO   | D. TITLE                                                              | PAGE |

|-------------|-----------------------------------------------------------------------|------|

| Figure 1.1  | Image stitching using corner detection [2].                           | 1    |

| Figure 2.1  | Methods to detect corner.                                             | 6    |

| Figure 2.2  | Region Classification Based on Intensity [15].                        | 6    |

| Figure 2.3  | Classification of Image Based on the Eigenvalues [17].                | 9    |

| Figure 2.4  | Binary-coded number format for RNS moduli set (8   7   5   3).        | 10   |

| Figure 2.5  | The structure of an arithmetic operation for RNS(8   7   5   3) [21]. | 12   |

| Figure 3.1  | Flowchart for overall project.                                        | 20   |

| Figure 3.2  | Working flow of the HCD system.                                       | 20   |

| Figure 3.3  | Functional block diagram of Harris system.                            | 21   |

| Figure 3.4  | Derivative kernel (Prewitt operator) (a) X-direction (b) Y-direction. | 22   |

| Figure 3.5  | 2-D 5x5 Gaussian filter.                                              | 23   |

| Figure 3.6  | 1-D Gaussian Kernels (a) 1x5 (b) 5x1.                                 | 24   |

| Figure 3.7  | Top-level module of Gaussian filter.                                  | 26   |

| Figure 3.8  | Proposed modified Gaussian filter block diagram.                      | 27   |

| Figure 3.9  | Dataflow graph of Gaussian kernel using shifter.                      | 28   |

| Figure 3.10 | Dataflow graph of Gaussian kernel using modulo multiplier.            | 28   |

| Figure 3.11 | Block diagram of forward converter.                                   | 30   |

| Figure 3.12 | Block diagram of backward converter.                                  | 31   |

| Figure 3.13 | Block diagram of modulo adder.                                        | 31   |

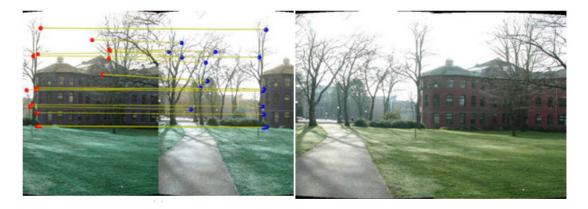

| Figure 4.1  | Corner detection on Blocks dataset.                                   | 36   |

| Figure 4.2  | Corner detection on House dataset.                                    | 37   |

| Figure 4.3  | Corner detection on Lena dataset.                                     | 38   |

| Figure 4.4  | CPD comparison of Gaussian filter using different clock period.       | 42   |

| Figure 4.5 | Area comparison of Gaussian filter using different clock period.  | 42 |

|------------|-------------------------------------------------------------------|----|

| Figure 4.6 | Power comparison of Gaussian filter using different clock period. | 43 |

| Figure 4.7 | Critical path of the Harris corner detector system.               | 44 |

# LIST OF ABBREVIATIONS

| - | Application-specific Integrated Circuit |

|---|-----------------------------------------|

| - | Chinese Remainder Theorem               |

| - | Design Compiler                         |

| - | Features from Accelerated Segment Test  |

| - | Least Significant Bit                   |

| - | Multiplier-Accumulator                  |

| - | Non-maximum Suppression                 |

| - | Positional Number System                |

| - | Power Performance Area                  |

| - | Residue Number System                   |

| - | Region of Interest                      |

| - | Synopsys Design Constrain               |

| - | Sum of Squared Difference               |

|   |                                         |

# LIST OF SYMBOLS

| Ι      | - | Intensity                     |

|--------|---|-------------------------------|

| D      | - | Dynamic Range                 |

| E(u,v) | - | Sum of All The SSD            |

| F      | - | Frequency                     |

| λ      | - | Eigenvalue of Harris Response |

| $m_i$  | - | Moduli Number                 |

| Р      | - | Power                         |

| R      | - | R Score of Harris Response    |

| X      | - | PNS Representation            |

| $x_i$  | - | <b>RNS</b> Representation     |

| -      |   | 1                             |

### LIST OF APPENDICES

| APPENDIX                  | TITLE                            | PAGE |

|---------------------------|----------------------------------|------|

| Appendix A Outputs of Spa | atial Derivative Block           | 50   |

| Appendix B Outputs of Ga  | ussian Filter Block              | 53   |

| Appendix C Outputs of Har | rris Response Block              | 56   |

| Appendix D Outputs of No  | n-Maximum Suppression Block      | 59   |

| Appendix E Synthesis Repo | ort of Gaussian Filter           | 62   |

| Appendix F Coding of Con  | ventional Harris Corner Detector | 64   |

| Appendix G RNS-Based H    | arris Corner Detector            | 90   |

| Appendix H Quartus IP     |                                  | 145  |

| Appendix I Design Compil  | er Synthesis IP                  | 186  |

| Appendix J Design Compil  | er Constraint                    | 196  |

| Appendix K MATLAB Co      | de                               | 197  |

### **CHAPTER 1**

### **INTRODUCTION**

### 1.1 Introduction

The computer vision field has been rapidly developing and has become an essential part of our modern life. Computer vision technology has been deployed in various areas such as personal gadgets, industrial, automotive, agriculture, including public health and medical applications. Computer vision enables computer to model and imitate the human visual through computer software and hardware at different levels by extracting and interpreting all the information from the images or videos during image processing stages. With all the information extraction, computer will be able to perform object classification and identification, including object tracking, panorama stitching and decision making [1], [2]. Figure 1.1 shows the image stitching in computer vision using corner detector. Image stitching is the process of concatenating multiple images of the same scene to generate a panoramic image without overlapping. During the stitching process, matching corner pairs are determined, and a similarity matrix for each corner is calculated to determine the positions of similar corners for image merging [2].

Figure 1.1 Image stitching using corner detection [2].

Corners are one of the basic features used to describe objects during the feature extraction process in image processing. Edges are the area with intensity changes, while the corners are interesting points formed by the intersection junction of two or more edges in a specific area [3]. Corners are an important feature in computer vision because it is invariant to illumination change, translation or rotation, and image noise. Therefore, a corner is a good feature to retain the essential property of an object and effectively reduce the data processing load during image processing and pattern recognition [4].

Harris corner detector is a common and popular technique used in computer vision to detect corners in an image because of its high informative and good stability properties [5]–[7]. Compared to other corner detector algorithms, it shows good performance and accuracy when distinguishing edge and corner in noisy images. Therefore, the Harris corner detector has become a famous research technique and one of the best corner detection algorithms for high-speed modern computer vision systems such as advanced driver assistance systems (ADAS) and video surveillance applications [8], [9].

The significant increasing demand for high-speed processing for real-time computing applications is a challenging issue in computer vision. There is always a tradeoff between system performance, costs, and design effort. Improving system performance always brings drawbacks in terms of power and area consumption. Therefore, a good architecture design should be able to increase the performance of the system with minimum cost and area increase.

### **1.2 Problem Statement**

The Harris corner detector needs a Gaussian filter to smoothen the image before passing the input pixel of the image to the system to determine the corner. The Gaussian filter calculation will require a constant of kernel matrix, and the filtering process requires a costly MAC unit to perform arithmetic operations. A larger gaussian kernel provides a better smoothing effect but will require more logic and increase processing time and area. In the positional number system (PNS) Harris corner detector, the bit size of binary arithmetic calculation in the Gaussian filter will become very large when using a bigger kernel size. This slows down the system because it requires a larger MAC unit for computation.

- (a) The processing of the Gaussian filter in the Harris Corner Detector is computationally expensive and requires a costly multiplier–accumulator (MAC unit) [10].

- (b) A larger gaussian kernel provides a better smoothing effect but has lower speed and performance, larger area, and higher cost [11], [12].

To solve the computation issue in the Harris corner detector, a more efficient data representation method can be used to replace the number system in the system. Residue number system (RNS) is a data representation system used to represent a number in a collection of smaller numbers and reduce the bit width of the MAC unit when performing the arithmetic operation. Therefore, the computational speed will be improved, and the combinational logic in the MAC unit will be reduced, resulting in a smaller area. The RNS will be studied and implemented in the MAC module. The performance of the Harris corner detector will be verified at the end of the report using PPA (Power, Performance, and Area) analysis.

#### **1.3** Research Goal

The ultimate goal of this project is to improve the computational speed of the Harris corner detector by implementing Residue Number System (RNS). RNS technique will be implemented on the reference model that uses the conventional position number system technique [8].

The objectives of the research are:

- (a) To implement Residue Number System in Harris Corner Detector.

- (b) To design a Residue Number System-based Gaussian Filter.

- To assess, benchmark, and analyze the performance of the Residue Number System-based Harris Corner Detector

### **1.4** Scope of Work

The scopes of work are:

- (a) Input is 256x256 pixels greyscale Lena, Block, and House dataset.

- (b) The input to the system is 8-bits pixel intensity, and the input binary image data is generated using MATLAB.

- (c) RNS moduli set {2<sup>n</sup>-1,2<sup>n</sup>,2<sup>n</sup>+1}, n=9,13 will be used in the modified MAC unit.

- (d) Synthesis the designs using 180nm SilTerra library with fast database in Synopsys Design Compiler.

- (e) Compare the performance of the design in terms of maximum operating frequency, throughput, power consumption, gate count, energy, and area.

- (f) The RNS converters are not considered during the performance comparison because they are not a part of the digital filter [13], and the RNS conversion can be performed using software [14], [15].

#### REFERENCES

- S. Xu, J. Wang, W. Shou, T. Ngo, A. M. Sadick, and X. Wang, "Computer Vision Techniques in Construction: A Critical Review," *Arch. Comput. Methods Eng.*, vol. 28, no. 5, pp. 3383–3397, Oct. 2021.

- I. Hadi Ali and S. Salman, "360-Degree Panoramic Image Stitching for Unordered Images Based on Harris Corner Detection," *Indian J. Sci. Technol.*, vol. 12, no. 4, pp. 1–9, Jan. 2019.

- [3] H. A. Kadhim and W. A. Araheemah, "A method to improve corner detectors (Harris, Shi-Tomasi & FAST) using adaptive contrast enhancement filter," *Period. Eng. Nat. Sci.*, vol. 8, no. 1, 2020.

- [4] A. A. Karim and R. Sameer, "Improvement of Harris Algorithm Based on Gaussian Scale Space," *Eng. Technol. J.*, vol. 37, no. 1B, pp. 1–5, Apr. 2019.

- Y. Han, P. Chen, and T. Meng, "Harris Corner Detection Algorithm at Subpixel Level and Its Application," *Proc. 2015 Int. Conf. Comput. Sci. Eng.*, vol. 17, no. Iccse, pp. 133–137, 2015.

- [6] T. P. Patel and S. R. Panchal, "Corner Detection Techniques : An Introductory Survey," Int. J. Eng. Dev. Res., vol. 2, no. 4, pp. 3680–3686, 2014.

- [7] C. Luo, X. Sun, X. Sun, and J. Song, "Improved Harris Corner Detection Algorithm Based on Canny Edge Detection and Gray Difference Preprocessing," *J. Phys. Conf. Ser.*, vol. 1971, no. 1, 2021.

- [8] M.OMAR AWADH, "Implementation of Harris Corner Detector On FPGA," Universiti Teknologi Malaysia, 2016.

- [9] P. Sikka, A. R. Asati, and C. Shekhar, "Real time FPGA implementation of a high speed and area optimized Harris corner detection algorithm," *Microprocess. Microsyst.*, vol. 80, p. 103514, 2021.

- [10] J. Sánchez, N. Monzón, and A. Salgado, "An analysis and implementation of the harris corner detector," *Image Process. Line*, vol. 8, pp. 305–328, 2018.

- [11] Z. M. Ramadan, "Effect of kernel size on Wiener and Gaussian image filtering," *Telkomnika (Telecommunication Comput. Electron. Control.*, vol. 17, no. 3, pp. 1455–1460, 2019.

- [12] K. K. Delibasis, "Efficient implementation of Gaussian and laplacian kernels

for feature extraction from IP fisheye cameras," *J. Imaging*, vol. 4, no. 6, 2018.

- [13] P. Lyakhov, M. Valueva, G. Valuev, and N. Nagornov, "High-Performance Digital Filtering on Truncated Multiply-Accumulate Units in the Residue Number System," *IEEE Access*, vol. 8, pp. 209181–209190, 2020.

- [14] P. Patronik and S. J. Piestrak, "Hardware/Software Approach to Designing Low-Power RNS-Enhanced Arithmetic Units," *IEEE Trans. Circuits Syst. I Regul. Pap.*, vol. 64, no. 5, pp. 1031–1039, 2017.

- [15] P. Palronik and S. J. Piestrak, "Design of a low-power RNS-enhanced arithmetic unit," LASCAS 2016 - 7th IEEE Lat. Am. Symp. Circuits Syst. R9 IEEE CASS Flagsh. Conf., pp. 151–154, 2016.

- [16] J. Wang and W. Zhang, "A Survey of Corner Detection Methods," vol. 139, no. Iceea, pp. 214–219, 2018.

- [17] T. Luo, Z. Shi, and P. Wang, "Robust and efficient corner detector using noncorners exclusion," *Appl. Sci.*, vol. 10, no. 2, p. 443, Jan. 2020.

- [18] K. U. Pavan, M. P. V. Sahul, and B. T. V. Murthy, "Implementation of stereo visual odometry estimation for ground vehicles," *RTEICT 2017 - 2nd IEEE Int. Conf. Recent Trends Electron. Inf. Commun. Technol. Proc.*, vol. 2018-January, pp. 1173–1177, Jul. 2017.

- [19] J. Loundagin, "Optimizing Harris Corner Detection on GPGPUs Using CUDA," *Master's Theses*, Mar. 2015.

- [20] K. Y. Kok and P. Rajendran, "Validation of Harris Detector and Eigen Features Detector," in *IOP Conference Series: Materials Science and Engineering*, 2018, vol. 370, no. 1.

- [21] S. Ma, S. Hu, Z. Yang, X. Wang, M. Liu, and J. Hu, "High precision multiplier for rns {2n 1, 2n, 2n + 1}," *Electron.*, vol. 10, no. 9, pp. 1–16, 2021.

- [22] N. I. Chervyakov, P. A. Lyakhov, N. N. Nagornov, D. I. Kaplun, A. S.

Voznesenskiy, and D. V. Bogayevskiy, "Implementation of Smoothing Image Filtering in the Residue Number System," 2019 8th Mediterr. Conf. Embed. Comput. MECO 2019 - Proc., no. June, pp. 12–15, 2019.

- [23] M. Selianinau, "Computationally Efficient Approach to Implementation of the Chinese Remainder Theorem Algorithm in Minimally Redundant Residue Number System," *Theory Comput. Syst.*, vol. 65, no. 7, pp. 1117–1140, 2021.

- [24] B. Parhami, "Computer arithmetic : algorithms and hardware designs," p. 641, 2010.

- [25] H. Zhou *et al.*, "A High-Speed Parallel FPGA Implementation of Harris Corner Detection," *Proc. 2020 IEEE Int. Conf. Integr. Circuits, Technol. Appl. ICTA 2020*, pp. 71–72, 2020.

- [26] S. Liu *et al.*, "Real-time implementation of harris corner detection system based on FPGA," 2017 IEEE Int. Conf. Real-Time Comput. Robot. RCAR 2017, vol. 2017-July, pp. 339–343, 2018.

- [27] A. Ben Amara, E. Pissaloux, R. Grisel, and M. Atri, "Zynq FPGA based memory efficient and real-time harris corner detection algorithm implementation," 2018 15th Int. Multi-Conference Syst. Signals Devices, SSD 2018, vol. 2, no. 1, pp. 852–857, 2018.

- [28] G. Jaberipur and H. R. Ahmadifar, "A ROM-less reverse RNS converter for moduli set {2q ± 1, 2q ± 3}," *IET Comput. Digit. Tech.*, vol. 8, no. 1, pp. 11–22, Jan. 2014.

- [29] D. Avinash and R. Sushma, "DESIGN OF HIGH SPEED FLOATING POINT MAC USING RESIDUE NUMBER SYSTEM," 2018 Int. J. Adv. Res. Sci. Technol. IJARST, vol. 07, pp. 1023–1031, 2018.

- [30] R. Dhanabal, V. Barathi, S. K. Sahoo, N. R. Samhitha, N. A. Cherian, and P. M. Jacob, "Implementation of floating point MAC using Residue Number System," *ICROIT 2014 Proc. 2014 Int. Conf. Reliab. Optim. Inf. Technol.*, pp. 461–465, 2014.