# SWITCHED CAPACITOR MULTILEVEL INVERTER USING PWM TECHNIQUE

ABDIRIZAK ABDIHAFID MOHAMED

A thesis submitted in fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical Power)

> School of Electrical Engineering Faculty of Engineering Universiti Teknologi Malaysia

> > JULY 2021

## ACKNOWLEDGEMENT

I would like to thank my supervisor Dr. Shahrin Bin Md. Ayob for his guidance throughout this process, without his support and guidance it would not have been possible to make it until here. Dr. Shahrin was very kind-hearted, was very humble during all this process, and used to give sample time for research and used to correct in many ways so that the research cannot have distracted.

I would like to remember my father who passed away during my first year in this world and my mother in 2002. It was tough to pursue my studies but my beloved uncles Abdullahi and Hassan their blessings kept my nerves to continue although my uncle Abdullahi passed away on 14 July 2007. May Allah bless them all my mother, father and uncle with the highest place in Jannah.

#### ABSTRACT

For the last decades, the increasing demand for renewable energy resources and their applications of high voltage, multilevel inverter (MLI) become very popular and globally recognized for several industrial applications and it has been under research and development with successful industrial applications due to its capacity to produce high levels of voltage output, low THD, low EMI and reduced switching stress on switching devices. However, renewable energy resources such as solar and wind energy for their output are not always fixed due to changes of their input constantly. To boost their output and to convert into alternate current (AC) at the same time with one circuit, switched capacitor inverter is required. In this project, a Switched-Capacitor multilevel inverter with 7-level output comparing between different kinds of pulse width modulation (PWM) technique namely, phase disposition (PD-SPWM), phase opposition disposition (POD-SPWM), and Alternate phase opposition disposition (APOD-SPWM) has been proposed. The main objectives of this project are to simulate the modelled 7-level switched capacitor multilevel inverter using pulse width modulation technique with different modulation index, to observe the performance of the switching patterns of various switches, output voltage, and FFT analysis of modified multilevel inverter, to perform analysis of the charging and discharging time of the capacitors and to analyze using PD-SPWM for pure resistive load and RL load and step change of load from no load to RL load and from low RL load to high RL load. The proposed topology uses a smaller number of switches and produces less harmonic output voltage using the strategy of pulse width modulation (PWM). To validate the viability of the proposed topography and its strategy of switching, a circuit for seven-level MLI is developed and done in MATLAB/SIMULINK software tool.

#### ABSTRAK

Selama beberapa dekad yang lalu, permintaan yang semakin meningkat untuk sumber tenaga yang boleh diperbaharui dan penggunaan voltan tinggi, penyongsang pelbagai tahap (MLI) menjadi sangat popular dan diiktiraf di seluruh dunia untuk beberapa aplikasi industri dan telah diteliti dan dikembangkan dengan aplikasi industri yang berjaya kerana kapasitinya untuk menghasilkan output voltan tahap tinggi, THD rendah, EMI rendah dan tekanan tegangan pengurangan pada peranti beralih. Walau bagaimanapun, sumber tenaga boleh diperbaharui seperti tenaga suria dan angin untuk outputnya tidak selalu diperbaiki kerana perubahan input mereka sentiasa. Untuk meningkatkan output mereka dan menukar menjadi arus bolak balik (AC) pada satu masa dengan satu litar, diperlukan penyongsang kapasitor yang diubah. Dalam projek ini, penyongsang bertingkat Kapasitor Beralih dengan output 7 tingkat yang membandingkan antara pelbagai jenis teknik modulasi lebar denyut (PWM) iaitu, disposisi fasa (PD-SPWM), disposisi penentangan fasa (POD-SPWM), dan penentangan fasa Alternatif pelupusan (APOD-SPWM) telah dicadangkan. Objektif utama projek ini adalah untuk mensimulasikan inverter bertingkat bertingkat kapasitor 7 tingkat yang dimodelkan menggunakan teknik modulasi lebar nadi dengan indeks modulasi yang berbeza, untuk memerhatikan prestasi corak pensuisan pelbagai suis, voltan keluaran, dan analisis FFT penyongsang bertingkat bertingkat, untuk melakukan analisis masa pengisian dan pemuatan kapasitor dan untuk menganalisis menggunakan PD-SPWM untuk beban resistif murni dan beban RL dan perubahan langkah dari beban tanpa beban ke beban RL dan dari beban RL rendah ke beban RL tinggi. Topologi yang dicadangkan menggunakan bilangan suis yang lebih sedikit dan menghasilkan voltan keluaran yang kurang harmonik menggunakan strategi modulasi lebar nadi (PWM). Untuk mengesahkan daya maju topografi yang dicadangkan dan strategi penukarannya, rangkaian untuk MLI tujuh peringkat dikembangkan dan dilakukan dalam alat perisian MATLAB / SIMULINK.

# TABLE OF CONTENTS

# TITLE

| ]       | DECLARATION     |         |                                                           | iii  |

|---------|-----------------|---------|-----------------------------------------------------------|------|

| ]       | DEDICATION      |         |                                                           |      |

|         | ACKNOWLEDGEMENT |         |                                                           |      |

|         | ABSTRACT        |         |                                                           | vi   |

|         | ABST            | RAK     |                                                           | vii  |

| ,       | TABL            | E OF (  | CONTENTS                                                  | viii |

| ]       | LIST            | OF TA   | BLES                                                      | xi   |

| ]       | LIST            | OF FIG  | GURES                                                     | xii  |

| ]       | LIST            | OF AB   | BREVIATIONS                                               | XV   |

| CHAPTER | 1               | INTR    | ODUCTION                                                  | 1    |

|         | 1.1             | Proble  | m Background                                              | 1    |

|         | 1.2             | Multile | evel Inverter classification                              | 3    |

|         | 1.3             | Proble  | m Statement                                               | 3    |

|         | 1.4             | Object  | ives                                                      | 4    |

|         | 1.5             | Scope   | of work                                                   | 4    |

|         | 1.6             | Thesis  | organization                                              | 5    |

| CHAPTER | 2               | LITEI   | RATURE REVIEW                                             | 7    |

|         | 2.1             | Diode   | Clamped MLI                                               | 7    |

|         |                 | 2.1.1   | Operation of Diode Clamped MLI                            | 8    |

|         |                 | 2.1.2   | Applications of DCMLI                                     | 11   |

|         |                 | 2.1.3   | Merits and demerits of DCLMI                              | 11   |

|         |                 | 2.1.4   | Pulse Width Modulation Technique for Diode<br>Clamped MLI | 11   |

|         |                 | 2.1.5   | Features of DCMLI                                         | 15   |

| ,       | 2.2             | Flying  | Capacitor Multilevel Inverter                             | 16   |

|         |                 | 2.2.1   | Operation of flying capacitor MLI                         | 17   |

|           | 2.2.2 Applications of FCMLI                                        | 18 |

|-----------|--------------------------------------------------------------------|----|

|           | 2.2.3 Merits and Demerits of FCMLI                                 | 19 |

|           | 2.2.4 Pulse Width Modulation Technique for Flying<br>Capacitor MLI | 19 |

|           | 2.2.5 Features of Flying Capacitor MLI                             | 22 |

| 2.3       | Cascaded multilevel inverter                                       | 23 |

|           | 2.3.1 Operation of cascaded MLI                                    | 23 |

|           | 2.3.2 Applications of cascaded MLI                                 | 26 |

|           | 2.3.3 Pulse width modulation strategy for CMLI                     | 26 |

|           | 2.3.4 Merits and Demerits of CMLI                                  | 29 |

| 2.4       | Switched Capacitor MLI                                             | 29 |

|           | 2.4.1 Operation of Switched-Capacitor MLI                          | 30 |

| CHAPTER 3 | <b>RESEARCH METHODOLOGY</b>                                        | 33 |

| 3.1       | Methodology flow chart                                             | 33 |

| 3.2       | Overview                                                           | 34 |

| 3.3       | Multi Carrier-Based Level Shifted PWM                              | 35 |

|           | 3.3.1 Phase disposition (PD)                                       | 35 |

|           | 3.3.2 Phase opposition disposition (POD)                           | 36 |

|           | 3.3.3 Alternate Phase Opposition Disposition (APOD)                | 36 |

| 3.4       | Proposed Switched-Capacitor MLI                                    | 37 |

| 3.5       | Modes of Operation                                                 | 37 |

| 3.6       | Switching Control Scheme                                           | 39 |

| 3.7       | Capacitor Design                                                   | 41 |

| CHAPTER 4 | PROPOSED WORK                                                      | 43 |

| 4.1       | Overview                                                           | 43 |

| 4.2       | Simulation and Result                                              | 43 |

|           | 4.2.1 Boost-up Conversion                                          | 44 |

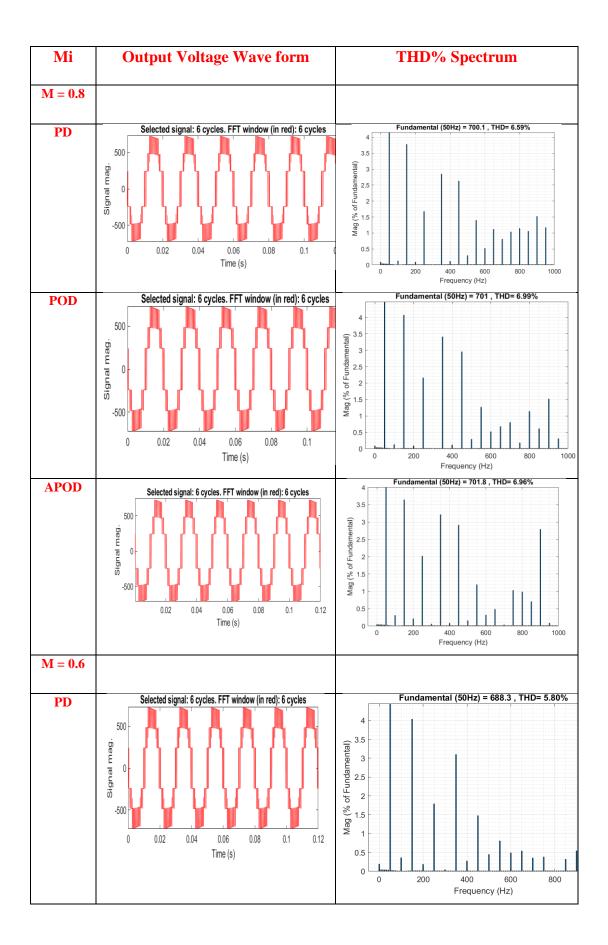

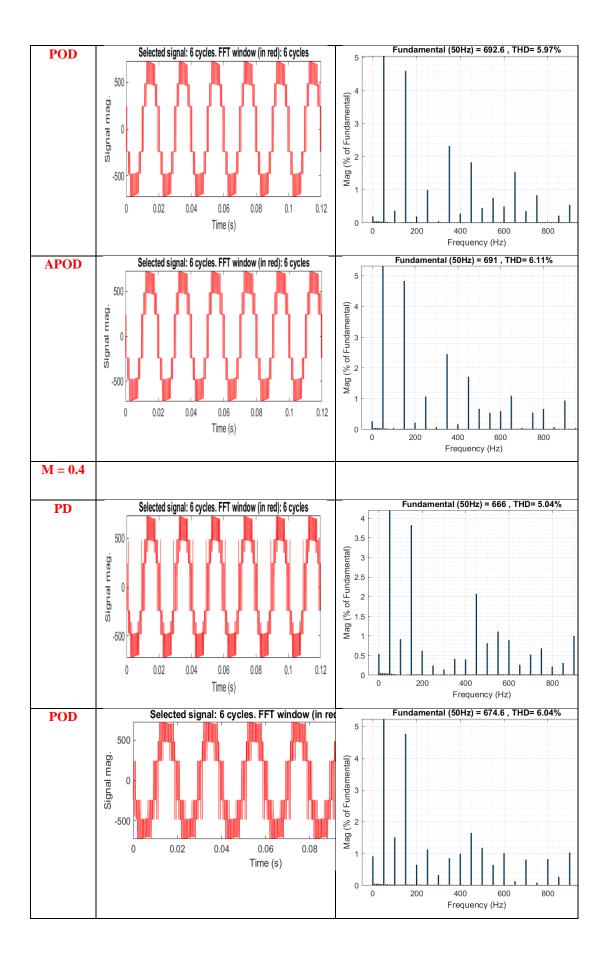

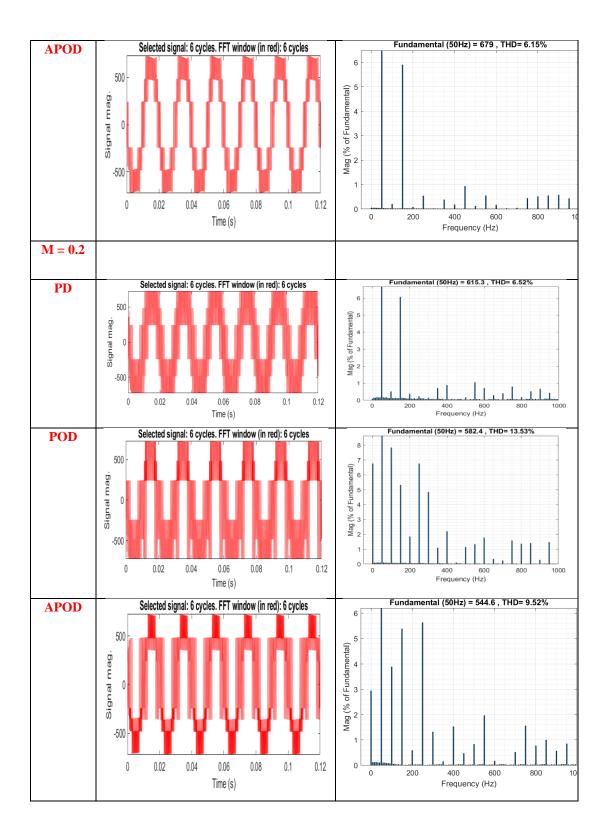

| 4.3       | Comparison of Multi-Carrier SPWM Methods                           | 45 |

| 4.4       | PD-SPWM with R and RL Loads                                        | 52 |

|           | 4.4.1 Pure Resistive Load                                          | 53 |

|           | 4.4.2 Resistive and Inductive Load                                 | 55 |

| APPENDIX  |                                   | lxv |

|-----------|-----------------------------------|-----|

| REFERENCE | ES                                | lxi |

| 5.2       | Recommendations for Future Work   | 59  |

| 5.1       | Conclusion                        | 59  |

| CHAPTER 5 | CONCLUSION                        | 59  |

|           | 4.5.2 Low RL load to High RL load | 57  |

|           | 4.5.1 No-load to low RL load      | 56  |

| 4.5       | Step Load Changes                 | 56  |

# LIST OF TABLES

| TABLE NO. | TITLE                                                  | PAGE |

|-----------|--------------------------------------------------------|------|

| Table 2.1 | Five level DCMLI switching patterns                    | 8    |

| Table 2.2 | One leg switching states                               | 10   |

| Table 2.3 | Simulation Parameters                                  | 13   |

| Table 2.4 | Three levels FCMLI output voltage and switching states | 17   |

| Table 2.5 | Percentage of THD for different modulation indices     | 20   |

| Table 2.6 | Output voltage levels of symmetrical five-level CMLI   | 24   |

| Table 2.7 | Output voltage levels of asymmetrical seven level CMLI | 25   |

| Table 2.8 | Output voltage levels and THD for PWM techniques       | 28   |

| Table 2.9 | Switching States of eleven level SCMLI                 | 31   |

| Table 4.1 | Simulation Parameters                                  | 43   |

| Table 4.2 | Modulation Parameters                                  | 46   |

| Table 4.3 | Fundamental voltage and THD for PD-SPWM                | 51   |

| Table 4.4 | Comparison between multicarrier SPWM                   | 52   |

# LIST OF FIGURES

| FIGURE NO   | D. TITLE                                                     | PAGE |

|-------------|--------------------------------------------------------------|------|

| Figure 1.1  | Current Source inverter                                      | 2    |

| Figure 1.2  | Voltage Source inverter                                      | 2    |

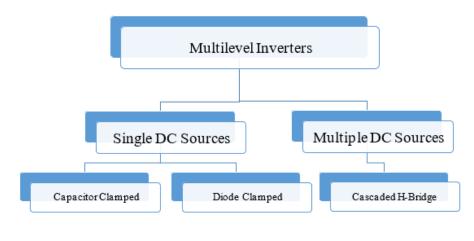

| Figure 1.3  | Multilevel Inverter classification                           | 3    |

| Figure 2.1  | DCMLI five level                                             | 8    |

| Figure 2.2  | Five level Voltage Output DCMLI                              | 9    |

| Figure 2.3  | Three phase DCMLI five Level                                 | 10   |

| Figure 2.4  | Three-level DCMLI                                            | 12   |

| Figure 2.5  | Sinusoidal Reference Signal                                  | 13   |

| Figure 2.6  | Trapezoidal Reference Signal                                 | 13   |

| Figure 2.7  | Third Harmonic Injection Reference Signal                    | 13   |

| Figure 2.8  | Zero Sequence Injection Reference Signal                     | 13   |

| Figure 2.9  | Output Voltage for SRS                                       | 14   |

| Figure 2.10 | Output Voltage for TRS                                       | 14   |

| Figure 2.11 | Output Voltage for ZSIRS                                     | 15   |

| Figure 2.12 | Three level FCMLI                                            | 17   |

| Figure 2.13 | One-leg Five-Level Flying Capacitor MLI                      | 20   |

| Figure 2.14 | <i>Vo</i> waveform for APOD technique and FFT at $(m = 0.9)$ | 21   |

| Figure 2.15 | <i>Vo</i> waveform for PD strategy and FFT at $(m = 0.9)$    | 22   |

| Figure 2.16 | <i>Vo</i> waveform for POD method and FFT at $(m = 0.9)$     | 22   |

| Figure 2.17 | Five-level CHB MLI                                           | 23   |

| Figure 2.18 | Five level CMLI a) output voltage                            | 27   |

| Figure 2.19 | Five level CMLI b) FFT analysis                              | 27   |

| Figure 2.20 | Seven level CMLI a) output voltage                           | 27   |

| Figure 2.21 | Seven level CMLI b) FFT analysis                             | 27   |

| Figure 2.22 | Nine level CMLI a) output voltage                            | 27   |

| Figure 2.23 | Nine level CMLI b) FFT analysis                    | 27 |

|-------------|----------------------------------------------------|----|

| Figure 2.24 | Eleven level CMLI a) output voltage                | 28 |

| Figure 2.25 | Eleven level CMLI b) FFT analysis                  | 28 |

| Figure 2.26 | Thirteen level CMLI a) output voltage              | 28 |

| Figure 2.27 | Thirteen level CMLI b) FFT analysis                | 28 |

| Figure 2.28 | Eleven Level SCMLI                                 | 31 |

| Figure 3.1  | Research methodology flow chart                    | 33 |

| Figure 3.2  | Multilevel inverter modulation classification [38] | 34 |

| Figure 3.3  | Phase Disposition PWM                              | 35 |

| Figure 3.4  | Phase Opposition Disposition PWM                   | 36 |

| Figure 3.5  | Alternate Phase Opposition Disposition             | 36 |

| Figure 3.6  | Proposed Switched-Capacitor MLI                    | 37 |

| Figure 3.7  | Zero Voltage                                       | 39 |

| Figure 3.8  | Vo = Vdc                                           | 39 |

| Figure 3.9  | Vo = 2Vdc                                          | 39 |

| Figure 3.10 | Vo = 3Vdc                                          | 39 |

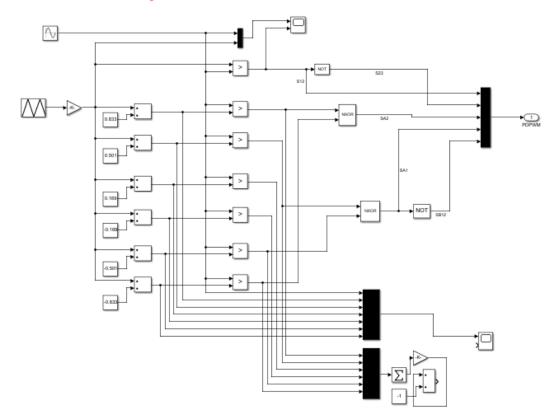

| Figure 3.11 | Model of PD-SPWM Matlab/Simulink                   | 40 |

| Figure 3.12 | Seven Level SCMLI PD-SPWM Modulation               | 40 |

| Figure 3.13 | Seven Level SCMLI PD-SPWM Switching Method         | 40 |

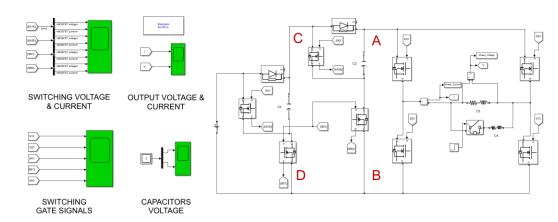

| Figure 4.1  | Simulink model of seven-level SCMLI                | 44 |

| Figure 4.2  | Output Voltage and Current                         | 44 |

| Figure 4.3  | Obtained boost up voltage to 490V                  | 45 |

| Figure 4.4  | Obtained boost up the voltage to 750V              | 45 |

| Figure 4.5  | Model of PD-SPWM block diagram Matlab/Simulink     | 46 |

| Figure 4.6  | Switching patterns obtained for all switches       | 47 |

| Figure 4.7  | Phase Disposition PWM diagram at Mi= 0.8           | 48 |

| Figure 4.8  | Output Voltage                                     | 48 |

| Figure 4.9  | Harmonic Spectrum                                  | 48 |

| Figure 4.10 | Phase Disposition PWM diagram at Mi= 0.6           | 49 |

| Figure 4.11 | Output Voltage                           | 49 |

|-------------|------------------------------------------|----|

| Figure 4.12 | Harmonic Spectrum                        | 49 |

| Figure 4.13 | Phase Disposition PWM diagram at Mi= 0.4 | 49 |

| Figure 4.14 | Output Voltage                           | 50 |

| Figure 4.15 | Harmonic Spectrum                        | 50 |

| Figure 4.16 | Phase Disposition PWM diagram at Mi= 0.2 | 50 |

| Figure 4.17 | Output Voltage                           | 51 |

| Figure 4.18 | Harmonic Spectrum                        | 51 |

| Figure 4.19 | Response with resistive loads            | 53 |

| Figure 4.20 | Switching states of the switches         | 54 |

| Figure 4.21 | Capacitor Voltages                       | 55 |

| Figure 4.22 | Capacitor Voltages                       | 55 |

| Figure 4.23 | PD-SPWM with RL Load                     | 56 |

| Figure 4.24 | Capacitor voltages                       | 56 |

| Figure 4.25 | PD-SPWM THD                              | 56 |

| Figure 4.26 | Voltage response                         | 57 |

| Figure 4.27 | THD no load                              | 57 |

| Figure 4.28 | THD after Step load                      | 57 |

| Figure 4.29 | Capacitor voltages no load               | 57 |

| Figure 4.30 | Voltage and current                      | 58 |

| Figure 4.31 | THD at low RL                            | 58 |

| Figure 4.32 | THD at high RL                           | 58 |

| Figure 4.33 | Capacitor charging                       | 58 |

# LIST OF ABBREVIATIONS

| MLI    | - | Multilevel Inverter                               |

|--------|---|---------------------------------------------------|

| DC     | - | Direct Current                                    |

| AC     | - | Alternate Current                                 |

| VSI    | - | Voltage Source Inverter                           |

| CSI    | - | Current Source Inverter                           |

| EMI    | - | Electromagnetic Interference                      |

| SCMLI  | - | Switched Capacitor Multilevel Inverter            |

| UTM    | - | Universiti Teknologi Malaysia                     |

| PD     | - | Phase Disposition                                 |

| POD    | - | Phase Opposition Disposition                      |

| APOD   | - | Alternate Phase Opposition Disposition            |

| PWM    | - | Pulse Width Modulation                            |

| SPWM   | - | Sinusoidal Pulse Width Modulation                 |

| DCMLI  | - | Diode Clamped Multilevel Inverter                 |

| FCMLI  | - | Flying Capacitor Multilevel Inverter              |

| CMLI   | - | Cascaded Multilevel Inverter                      |

| SRS    | - | Sinusoidal Reference Signal                       |

| TRS    | - | Trapezoidal Reference Signal                      |

| ZSIRS  | - | Zero Sequence Injected Reference Signal           |

| PS     | - | Phase Shift                                       |

| IGBT   | - | Insulated-gate Bipolar Transistor                 |

| GTO    | - | Gate Turn-off Thyristor                           |

| BJT    | - | Bipolar Junction Transistor                       |

| MOSFET | - | Metal Oxide Semiconductor Field-effect Transistor |

| THD    | - | Total Harmonic Distortion                         |

| PV     | - | Photovoltaic                                      |

| PDS    | - | Power distribution Systems                        |

|        |   |                                                   |

#### **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 Problem Background

Multilevel inverter (MLI) topology has played significant interest in renewable energy and power electronics researchers due to its numerous ranges of potentially useful applications and increasing demands of power and efficiency. Many observations have been done in shaping these challenges with continued evolution for the last two decades. The considerations of high dynamic, demanding applications and high power with quality and efficiency of multilevel inverter may become modest clarifications. It is used a wide range of multi-megawatts [1].

Our daily power consumption resources include coal, natural gas, and coal crude oil, one of the most dependable resources for many countries for the last couple of years. Their resources are decreasing day by day with their high consumption. These resources have many environmental problems; for these obstacles, there is a necessary high need for renewable energy resources. Many countries have many potential capabilities of applying renewable energy resources such as solar energy and wind energy. These sources generate direct current (DC) voltage and current for their output. Inverters are required to convert the dc voltages to ac supply.

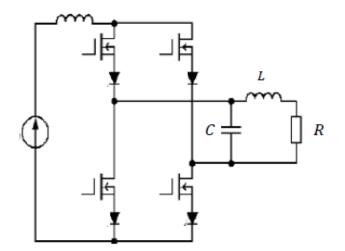

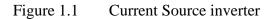

Inverter topology refers to the conversion from direct current input to alternative current output into pair of cycles. Voltage source inverter (VSI) can be called the inverter when the input is a voltage source. Similarly, when the input is a current source, the inverter is called a current source inverter (CSI). In contrast, a multilevel inverter (MLI) is the inverter used to synthesize desired sinusoidal output voltage from several levels of DC source [2-4]. The sources can be derived from batteries, renewable energy systems, etc. Due to the lower rating voltage of power semiconductor devices for high voltage generation, small filter size, Lower EMI, improved performance, reduced content of harmonic, and many more, multilevel inverters have their significance in medium and high voltage applications[5]. Figure 1.1 and Figure 1.2 show typical single-phase CSI and VSC circuit diagrams

Figure 1.2 Voltage Source inverter

## 1.2 Multilevel Inverter classification

Mainly multilevel inverters are classified into three main kinds:

- a. Cascaded H-Bridge (CHB)

- b. Neutral-Point Clamped (NPC)

- c. Flying-Capacitor (FC)

Figure 1.3 Multilevel Inverter classification

### **1.3 Problem Statement**

For the last two decades, with the increasing demand for renewable energy sources and their application in high voltage applications, power electronic converters play a vital role in the suitability of power conversion for each application. Due to the lower rating voltage of power semiconductor devices for high voltage generation, small filter size, Lower EMI, improved performance, reduced content of harmonic, and many more, multilevel inverters have their significance in medium and high voltage applications [5]. The basic principle of MLIs is to generate a staircase voltage waveform near sinusoidal with high power quality. The desired staircase voltage waveform is synthesized using the appropriate combination of different switches, which can reduce the voltage stress of power switches and total harmonic distortion (THD)[6, 7].[8]

The output of some renewable energy resources such as solar and wind energy are not always fixed due to change in their input continuously. For solar energy, the output voltage varies with the temperature and irradiance, while wind energy output voltage varies with the speed of the wind. Hence, there will be a possibility of the output voltage is lower than the utility grid. The conventional multilevel inverter is not able to deal with these problems.

To boost their output and convert into alternate current (AC) simultaneously with one circuit, switched capacitor inverter is required. In this project, a Switched-Capacitor multilevel inverter with 7-level output has been proposed to overcome the aforementioned issues.

## 1.4 Objectives

The objectives of this study are:

- a. To simulate the modelled 7-level switched multilevel capacitor inverter using pulse width modulation technique

- b. To observe the performance of the switching patterns of various switches, output voltage, and FFT analysis, to analyze the circuit by using PD-SPWM for both steady-state and transient state of load with capacitor design for seven-level SCMLI.

## 1.5 Scope of work

The research scopes of this project can be described as below;

- a. The focus of this thesis project is about seven-level MLI topology.

- b. The modulation strategy that will be used as switching techniques are phase disposition pulse width modulation technique (PD-SPWM),

phase opposition disposition pulse width modulation strategy (POD-SPWM), alternate phase opposition disposition pulse width modulation strategy (APOD-SPWM)

c. The model will be simulated using MATLAB/SIMULINK software.

## **1.6** Thesis organization

This thesis consists of five chapters that are listed below: -

**Chapter 1** presents the fundamental basics of MLI and highlights the reputation of using switched capacitor multilevel inverter.

**Chapter 2** discusses the overall view of different multilevel inverter topologies, including merits and demerits. It also presents the discussion of using different pulse width modulation techniques and their total harmonic distortion spectrum.

**Chapter 3** focuses on the proposed seven-level switched capacitor multilevel inverter with a thorough, detailed explanation of the principle mode of operation of the proposed circuit and the design of the capacitors. It also provides a detailed concept of level-shifted pulse width modulation techniques that will implement during this thesis project.

**Chapter 4** gives the simulation results, which describe the validation of the proposed switched capacitor MLI and the results are analyzed accordingly.

**Chapter 5** concludes the thesis with statements that answers the objectives of the research.

#### REFERENCES

- Suvetha Poyyamani Sunddararaj, S.S.R., Subashini N, An Extensive Review of Multilevel Inverters Based on Their Multifaceted Structural Configuration, Triggering Methods and Applications.

- Suresh, R.A.K.a.L.P., A brief review on multi level inverter topologies. International Conference on Circuit, Power and Computing Technologies (ICCPCT), 2016.

- S.Ravivarman, M.R.a., *Review on Voltage Balancing Solutions in Multilevel Inverters.* Indonesian journal of electrical engineering and computer science, 2016. vol.1,No: p. 53-59.

- 4. S.Shalini, *Voltage Balancing in Diode Clamped Multilevel*. International Journal of Engineering Trends and Technology (IJETT), 2013. **volume 6,No2**.

- Siddique, M.D., et al., A New Single Phase Single Switched-Capacitor Based Nine-Level Boost Inverter Topology With Reduced Switch Count and Voltage Stress. IEEE Access, 2019. 7: p. 174178-174188.

- Rodriguez, J., L. Jih-Sheng, and P. Fang Zheng, *Multilevel inverters: a survey* of topologies, controls, and applications. IEEE Transactions on Industrial Electronics, 2002. 49(4): p. 724-738.

- Gupta, K.K., et al., Multilevel Inverter Topologies With Reduced Device Count: A Review. IEEE Transactions on Power Electronics, 2016. 31(1): p. 135-151.

- Axelrod, B., Y. Berkovich, and A. Ioinovici, A cascade boost-switchedcapacitor-converter - two level inverter with an optimized multilevel output waveform. IEEE Transactions on Circuits and Systems I: Regular Papers, 2005. 52(12): p. 2763-2770.

- Nabae, A., I. Takahashi, and H. Akagi, A New Neutral-Point-Clamped PWM Inverter. IEEE Transactions on Industry Applications, 1981. IA-17(5): p. 518-523.

- 10. Riya G. Barapatre1, S.Y.T., Samir D.Landge1, Shubhendu B.Mukherji1, Design and Implementation of Five Level Diode Clamped Inverter.

International Journal of Innovations in Engineering and Science, 2019. Vol. 4, No.7(Impact Factor Value 4.046).

- Kumar, R., R.A. Gupta, and K.S. Pratap. Implementation and Analysis of Five-Level inverter with Space Vector PWM Algorithm. in 2006 IEEE International Conference on Industrial Technology. 2006.

- 12. Bin, W. and N. Mehdi, *Voltage Source Inverter Fed Drives*, in *High-Power Converters and AC Drives*. 2017, IEEE. p. 287-308.

- Tolbert, L.M., P. Fang Zheng, and T.G. Habetler, *Multilevel converters for large electric drives*. IEEE Transactions on Industry Applications, 1999. 35(1): p. 36-44.

- 14. Siddique, M.D. and A. Sarwar. *Performance analysis of carrier based PWM technique for three level diode clamped multilevel inverter with different reference signals.* in 2016 IEEE 7th Power India International Conference (PIICON). 2016.

- Meynard, T.A., et al., *Multicell converters: basic concepts and industry applications*. IEEE Transactions on Industrial Electronics, 2002. 49(5): p. 955-964.

- Chang-xin, M., et al., *Flying capacitor multilevel inverters with novel PWM method.* Procedia Earth and Planetary Science, 2009. 1(1): p. 1554-1560.

- Escalante, M.F., J. Vannier, and A. Arzande, *Flying capacitor multilevel* inverters and DTC motor drive applications. IEEE Transactions on Industrial Electronics, 2002. 49(4): p. 809-815.

- Koshti, A.K. and M.N. Rao. A brief review on multilevel inverter topologies. in 2017 International Conference on Data Management, Analytics and Innovation (ICDMAI). 2017.

- Xiaoming, Y., H. Stemmler, and I. Barbi, Self-balancing of the clampingcapacitor-voltages in the multilevel capacitor-clamping-inverter under subharmonic PWM modulation. IEEE Transactions on Power Electronics, 2001. 16(2): p. 256-263.

- 20. Manjrekar, M.D. and T.A. Lipo. *A hybrid multilevel inverter topology for drive applications.* in *APEC '98 Thirteenth Annual Applied Power Electronics Conference and Exposition.* 1998.

- 21. Taleb, R., et al. A comparative analysis of multicarrier SPWM strategies for five-level flying capacitor inverter. in 2016 8th International Conference on Modelling, Identification and Control (ICMIC). 2016.

- 22. Ranjan, A.K., D.V. Bhaskar, and N. Parida. Analysis and simulation of cascaded H-bridge multi level inverter using level-shift PWM technique. in 2015 International Conference on Circuits, Power and Computing Technologies [ICCPCT-2015]. 2015.

- 23. Rashid, M.H., *Power electronics: circuits, devices and applications.*

- Dixon, J., et al., High-Power Machine Drive, Using Nonredundant 27-Level Inverters and Active Front End Rectifiers. IEEE Transactions on Power Electronics, 2007. 22(6): p. 2527-2533.

- Liu, Y., et al., Small-Signal Model-Based Control Strategy for Balancing Individual DC Capacitor Voltages in Cascade Multilevel Inverter-Based STATCOM. IEEE Transactions on Industrial Electronics, 2009. 56(6): p. 2259-2269.

- Jain, K.K.G.a.S., *Topology for multilevel inverters to attain maximum number of levels from given DC sources*. IET Power Electron, 2012. Vol. 5(Iss.4): p. pp. 435–446.

- 27. Glinka, M. Prototype of multiphase modular-multilevel-converter with 2 MW power rating and 17-level-output-voltage. in 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551). 2004.

- Barrena, J.A., et al., *Individual Voltage Balancing Strategy for PWM Cascaded H-Bridge Converter-Based STATCOM*. IEEE Transactions on Industrial Electronics, 2008. 55(1): p. 21-29.

- 29. Tsunoda, A., Y. Hinago, and H. Koizumi. A grid connected inverter with switched capacitor inverter using series/parallel conversion. in 2012 15th International Power Electronics and Motion Control Conference (EPE/PEMC). 2012.

- Hinago, Y. and H. Koizumi, A Switched-Capacitor Inverter Using Series/Parallel Conversion With Inductive Load. IEEE Transactions on Industrial Electronics, 2012. 59(2): p. 878-887.

- 31. Kanimozhi, M. and P. Geetha. A new boost switched capacitor multilevel inverter using different multi carrier PWM techniques. in 2014 International

*Conference on Circuits, Power and Computing Technologies [ICCPCT-2014].* 2014.

- 32. Raman, S.R., K.W.E. Cheng, and J. Hu. A seven level switched capacitor multilevel inverter with asymmetric input sources for microgrids. in 2017 20th International Conference on Electrical Machines and Systems (ICEMS). 2017.

- Liu, J., K.W.E. Cheng, and Y. Ye, A Cascaded Multilevel Inverter Based on Switched-Capacitor for High-Frequency AC Power Distribution System. IEEE Transactions on Power Electronics, 2014. 29(8): p. 4219-4230.

- 34. Raman, S.R., Y. Ye, and K.W.E. Cheng. Switched-capacitor multilevel inverters for high frequency AC microgrids. in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC). 2017.

- Ye, Y., et al., A Step-Up Switched-Capacitor Multilevel Inverter With Self-Voltage Balancing. IEEE Transactions on Industrial Electronics, 2014. 61(12): p. 6672-6680.

- Jain, P., et al., A Review of High-Frequency Power Distribution Systems: For Space, Telecommunication, and Computer Applications. IEEE Transactions on Power Electronics, 2014. 29(8): p. 3852-3863.

- 37. Kishore, P.M. and R. Bhimasingu. A split source boost switched capacitor multilevel inverter for low power applications. in 2017 National Power Electronics Conference (NPEC). 2017.

- Mohan D., K.S.B., A Comparative Analysis of Multi Carrier SPWM Control Strategies using Fifteen Level Cascaded H- Bridge Multilevel Inverter. International Journal of Computer Applications (0975-8887), March 2012. 41,No.21.

- 39. Bhagyalakshmi, P.S., B.M. Varghese, and B.M. Jos. Switched capacitor multilevel inverter with different modulation techniques. in 2017 International Conference on Innovations in Information, Embedded and Communication Systems (ICHECS). 2017.

# APPENDIX

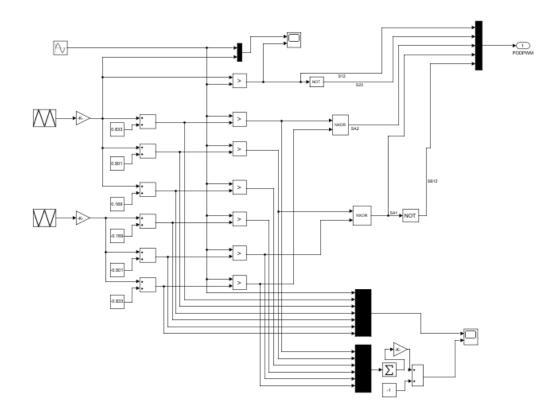

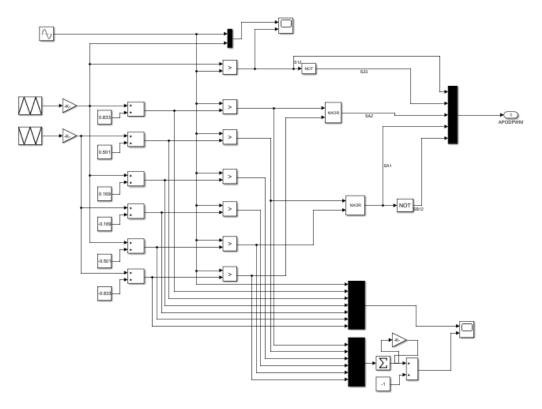

# Modelled diagram of 7 level Switched Capacitor MLI MATLAB/SIMULINK

# PD-SPWM model diagram MATLAB/SIMULINK

## PD-SPWM model diagram MATLAB/SIMULINK