## OPTIMIZATION OF PROCESS PARAMETERS FOR LOWER LEAKAGE CURRENT IN 10 NM FINFET USING TAGUCHI METHOD

LOY YING TING

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Computer & Microelectronic Systems)

> School of Electrical Engineering Faculty of Engineering Universiti Teknologi Malaysia

### **DEDICATION**

This project report is dedicated to my father, who taught me that the best kind of knowledge to have is that which is learned for its own sake. It is also dedicated to my mother, who taught me that even the largest task can be accomplished if it is done one step at a time.

#### ACKNOWLEDGEMENT

I would like to thank to God for giving me the strength, patience and ability to go through all the trials and challenges to complete this final year project successfully. This project would not have been possible without the support of many people. No one walks alone on the journey of life. I would like to take this opportunity to express my gratitude to the people who have been instrumental in the successful completion of this project.

First and foremost, I would like to express my sincere appreciation to my supervisor, Dr Zaharah binti Johari for giving me this golden opportunity on doing and completing this project with all her guidance and knowledge. This project would have never been accomplished without her constant assistance and dedicated involvement. Thank you very much for her enthusiasm and understanding during these two semesters.

Apart from that, I would like to show my biggest gratitude to my beloved family for their unconditional support and encouragement throughout this process. Their love and moral support are the main factors that make me keep going on. Next, I would like to forward my thanks to the faculty; School of Computer and Microelectronic Engineering of Universiti Teknologi Malaysia (UTM), that gave me chance, opportunities and support to gain knowledge in this field.

Furthermore, I would like to highlight my appreciation to my friends, Goh Chien Nam and Muhammad Faidzal Bin Mohamad Rasol, who inspired, encouraged and fully supported me in every trial that came to my way. They had given me constructive and valuable advices throughout the accomplishment of this project.

Once again, thank you very much for their endless support and motivation throughout this project.

#### ABSTRACT

The scaling of conventional transistor according to Moore's Law is predicted to reach its limitation in the future. The conventional transistor using silicon material particularly at nanoscale channel has experienced the short channel effect (SCE), which leads to increase in the leakage current. Therefore, alternative device structure and advanced material are needed to overcome the SCE and reduce the leakage current (ILEAK) with regards to the transistor performance. In this project, a method to control the leakage current in ultranarrow 10 nm FinFET using High-K dielectric material is proposed. The device's fabrication and electrical characterization are then executed using TCAD Sentaurus from Synopsys. Optimization of the process parameters using L9 Taguchi method and finally prediction of the best combination of process parameters in order to obtain the minimum leakage current (ILEAK) in the 10 nm FinFET. There are four process parameters were varied, which are the fins dimension (fin height and width), channel concentration and oxide thickness. Smaller-the-Better (STB) Signal - to -noise ratio (SNR) and the Analysis of Variance (ANOVA) is used to study the performance characteristic and finally obtain the best combination of process parameters in order for the device to perform at its best performance, that will later benchmarked with predicted data from International Technology Roadmap for Semiconductors (ITRS) and previous published results. The optimization is expected to result in the attainment of the lower leakage current value in order to increase the speed performance of the device.

#### ABSTRAK

Pengukuran transistor konvensional mengikut Undang-undang Moore diramalkan akan mencapai batasannya pada masa akan datang. Transistor konvensional menggunakan bahan silikon terutamanya pada saluran nanoscale telah mengalami kesan saluran pendek, yang menyebabkan kebocoran arus meningkat. Oleh itu, struktur peranti alternatif dan bahan canggih diperlukan untuk mengatasi kesan saluran pendek dan mengurangkan kebocoran arus. Dalam projek ini, kaedah untuk mengawal kebocoran arus elektrik dalam 10 nm FinFET ialah menggunakan bahan High-K dielektrik. Fabrikasi dan pencirian elektrik telah dijalankan menggunakan TCAD Sentaurus dari Synopsys. Kaedah L9 Taguchi digunakan untuk mengoptimumkan parameter proses dan akhirnya meramalkan kombinasi parameter proses yang terbaik untuk mendapatkan kebocoran arus yang paling minimum dalam FinFET 10 nm. Empat parameter proses yang diubah, iaitu dimensi sirip (kelebaran dan ketinggian), kepekatan saluran dan ketebalan oksida. Smaller-the-Better (STB) Signal - to -noise ratio (SNR) dan Analysis of Variance (ANOVA) digunakan untuk mengkaji ciri prestasi dan akhirnya meramalkan gabungan parameter proses terbaik untuk mendapatkan prestasi terbaik peranti yang akan kemudian ditandai dengan data yang diramalkan dari Peta Jalan Teknologi Antarabangsa untuk Semikonduktor dan juga karya terbitan sebelumnya. Pengoptimuman dijangka akan menghasilkan pencapaian nilai kebocoran arus yang rendah untuk meningkatkan prestasi kelajuan peranti.

### TABLE OF CONTENTS

### TITLE

PAGE

| DECI                        | LARATION                               | iii  |

|-----------------------------|----------------------------------------|------|

| DEDI                        | ICATION                                | iv   |

| ACK                         | NOWLEDGEMENT                           | V    |

| ABST                        | TRACT                                  | vi   |

| ABST                        | ſRAK                                   | vii  |

| TABI                        | LE OF CONTENTS                         | viii |

| LIST                        | OF TABLES                              | xi   |

| LIST                        | OF FIGURES                             | xii  |

| LIST                        | OF ABBREVIATIONS                       | xiv  |

| LIST                        | OF SYMBOLS                             | XV   |

| LIST                        | OF APPENDICES                          | xvi  |

|                             |                                        |      |

| CHAPTER 1                   | INTRODUCTION                           | 1    |

| 1.1                         | Problem Background                     | 1    |

| 1.2                         | Problem Statement                      | 3    |

| 1.3                         | Objectives                             | 4    |

| 1.4                         | Project Scope                          | 4    |

| 1.5                         | Chapter Organization                   | 5    |

| CHAPTER 2 LITERATURE REVIEW |                                        | 7    |

| 2.1                         | Chapter Overview                       | 7    |

| 2.2                         | Problem Background                     | 7    |

|                             | 2.2.1 Scaling of CMOS                  | 8    |

|                             | 2.2.2 Short Channel Effects            | 9    |

|                             | 2.2.3 High Leakage Current             | 10   |

|                             | 2.2.4 High-K Gate Dielectric Materials | 10   |

|           |        | 2.2.4.1                | High-K Materials Characteristics                                                                   | 11 |

|-----------|--------|------------------------|----------------------------------------------------------------------------------------------------|----|

|           |        | 2.2.4.2                | Review on Performance Analysis on<br>Various Types of High-K Materials                             | 12 |

| 2.3       | Review | w of FinF              | ET                                                                                                 | 14 |

|           | 2.3.1  | Fabricat               | ion of FinFET                                                                                      | 15 |

|           | 2.3.2  | Technol                | ogy Nodes of FinFETs                                                                               | 16 |

| 2.4       | -      | ization of<br>hi Metho | Process Parameters on MOSFET using                                                                 | 21 |

| 2.5       | Chapte | er Summa               | nry                                                                                                | 23 |

| CHAPTER 3 | RESE   | ARCH N                 | 1ETHODOLOGY                                                                                        | 25 |

| 3.1       | Chapte | er Overvi              | ew                                                                                                 | 25 |

| 3.2       | Synop  | sys Senta              | urus TCAD Overview                                                                                 | 25 |

| 3.3       | Projec | t Flow                 |                                                                                                    | 28 |

|           | 3.3.1  | fabricati              | Simulation of the process and device<br>on of the 10 nm FinFET using TCAD<br>is from Synopsys.     | 29 |

|           | 3.3.2  |                        | Process parameter optimization using L9 Method.                                                    | 30 |

|           | 3.3.3  | data usi               | Statistical analysis of the experimental ng signal to noise (SNR) ratio and s of Variance (ANOVA). | 31 |

| 3.4       | 10 nm  | FinFET                 | Design and Device Structure                                                                        | 32 |

|           | 3.4.1  | Fabricat               | ion Simulation                                                                                     | 32 |

| 3.5       | Tools  | and Meth               | ods                                                                                                | 33 |

|           | 3.5.1  | Paramet                | er Diagram                                                                                         | 33 |

|           | 3.5.2  | Taguchi                | L9 Orthogonal Array Method                                                                         | 34 |

|           | 3.5.3  | Signal-te              | o-Noise Ratio Analysis                                                                             | 35 |

|           | 3.5.4  | Analysis               | s of Variance                                                                                      | 35 |

| 3.6       | Device | e Charact              | erization                                                                                          | 35 |

|           | 3.6.1  | Saturatio              | on and Leakage Current                                                                             | 36 |

|           | 3.6.2  | Subthree               | shold Swing                                                                                        | 37 |

|           | 3.6.3  | Thresho                | ld Voltage                                                                                         | 37 |

|           | 3.6.4  | Drain-In               | duced Barrier Lowering                                                                             | 38 |

| 3.7       | Resear | rch Plan               |                                                                                                    | 39 |

| 3.8        | Chapter Summary                                                    | 39 |

|------------|--------------------------------------------------------------------|----|

| CHAPTER 4  | <b>RESULT AND DISCUSSION</b>                                       | 41 |

| 4.1        | Chapter Overview                                                   | 41 |

| 4.2        | 10 nm FinFET with SiO <sub>2</sub> Material                        | 41 |

|            | 4.2.1 Result Validation                                            | 42 |

| 4.3        | 10 nm FinFET with HfO2 Material                                    | 43 |

|            | 4.3.1 Device Simulation Result                                     | 44 |

|            | 4.3.2 Variation of Process Parameters                              | 48 |

|            | 4.3.3 Signal-to-Noise Ratio Analysis for 10 nm n-<br>FinFET Device | 52 |

|            | 4.3.4 Analysis of Variance (ANOVA)                                 | 55 |

| 4.4        | Chapter Summary                                                    | 56 |

| CHAPTER 5  | CONCLUSION AND RECOMMENDATION                                      | 57 |

| 5.1        | Chapter Overview                                                   | 57 |

| 5.2        | Conclusion                                                         | 57 |

| 5.3        | Contribution to Knowledge                                          | 58 |

| 5.4        | Future Works                                                       | 58 |

| REFERENCES |                                                                    | 59 |

**Appendices A-B**

65-66

### LIST OF TABLES

### TITLE

### PAGE

### TABLE NO.

| Table 2.1 | ITRS Trends for MOS Devices                                          | 9  |

|-----------|----------------------------------------------------------------------|----|

| Table 2.2 | Types of High-K Materials Used                                       | 13 |

| Table 2.3 | Summary of 16 nm FinFET Key Technology Features                      | 18 |

| Table 2.4 | Layer Pitches of 14 nm FinFET                                        | 18 |

| Table 2.5 | Example list of FinFET reliability characterization on 10 nm FinFETs | 19 |

| Table 2.6 | Summary of Technology Node of FinFETs                                | 20 |

| Table 2.7 | Use of Taguchi Method for Optimization of Process Parameters         | 22 |

| Table 3.1 | Range of Parameters Used in the Simulation of FinFET                 | 32 |

| Table 4.1 | Process Parameters and their Levels                                  | 49 |

| Table 4.2 | Nine Experiments Suggested by L9 Taguchi Method                      | 50 |

| Table 4.3 | SNR of ILEAK and their Main Effects                                  | 53 |

| Table 4.4 | SNR Response for the I <sub>LEAK</sub>                               | 54 |

| Table 4.5 | ANOVA Result                                                         | 55 |

| Table 4.6 | Best Setting of Process Parameters                                   | 56 |

### LIST OF FIGURES

### TITLE

#### PAGE

### FIGURE NO.

| Figure 1.1  | State-of-art for Intel's Transistors Density                                                                                                 | 1  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1  | Relationship of Band Gap and Relative Dielectric Constants of Various Materials                                                              | 11 |

| Figure 2.2  | Fabrication Process of Silicon-Based FinFET                                                                                                  | 16 |

| Figure 2.3  | (a) TEM Cross-section showing vertical fin sidewall (b)<br>Cross-sectional TEM showing a vertical gate profile from<br>fin-top to fin-bottom | 17 |

| Figure 2.4  | TEMs of Tri-gate NMOS (left) and PMOS (right)<br>Transistors                                                                                 | 17 |

| Figure 2.5  | Illustration of the Input Parameters that Define the FinFET<br>(a) Stressor (b) Geometry (c) Fin Crosssection                                | 19 |

| Figure 3.1  | Tool Flow with Device Simulation using Sentaurus Device                                                                                      | 26 |

| Figure 3.2  | Simulation Tools using Synopsys Sentaurus TCAD                                                                                               | 26 |

| Figure 3.3  | Mesh for TCAD Simulation for n-type FinFET                                                                                                   | 27 |

| Figure 3.4  | Project Implementation Flow                                                                                                                  | 28 |

| Figure 3.5  | Phase 1 Project Flow                                                                                                                         | 29 |

| Figure 3.6  | Phase 2 Project Flow                                                                                                                         | 30 |

| Figure 3.7  | Phase 3 Project Flow                                                                                                                         | 31 |

| Figure 3.8  | Simulated Structure Formation Flow for 10 nm FinFET Design                                                                                   | 33 |

| Figure 3.9  | P-Diagram of the 10 nm FinFET                                                                                                                | 34 |

| Figure 3.10 | INSPECT Tool showing the Electrical Properties                                                                                               | 36 |

| Figure 3.11 | Extraction of $I_{on}$ and $I_{off}$                                                                                                         | 36 |

| Figure 3.12 | Extraction of SS                                                                                                                             | 37 |

| Figure 3.13 | Extraction of V <sub>T</sub>                                                                                                                 | 38 |

| Figure 3.14 | Extraction of DIBL from Drain Current versus Gate Voltage Curve            | 38 |

|-------------|----------------------------------------------------------------------------|----|

| Figure 4.1  | Structural Diagram of the Eight Cuboids of 10 nm n-<br>FinFET              | 42 |

| Figure 4.2  | Comparison of Id-Vg between Simulation and Previous Work                   | 43 |

| Figure 4.3  | 10 nm 2D n-FinFET Simulation Structure (a)Top View (b)<br>Side View        | 44 |

| Figure 4.4  | 10 nm 3D n-FinFET Simulation Structure with $HfO_2$ dielectric layer       | 45 |

| Figure 4.5  | 10 nm 3D n-FinFET Simulation Structure without $HfO_2$ dielectric layer    | 45 |

| Figure 4.6  | Logarithm Graph of $I_d$ - $V_g$ Curve of the n-FinFET Simulation          | 46 |

| Figure 4.7  | Linear Graph of Id-Vg Curve of the n-FinFET Simulation                     | 46 |

| Figure 4.8  | <i>INSPECT</i> Tool to Determine the Electrical Properties Characteristics | 47 |

| Figure 4.9  | Mesh Diagram of the 3D n-FinFET Simulation                                 | 47 |

| Figure 4.10 | Electron Concentration Distribution of the 3D n-FinFET Simulation          | 47 |

| Figure 4.11 | Electric Field Distribution of 3D n-FinFET Simulation                      | 48 |

| Figure 4.12 | Electrostatic Potential Difference of the 3D n-FinFET Simulation           | 48 |

| Figure 4.13 | Id-Vg Curve of The Varied Parameters as Suggested by L9<br>Taguchi Method  | 50 |

| Figure 4.14 | $I_d$ - $V_g$ Graph of Fin Width Dependency                                | 51 |

| Figure 4.15 | $I_d$ - $V_g$ Graph of Fin Height Dependency                               | 51 |

| Figure 4.16 | $I_d$ - $V_g$ Graph of Oxide Thickness Dependency                          | 52 |

| Figure 4.17 | Id-Vg Graph of Channel Doping Dependency                                   | 52 |

| Figure 4.18 | Factor Effect Plot for SNR                                                 | 54 |

### LIST OF ABBREVIATIONS

| TCAD                           | - | Technology Computer-Aided Design                    |

|--------------------------------|---|-----------------------------------------------------|

| MOSFET                         | - | Metal-Oxide Semiconductor Field-Effect Transistor   |

| FinFET                         | - | Fin-Field Effect Transistor                         |

| CMOS                           | - | Complementary Metal Oxide Semiconductor             |

| SCE                            | - | Short Channel Effects                               |

| DIBL                           | - | Drain-Induced Barrier Lowering                      |

| MugFET                         | - | Multigate FinFET                                    |

| SNR                            | - | Signal-to-Noise Ratio                               |

| EOT                            | - | Equivalent Oxide Thickness                          |

| IC                             | - | Integrated Circuit                                  |

| ANOVA                          | - | Analysis of Variance                                |

| ITRS                           | - | International Technology Roadmap for Semiconductors |

| HK/MG                          | - | High-K/Metal Gate                                   |

| S/D                            | - | Source/Drain                                        |

| L9                             | - | Level 9                                             |

| L11                            | - | Level 11                                            |

| DF                             | - | Degree of Freedom                                   |

| SS                             | - | Sum of Squares                                      |

| WF                             | - | Work Function                                       |

| Si                             | - | Silicon                                             |

| SiO <sub>2</sub>               | - | Silicon dioxide                                     |

| HfO <sub>2</sub>               | - | Hafnium oxide                                       |

| Si <sub>3</sub> N <sub>4</sub> | - | Silicon nitride                                     |

| $Al_2O_3$                      | - | Aluminium oxide                                     |

| AlN                            | - | Aluminium nitride                                   |

| SiGe                           | - | Silicon Germanium                                   |

| TiN                            | - | Titanium Nitride                                    |

| Cgate                          | - | Gate Capacitance                                    |

### LIST OF SYMBOLS

| nm                | - | nanometer                                 |

|-------------------|---|-------------------------------------------|

| $V_{dd}$          | - | Drain to drain voltage                    |

| I <sub>LEAK</sub> | - | Leakage current                           |

| Leff              | - | Effective channel length                  |

| $W_{eff}$         | - | Effective width                           |

| ŋstb              | - | SNR (Smaller-the-Better)                  |

| n                 | - | Number of tests                           |

| Yi                | - | Experimental value of the leakage current |

| Σ                 | - | Sum of leakage current of the experiment  |

### LIST OF APPENDICES

# TITLE PAGE

### APPENDIX

| Appendix A | Gantt Chart for Semester 1 | 65 |

|------------|----------------------------|----|

| Appendix B | Gantt Chart for Semester 2 | 66 |

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Problem Background

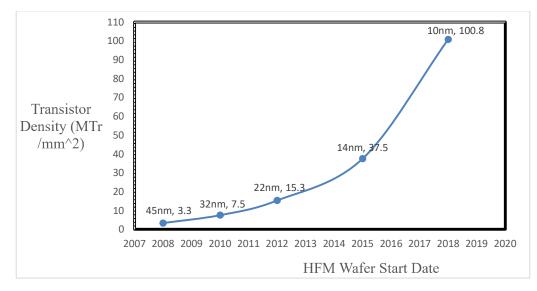

The guiding principle that is used for CMOS scaling for the past few decades is Moore's Law [1]. The research and development to improve the performance of Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is growing at an unprecedented rate since MOSFET is the most vital device in the field of electronic, communication and radio frequency application. One of the crucial methods to improve the performance of the MOSFET is by designing it into smaller dimension, which also means to downscale the size of the device [2]. Intel's state-of-art has doubled its transistor density in the recent years, from 45-nm having 3.3 million transistors per square millimeter to 10 nm having 100.8 million transistors per square

Figure 1.1: State-of-art for Intel's Transistors Density [3]

The gate controllability of the channel potential decreases as the MOSFET is shrinking down. This is due to the drain having an increase of longitudinal field, which causes the short channel effects to become worse [2]. Besides that, as the device dimension decreases, this also means that the equivalent oxide thickness (EOT) reduces, thus increases the leakage current, which makes the fabrication process of SiO<sub>2</sub> not able to carry out. Higher leakage current increases current densities and encourages higher power dissipation [4]. In fact, leakage current ( $I_{LEAK}$ ) has been identified as one of the main sources of leakage to the total power consumption of CMOS devices [5]. Both the SCE and high leakage current have become the crucial problems to MOSFET. Thus, having an extra gate is one of the attractive alternative ways in order to have increment of gate control over the channel [6].

For future scaling of CMOS technologies, Multigate MOSFETs (MuGFETs) have been considered as one of the attractive and promising candidates. This is because a better drive current had been shown by MuGFETs at a fixed value of  $V_{dd}$  [7]. FinFETs are one of the examples of MuGFETs, where the multigated architecture of FinFET having additional discrete fin sizing, which brings an advantage to the design [7] [8]. Crucially, Intel mentioned that 10 nm FinFET shows the capability in terms of higher speed performance and better energy efficiencies compared to the predecessors [3]. Meanwhile, the problem of gate leakage current can be solved by introducing the combination of high-k gate dielectric layer to replace the conventional SiO<sub>2</sub> [9]. This could potentially reduce the leakage current flowing through the gate dielectric layer and improve the reliability of the device.

In fact, in the advancement of CMOS technologies, both the Moore's Law and ITRS played a very significant role. Since the very first edition of the ITRS roadmap in the beginning of 90's, Moore's Law and ITRS have been the compliment to each other. The initial forecast of Gordon Moore is on the number of transistors that can be integrated into the microchip for the coming ten years, which is from 1965 to 1975, but it can be seen for the next three decades, the trend remain unchanged [10]. Meanwhile, ITRS, on the other hand, is an ambitious and reliable document, which is widely used as a guiding reference for the research of the advanced semiconductor device and manufacturing purposes that gives direction for the next generation of

devices. One of the vital sections which included in ITRS is finding and developing new device structures to replace the current conventional MOSFETs for a better performance. One of the suggestions provided in ITRS is using FinFET as the device to boost the performance without neglecting the short channel effects [11].

#### **1.2** Problem Statement

Scaling down the size of MOSFET is the main trend to achieve the target set by Moore's Law. In the current trend, the performance of MOSFET can be improved easily by scaling down its size. Over the past decades, many researchers have tried to enhance the scaling technology and have been successfully changed the physical dimensions of MOSFETs from larger to a smaller dimension [12]. However, the reduction of the channel length of the transistor has reached the limit in current technology. As the channel length are scaled to nanometer, the undesirable effects which are named short channel effects (SCEs) occur and become more problematic. The SCEs is defined as the channel length, L<sub>ch</sub> of a MOSFET becomes the same order of magnitude as the depletion widths associated with the drain and source, in other words, device downscaling has caused the drain area and source to be much closer to each other, thus resulting in short channel effects [13]. In this situation, the behaviour of the MOSFET is out of expected, and this undesired effect has created a huge impact in terms on the reliability, modelling and the performance.

Over the past few decades, silicon dioxide  $(SiO_2)$  has been used as the gate dielectric material. The continually scaling down of CMOS causes the continuous reduction of the equivalent oxide thickness (EOT) until as low as 1nm, which makes the fabrication of SiO<sub>2</sub> having difficulty to be achieved since this thickness would cause higher gate leakage current, and consequently causing increased of current densities and encourages high power dissipation [4]. In fact, one of the main causes of the current leakage is because of the ultra-thin gate which contribute much to the total static power dissipation of the CMOS device.

The main aim of this project is to simulate and optimize the process parameters for lowering leakage current in a 10 nm FinFET by replacing the conventional SiO<sub>2</sub> and polysilicon layers respectively with high-k dielectric materials, using L9 Taguchi Method.

Below are the objectives, which needed to be achieved to realize the aim of the project:

- i. To simulate a 10 nm FinFET with the deposition of high-k material (Hafnium Oxide) using TCAD Sentaurus from Synopsys.

- ii. To optimize the process parameters using L9 Taguchi Method in order to obtain a lower leakage current (I<sub>LEAK</sub>).

- iii. To perform a statistical analysis and predict the best process parameters combination of the 10 nm FinFET device using Analysis of Variance (ANOVA) while benchmarking with predicted data from ITRS and previous published results.

#### 1.4 **Project Scope**

- i. 10 nm FinFET is developed and simulated as the device structure with this gate length shows reduced SCE and leakage current with a higher drive current, thus lowering the leakage current.

- The device's process will be executed using TCAD Sentaurus from Synopsys. TCAD Sentaurus software is used throughout this whole project to organize, design and run simulations.

- iii. Optimization of the 10 nm FinFET using Hafnium Oxide (HfO<sub>2</sub>) as the dielectric layer to replace the conventional silicon dioxide for lower leakage

current. Hafnium oxide appears to be one of the most attractive type of high kdielectric materials and the demand for high-k dielectric materials in integrated circuits (IC) has becoming more and more imminent in the development of electronic devices towards miniaturization. Besides, the thickness of the gate oxide using HfO<sub>2</sub> would then be optimized throughout the simulation process.

iv. L9 Taguchi Method is used for the optimization of the process parameters. The advantages of Taguchi method over the other methods are that numerous factors can be simultaneously optimized, and more quantitative information can be extracted from fewer experimental trials.

#### **1.5** Chapter Organization

This report is separated into five chapters covering different aspects of this research. The overview of the work is described as follows:

Chapter 1: This chapter contains the introduction of this research project and brief discussion on background, problem statement, aim, objectives and project scope of this research project.

Chapter 2: This chapter covers the literature review of the project. It contains the concept of this project and on previous work done by various researchers. This chapter also discusses about the optimization process using L9 Taguchi method by various researchers.

Chapter 3: This chapter defines the methodology or procedure used in the project. Flow charts are also included for better description. Besides, this chapter explains the procedure to model and simulate the design. Performance parameters used to compare and analyse the 10 nm FinFET using Taguchi method and ANOVA also been discussed.

Chapter 4: This chapter contains the results for this project. The simulation results obtained are also discussed and the best setting of parameters is then chosen based on the statistical analysis on the performance of the device.

Chapter 5: The chapter contains the summary or conclusion of the research project and findings. Apart from that, this chapter also included the directions and suggestions of future works for improvement of current work.

#### REFERENCES

- [1] M. Bohr, "The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era," *2011 Int. Electron Devices Meet.*, pp. 1.1.1-1.1.6, 2011.

- [2] Y.-B. Kim, "Challenges for Nanoscale MOSFETs and Emerging Nanoelectronics," *Trans. Electr. Electron. Mater.*, vol. 11, no. 3, pp. 93–105, 2010.

- [3] "Intel Now Packs 100 Million Transistors in Each Square Millimeter IEEE Spectrum." [Online]. Available: https://spectrum.ieee.org/nanoclast/semiconductors/processors/intel-nowpacks-100-million-transistors-in-each-square-millimeter. [Accessed: 17-Dec-2019].

- [4] C. Choi, "Thickness and material dependence of capping layers on flatband voltage (VFB) and equivalent oxide thickness (EOT) with high-k gate dielectric/metal gate stack for gate-first process applications," *Microelectron. Eng.*, vol. 89, no. 1, pp. 34–36, 2012.

- [5] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," *Proc. IEEE*, vol. 91, no. 2, pp. 305–327, 2003.

- [6] I. Ferain, C. A. Colinge, and J. P. Colinge, "Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors," *Nature*, vol. 479, no. 7373, pp. 310–316, 2011.

- [7] F. A. Md Rezali, N. A. F. Othman, M. Mazhar, S. W. M. Hatta, and N. Soin, "Performance and Device Design Based on Geometry and Process Considerations for 14/16-nm Strained FinFETs," *IEEE Trans. Electron Devices*, vol. 63, no. 3, pp. 974–981, 2016.

- [8] D. Hisamoto *et al.*, "FinFET A Self-Aligned Double-Gate MOSFET," vol. 47, no. 12, pp. 2320–2325, 2000.

- [9] N. Shashank, S. Basak, and R. K. Nahar, "Design and Simulation of Nano Scale High-K Based MOSFETs with Poly Silicon and Metal Gate Electrodes," *Int. J. Adv. Technol.*, vol. 1, no. 2, pp. 252–261, 2010.

- [10] G. Baccarani, M. R. Wordeman, and R. H. Dennard, "Generalized Scaling

Theory and Its Application," *IEEE Trans. Electron Devices*, vol. 41, no. 4, pp. 1283–1290, 1984.

- [11] ITRS 2015. *http://www.itrs2.net/.*

- [12] S. Asai and Y. Wada, "Technology challenges for integration near and below 0.1 µm," *Proc. IEEE*, vol. 85, no. 4, pp. 505–520, 1997.

- [13] K. Agarwal Gupta, "Device Characterisation of Short Channel Devices and its Impact on CMOS Circuit Design," *Int. J. VLSI Des. Commun. Syst.*, vol. 3, no. 5, pp. 163–173, 2012.

- [14] A. Agarwal, C. H. Kim, S. Mukhopadhyay, and K. Roy, "Impact and Design Considerations, I," pp. 6–11.

- [15] M. Anis, S. Member, M. Allam, and M. Elmasry, "Impact of Technology Scaling on CMOS Logic Styles," *IEEE Trans. Circuits Syst. II Analog Digit. Signal Process.*, vol. 49, no. 8, pp. 577–588, 2002.

- [16] S. Borkar and I. Corporation, "Design Challenges of Technology Scaling," *Ieee Micro*, pp. 23–29, 1999.

- [17] A. Chaudhry, Fundamentals of Nanoscaled Field Effect Transistors. .

- [18] F. Assad, Z. Ren, S. Datta, M. Lundstrom, and P. Bendix, "Performance limits of silicon MOSFET's," *Tech. Dig. - Int. Electron Devices Meet.*, pp. 547–550, 1999.

- [19] P. Gargini, "Roadmap: Past, Present and Future," Surf. Prep. Clean. Conf., no. April, 2016.

- [20] T. Pompl *et al.*, "Gate dielectric integrity along the road map of CMOS scaling including multi-gate FET, TiN metal gate, and HfSiON high-k gate dielectric," *IEEE Int. Reliab. Phys. Symp. Proc.*, pp. 655–656, 2006.

- [21] K. Roy, J. P. Kulkarni, and S. K. Gupta, "Device/circuit interactions at 22nm technology node," *Proc. - Des. Autom. Conf.*, pp. 97–102, 2009.

- [22] V. K. Khanna, Integrated Nanoelectronics. 2016.

- [23] H. Asija, V. Nehra, and P. K. Dahiya, "Leakage Power Reduction Technique in Cmos Circuit: a State-of-the-Art Review," *IOSR J. VLSI Signal Process.*, vol. 5, no. 4, pp. 31–36, 2015.

- [24] Y. C. Yeo, T. J. King, and C. Hu, "MOSFET gate leakage modeling and selection guide for alternative gate dielectrics based on leakage considerations," *IEEE Trans. Electron Devices*, vol. 50, no. 4, pp. 1027–1035, 2003.

- [25] A. H. Afifah Maheran, P. S. Menon, I. Ahmad, and S. Shaari, "Optimisation of

process parameters for lower leakage current in 22 nm n-type MOSFET device using Taguchi method," *J. Teknol. (Sciences Eng.*, vol. 68, no. 4, pp. 1–5, 2014.

- [26] Y. C. Wu and Y. R. Jhan, *3D TCAD simulation for CMOS nanoeletronic devices*. 2017.

- [27] H. H. Dielectrics *et al.*, "Hafnium-based High-K Dielectrics," vol. 78758, no. 512, pp. 122–125.

- [28] R. Chaudhary, R. Mukhiya, G. S. Patel, P. R. Mudimela, and R. Sharma, "Simulation of MOSFET with different dielectric films," *Proc. - 2nd Int. Conf. Intell. Circuits Syst. ICICS 2018*, pp. 177–183, 2018.

- [29] J. C. Pravin, P. Prajoon, F. P. Nesamania, G. Srikesh, P. Senthil Kumar, and D. Nirmal, "Nanoscale High-k Dielectrics for Junctionless Nanowire Transistor for Drain Current Analysis," *J. Electron. Mater.*, vol. 47, no. 5, pp. 2679–2686, 2018.

- [30] M. Prasad and U. B. Mahadevaswamy, "A novel approach for leakage current reduction of 14nm NMOS device using HfO2 dielectric," *Int. Conf. Electr. Electron. Commun. Comput. Technol. Optim. Tech. ICEECCOT 2017*, vol. 2018-Janua, no. 1, pp. 129–134, 2018.

- [31] A. Nisha Justeena, D. Nirmal, and D. Gracia, "Design and analysis of tunnel fet using high K dielectric materials," *Proc. IEEE Int. Conf. Innov. Electr. Electron. Instrum. Media Technol. ICIEEIMT 2017*, vol. 2017-Janua, no. 978, pp. 177–180, 2017.

- [32] D. Morillon *et al.*, "High voltage MOSFETs integration on advanced CMOS technology: Characterization of thick gate oxides incorporating high k metal gate stack from logic core process," *IEEE Int. Conf. Microelectron. Test Struct.*, pp. 2–6, 2017.

- [33] A. H. A. Maheran, P. S. Menon, S. Shaari, I. Ahmad, and Z. A. N. Faizah,

"Statistical optimization of process parameters for threshold voltage in 22 nm

p-Type MOSFET using Taguchi method," *RSM 2015 2015 IEEE Reg. Symp. Micro Nano Electron. Proc.*, pp. 1–4, 2015.

- [34] Nirmal, D., Kumar, P. V., Joy, D., Jebalin, B. K. and Kumar, N. M. Nanoscale tri gate MOSFET for ultra low power applications using high-k dielectrics. Nanoelectronics Conference (INEC), 2013 IEEE 5th International. IEEE. 2013. 12–19

- [35] N. Collaert et al., "Multi-gate devices for the 32nm technology node and

beyond," *ESSDERC 2007 - Proc. 37th Eur. Solid-State Device Res. Conf.*, vol. 2007, pp. 143–146, 2007.

- [36] P. Laube, "Semiconductor technology from A to Z: Fundamentals." [Online]. Available: https://www.halbleiter.org/en/fundamentals/. [Accessed: 11-Jun-2020].

- [37] T. M. F. Sensors and V. S. Luong, "Planarization, Fabrication, and Characterization of," vol. 17, no. 1, pp. 11–25, 2018.

- [38] C. C. Wu *et al.*, "High performance 22/20nm FinFET CMOS devices with advanced high-K/metal gate scheme," *Tech. Dig. - Int. Electron Devices Meet. IEDM*, pp. 600–603, 2010.

- [39] C. Auth *et al.*, "A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," *Dig. Tech. Pap. - Symp. VLSI Technol.*, vol. m, no. 2003, pp. 131–132, 2012.

- [40] S. Takagi *et al.*, "Carrier-transport-enhanced channel CMOS for improved power consumption and performance," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 21–39, 2008.

- [41] S. Y. Wu et al., "A 16nm FinFET CMOS technology for mobile SoC and computing applications," Tech. Dig. - Int. Electron Devices Meet. IEDM, pp. 224–227, 2013.

- [42] S. Natarajan *et al.*, "A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 μm2

SRAM cell size," *Tech. Dig. Int. Electron Devices Meet. IEDM*, vol. 2015-Febru, no. February, pp. 3.7.1-3.7.3, 2015.

- [43] G. Saini, A. K. Rana, P. K. Pal, and S. Jadav, "Leakage behavior of underlap FinFET structure: A simulation study," 2010 Int. Conf. Comput. Commun. Technol. ICCCT-2010, pp. 302–305, 2010.

- [44] M. Moreau, D. Munteanu, and J. L. Autran, "Simulation study of Short-Channel Effects and quantum confinement in double-gate FinFET devices with highmobility materials," *Microelectron. Eng.*, vol. 88, no. 4, pp. 366–369, 2011.

- [45] F. A. Md Rezali, N. A. F. Othman, M. Mazhar, S. W. M. Hatta, and N. Soin, "Performance and Device Design Based on Geometry and Process Considerations for 14/16-nm Strained FinFETs," *IEEE Trans. Electron Devices*, vol. 63, no. 3, pp. 974–981, 2016.

- [46] J. J. Kim, M. Jin, H. Sagong, and S. Pae, "Reliability assessment of 10nm finfet process technology," *Proc. Int. Symp. Phys. Fail. Anal. Integr. Circuits, IPFA*, vol. 2018-July, pp. 1–6, 2018.

- [47] K. E. Kaharudin, A. H. Hamidon, and F. Salehuddin, "Implementation of Taguchi modeling for higher drive current (ION) in vertical DG-MOSFET device," J. Telecommun. Electron. Comput. Eng., vol. 6, no. 2, pp. 11–17, 2014.

- [48] N. Mohammad, F. Salehuddin, H. A. Elgomati, I. Ahmad, and N. A. A. Rahman, "MOSFET Device," no. December 2015, 2013.

- [49] H. A. Elgomati, B. Y. Majlis, A. M. A. Hamid, P. M. Susthitha, and I. Ahmad,

"Modelling of process parameters for 32nm PMOS transistor using Taguchi method," *Proc. - 6th Asia Int. Conf. Math. Model. Comput. Simulation, AMS* 2012, pp. 40–45, 2012.

- [50] N. Rosli *et al.*, "Taguchi Modelling of Process Parameters in VDG-MOSFET Device for Higher Ion/Ioff Ratio," Jurnal Teknologi ,vol. 1, pp. 1–6, 2015.

- [51] S. Banerjee, E. Sarkar, and A. Mukherjee, "Effect of Fin Width and Fin Height on Threshold Voltage for Tripple Gate Rectangular FinFET," vol. 2, pp. 27–30, 2018.

- [52] R. A. N. D. Discussion, "Electrical and Physical Characterization of High-k Dielectric Layers," pp. 196–199.

- [53] S. K. Mah, I. Ahmad, P. J. Ker, and Z. A. Noor Faizah, "Modelling of 14NM gate length La2O3-based n-type MOSFET," *J. Telecommun. Electron. Comput. Eng.*, vol. 8, no. 4, pp. 107–110, 2016.