# Modeling of Nanoscale MOSFET Performance in the Velocity Saturation Region

Michael Tan Loong Peng<sup>\*</sup> and Razali Ismail

Faculty of Electrical Engineering, Universiti Teknologi Malaysia, 81310 UTM Skudai, Johor, Malaysia.

\*Corresponding author: michael@fke.utm.my (Michael Tan), Tel: 607-5535411, Fax: 607-5566262

**Abstract:** Velocity saturation as a function of temperature and drain voltage for n-channel MOSFET is investigated. The combination of an existing current-voltage (I-V) model, drain source resistance model and a more precise mobility derivation gives an accurate representation of velocity saturation as a function of the above parameters. A simplified threshold voltage formulation is developed to provide similar accuracy when compared to actual devices. The models show good agreement with the experimental data over a wide range of gate and drain bias for 90nm process technology.

Keywords: Current-voltage, Drain source resistance, MOSFET, Threshold voltage, Velocity saturation.

# **1. INTRODUCTION**

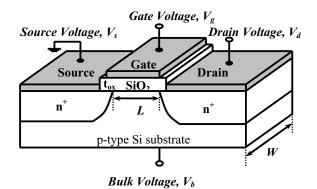

Velocity saturation in Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is a phenomenon which occurs in high electric field where the mobility degradation causes drift velocity to reach a maximum value typically at  $v_{sat} \approx 10^7$  cm/s. The electric field at which saturation occurs differs with different semiconductors. At high fields up to  $10^6$  V/cm [1] in nanoelectronic devices, scattering rate of highly energetic electrons increases with the average carrier energy. Eventually, the carrier loses their energy by opticalphonon emission nearly as fast as they gain from the field. This ultimately increases the transit time of carriers through the channel. In the quest to obtain higher speed, performance and chip density, the channel length (L) and channel width (W) are being scaled down [2]. The basic structure of a n-channel MOSFET (NMOS) is shown in Figure 1.

Figure 1. Basic structure of a NMOS

As devices are getting smaller and smaller, undesirable effects are encountered. In the current 65nm and 90nm process technology designs, second order effects such as velocity saturation, short channel effect (SCE), channel length modulation (CLM) and narrow width effect

(NWE) are encountered during the design phases [3]. Velocity saturation particularly affects the drive strength in the saturation velocity region. SCE could be ignored in previous long channel CMOS generation as the effects is not that significant [4].

The development of short channel semi empirical model for nanoscale MOSFET [5-7] has enable an in depth investigation on the saturation velocity impact in a wider scope. The nanoscale MOSFET has features size beyond 50nm and below 100nm for 90nm process technology. In this paper, the occurrence of velocity saturation,  $v_{sat}$  and its impact on electric field, external environment and I-V characteristic at different process parameters are analyzed and presented. The paper is organized as follows. Section 1 gives a deeper insight onto velocity saturation and its limitation that was highlighted by several researchers [8-10] as well as the key contribution. A detailed description on the models used is presented in Section 2. Results are presented and discussed in Section 3. Section 4 concludes the study.

## 2. MODEL AND METHODS

Threshold voltage, effective mobility, doping concentration, diffused junction depth, gate oxide thickness, gate oxide capacitance and others related physical parameter are extracted from the experimental data generated from the Intel Proprietary Schematic Editor and Intel Proprietary Circuit Simulator. Subsequently, curves based on the newly developed threshold voltage model, effective mobility model and I-V model are plotted using Microsoft Excel. The velocity longitudinal field equation is then incorporated to model the velocity saturation region (VSR). Finally, based on the graphs depicted, the velocity saturation relationship between the models is analyzed.

## 2.1 The Threshold Voltage Model

A new effective threshold voltage model is derived in this section based on the long channel device. Several modifications are employed to consider the effects of short and narrow channel effects. There are varieties of definition models [11]–[14] which are used to measure and predict the threshold voltage model each with its unique features and limitations. In this work, the threshold voltage equation for n-channel MOSFET with n+ polysilicon gate and p-type silicon substrate is defined as

$$V_T = 2\phi_f + V_{FB} + \frac{\sqrt{2\varepsilon_{SI}qN_A(2\phi_f)}}{C_{ox}}$$

(1)

where  $\phi_f$  is the Fermi potential given as

$$\phi_f = \frac{kT}{q} \ln\left(\frac{N_A}{n_i}\right) \tag{2}$$

$N_A$  is the substrate doping concentration, k is the Boltzmann's constant,  $\varepsilon_{Si}$  is the dielectric permittivity of the silicon and  $C_{ox}$  is the gate oxide capacitance. The flat band voltage,  $V_{FB}$  is given as

$$V_{FB} = \left(\phi_{ms} - \frac{Q_{ss}}{C_{ox}}\right) \tag{3}$$

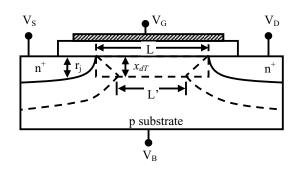

where  $\phi_{ms}$  is the metal-semiconductor work function difference and  $Q_{ss}$  is the fixed oxide charge. As the device is scaled down in size, additional effects on  $V_T$ occur. The short channel threshold voltage shift reducew  $V_T$  predicted by the long channel. The threshold voltage shift due to short channel effects can be expressed as

$$\Delta V_{T \text{ for short channel}} = -\frac{qNx_{dT}}{C_{ox}} \left[ \frac{r_j}{L} \sqrt{1 + \frac{2x_{dT}}{r_j}} - 1 \right]$$

(4)

where  $x_{dT}$  is the lateral space charge width and  $r_j$  is the diffused junction as shown in Figure 2 below.

Figure 2. Charge sharing in the short channel threshold voltage model

On the other hand, as the channel width is reduced, the threshold voltage is reduced. This is know as the narrowwidth effect and can be approximated as

$$\Delta V_{T \text{ for narrow width}} = \frac{qNx_{dT}}{C_{ox}} \left[ \frac{\xi x_{dT}}{W} \right]$$

(5)

where  $\xi$  is the empirical parameter that account for the shape of the fringe depletion region and *q* is the electronic charge. The resultant threshold voltage expression that take into account the short channel and narrow width effect can be expressed as

$$V_{T} = 2\phi_{jp} + V_{FB} \pm \frac{\sqrt{2\varepsilon q N(2\phi_{f})}}{C_{ox}}$$

$$-\frac{q N x_{dT}}{C_{ox}} \left[ \left( \frac{r_{j}}{L} \sqrt{1 + \frac{2x_{dT}}{r_{j}}} - 1 \right) - \left( \frac{\xi x_{dT}}{W} \right) \right]$$

(6)

#### The Mobility Model

The effective mobility of inversion layer carriers is a significant factor in the performance of a MOSFET. A physically based semi-empirical equation is employed to model the surface roughness, phonon and coulomb scattering. This model is an extension of the work done by Schwarz and Russek [15]. The scattering mechanism now includes surface roughness and coulombic scattering to account for high transverse electric field and high doping concentration operation level. Each scattering contribution to the effective mobility is calculated according to Matthiessen's rule as depicted below [16].

$$\mu_{\perp eff} = \left[\frac{1}{\mu_{ph}} + \frac{1}{\mu_{sr}} + \frac{1}{\mu_c}\right]^{-1}$$

(7)

where  $\mu_c$  is Coulombic scattering due to doping concentration,  $\mu_{ph}$  is phonon scattering and  $\mu_{sr}$  is surface roughness scattering. The model for effective mobility of electron in MOS with (100) plane structure is given as [17]

$$E_{\perp eff} = \frac{1}{\varepsilon_{si}} \left( \frac{1}{2} Q_{inv} + Q_B \right) = \frac{1}{6t_{ox}} \left( V_{gs} + V_t \right)$$

(8)

$$\mu_{ph} = \left[ \left( \frac{K_B}{T_n^{-2.5}} \right)^{-1} + \left( \frac{z}{3.2 \times 10^{-9} \, p T_n^{\frac{1}{2}}} \right)^{-1} \right]^{-1} \tag{9}$$

$$\mu_{sr} = K_{sr} E_{\perp eff}^{-2} \tag{10}$$

$$\mu_{c} = \frac{1.1 \times 10^{-21} T_{n}^{1.5}}{\ln\left(1 + \gamma_{BH}^{2}\right) - \frac{\gamma_{BH}^{2}}{\gamma_{BH}^{2} + 1}} \frac{1}{N_{A}}$$

(11)

$$p = 0.09T_n^{1.75} + 4.53 \times 10^{-8} \left(\frac{N_I}{z}\right)^{-0.25} \left(\frac{N_f}{T_n}\right) \quad (12)$$

$$z = z_{QM} + z_d = \frac{0.388T_n}{E_{\perp eff}} + \frac{1.73 \times 10^{-5}}{E_{\perp eff}}$$

(13)

where *p* is the Fuchs factoring scattering which describe the probability of diffuse scattering, *z* is the averaged inversion layer width,  $N_f$  is the interface charge density,  $z_{cl}$  is the classical channel width,  $z_{QM}$  is the quantum mechanically broadened width due to the two dimensional quantization of the energy levels in the inversion layer,  $\gamma^2_{BH}$  is the Brooks Herring constant while  $K_B$ ,  $K_{QM}$ ,  $K_{sr}$ ,  $K_c$  and  $K_{\gamma}$  are numerical coefficients that provide best agreements with the experimental data. The normalized temperature,  $T_n$  is given by

$$T_n = \frac{T}{300} \tag{14}$$

#### 2.2 The I-V Model

There are parasitic resistances associated with the source and drain. These source drain resistance has to be taken into account as it causes a substantial drain current degradation as well as an RC delay. A physically-based source/drain (S/D) series resistance  $R_{ds}$  model comprising intrinsic and extrinsic component is included. The model is based on the concept introduced by Zhou and Lim [18] and is given by

$$R_{s/d} = R_{ext} + R_{int} = \frac{2\rho S}{x_j W} + \frac{\upsilon}{V_{GS} - V_T}$$

(15)

where  $R_{ext}$  is the extrinsic resistance,  $R_{int}$  is intrinsic resistance,  $x_j$  is the junction depth, S is the spacer thickness and  $\rho$  is taken as effective resistivity of the S/D regions (including contacts). The I-V model is based on the compact model derivation by Xing Zhou *et al.* [19].

The model has similar characteristic as BSIM3v3 model and comparable to HSPICE level 49. It is selected to be the core model formulation since it well considered being the standard model from deep submicron into nanoscale CMOS circuit design. The step by step derivation of  $I_{ds}$  model including the effect of CLM and  $R_{sd}$  is given below. The initial drain current,  $I_{ds}$  when source drain resistance is ignored is expressed as

$$I_{ds0} = \frac{\mu_{eff} C_{ox} W}{(2L) \left[ 1 + \left( V_{deff} / EL \right) \right]} \left( V_{GT} V_{deff} - \frac{1}{2} m V_{deff}^{2} \right)$$

(16)

$V_{deff}$  is the smoothing function to replace  $V_{ds}$  for a smooth transition from linear to saturation region to form a single compact model and is given as

$$V_{deff} = V_{dsat} - \frac{1}{2} \left[ V_{dsat} - V_{ds} - \delta_s \right] - \frac{1}{2} \left[ \sqrt{\left( V_{dsat} - V_{ds} - \delta_s \right)^2 + 4 \delta_s V_{dsat}} \right]$$

(17)

When CLM effect is taken into consideration, Equation (16) can be rewritten as

$$I_{deff} = \left(1 + \frac{V_{ds} - V_{deff}}{V_{Aeff}}\right) I_{ds0}$$

(18)

where  $I_{deff}$  is the smoothing function for  $I_{ds0}$  with effective early voltage,  $V_{Aeff}$ . With the inclusion of Equation (17) and Equation (18), the drain current is given by

$$I_{ds} = \frac{I_{deff}}{1 + \left(R_{s/d} I_{deff}\right) / V_{deff}}$$

(19)

#### 2.4 The Velocity-Field Model

In order to describe the electric field dependence, the velocity model for electron [20-21] is given as

$$v_{d} = \frac{\mu_{eff} E_{(1.14)}}{\left[1 + \left(E_{y}/E_{c}\right)^{2}\right]^{1/2}}$$

(20)

where  $E_c$  is the critical electric field for velocity saturation defined by

$$E_c = \frac{\nu_{sat}}{\mu_{eff}} \tag{21}$$

The longitudinal electric field across the channel,  $E_c$  can be expressed as

$$E_y = \frac{V_d - IR_{sd}}{L} \tag{22}$$

## 3. RESULTS AND DISCUSSION

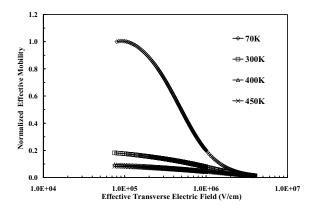

The simulations cover a wide range of temperatures, effective field and parasitic resistance to establish reliable models operating at different environment. The short channel NMOS channel length is 80 nm with the widths of 1.3 micron. Figure 3 gives the variation of the electron mobility as a function of effective longitudinal field along the channel.

Figure 3. Normalized effective mobility versus transverse electric field at different temperature

It is shown that for an electric field of  $1.0 \times 10^{5}$  V/cm, devices at 77K have a higher effective mobility and this

in turn gives a higher drift velocity. As the temperature is increase to 300 K and above, the mobility decreases substantially as scattering is far more frequent. Devices at low temperature will first gain velocity saturation. The drift velocity of electrons at different temperature becomes saturates beyond the critical field region at  $1.0 \times 10^6$  V/cm.

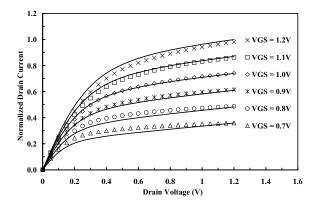

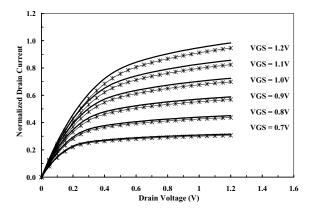

In order to get an overall best fit graph, the velocity saturation value has to be in the range of the process model parameter. The velocity saturation is extracted from the experimental data by using the I-V models. By incorporating the parameter into the velocity model, the simulation results illustrate a satisfactory agreement with the I-V experimental data across a wide range of gate voltage as shown in Figure 4.

Figure 4. Comparison of calculated versus measured I-V characteristics for a wide range of gate voltage at resistivity  $3.5e-5 \Omega/cm$

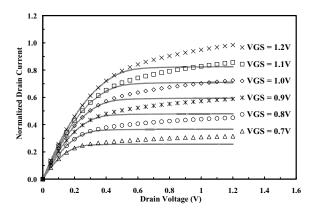

The results of experimental data investigation with simulation model are presented. This includes observation in the constant velocity saturation region with respect to gate voltage at low and high effective parasitic resistance. Parasitic resistances,  $\rho$  of 3.5e-5  $\Omega$ /m and 5.5e-5  $\Omega$ /m are used. Low parasitic resistance has a reduced source drain series resistance,  $R_{sd}$  and this gives a higher drain current as shown in Figure 5.

Figure 5. Comparison of calculated I-V characteristics for a wide range of gate voltage at resistivity 3.5e-5  $\Omega$ /cm (bold solid line) and 4.5e-5  $\Omega$ /cm (in asterix)

In addition, saturation voltage is reduced. The reason for this is that drain current is inversely proportional to the drain series resistance. When  $R_{sd}$  is taken into consideration, a larger drain and source voltage need to be applied to achieve velocity saturation in order to make up for the drain and source voltage drop. It is found that the drift velocity is affected by the longitudinal electric field drop when  $R_{sd}$  is increased.

Channel length modulation (CLM) is a non ideal characteristic that is present in short channel MOSFET. The channel length is modulated by the drain current when it is saturated. The current deviate from its ideal I-V curve as the average electric field increase with the shortening of effective channel length. Figure 6 show the comparison of the calculated I-V characteristics for a wide range of gate voltage at resistivities of  $3.5e-5 \Omega/cm$  with and without channel length modulation.

Figure 6. Comparison of calculated I-V characteristics for a wide range of gate voltage at resistivity 3.5e-5  $\Omega$ /cm with CLM (pattern) and without CLM (shaded line)

Notable differences can be found where the saturation drain current is predicted higher in the saturation region compared to the shaded lines (without CLM) as shown in Figure 6.

#### 4. CONCLUSION

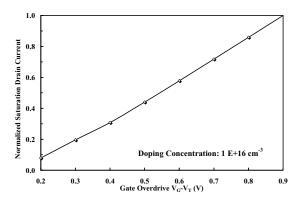

The analytical and semi empirical models are used to investigate the electrical behavior of nanoscale NMOS. We have demonstrated that simulation from the I-V model is in good agreement with the experimental data. The semi empirical formula presented here has allowed us to see the impact of velocity saturation. Saturation current in the short channel devices no longer has an ideal square law dependence predicted for long channel. The saturation current is now increasing linearly with gate voltage as shown in Figure 7.

Figure 7. Normalized saturation drain current versus gate overdrive

On the other hand, the drain current for short channel device under the influence of velocity saturation is lower causing a longer switching transition time due to a low gate overdrive. The introduction of strained silicon can be used to enhance transistor current flow or drive current which allow electrons and holes to move smoother at higher mobility.

## ACKNOWLEDGMENT

The authors would like to thank Intel Penang Design Center (PDC) for providing simulation tools for this work. Our thankfulness also goes to Ravisangar Muniandy, Wong Vee Kin, Lock Choon Hou and Dr Kelvin Kwa Sian Kiat for discussion on various aspects of modeling.

#### REFERENCES

- V. K. Arora, "High-Field Effects in Sub-Micron Devices," Conference on Optoelectronic and Microelectronic Materials and Devices (COMMAD 2000), 2000, pp. 33-40.

- [2] T. Sakurai and A. R. Newton. "A simple MOSFET model for circuit analysis," *IEEE Trans. Electron Devices*, vol. 38, no. 4, pp. 887-894, 2001.

- [3] Y. Taur, D. A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S.-H. Lo, G. A. Sai-Halasz, R. G. Viswanathan, H.-J. C. Wann, S. J. Wind, and H.-S. Wong, "CMOS Scaling into the Nanometer Regime," *Proceedings of the IEEE*, vol. 85, no. 4, pp. 486–504, 1997.

- [4] V. K. Arora, "The Electron Temperature in Nanostructures Subjected to a High Electric Field," Proceedings of *IEEE International Conference on Semiconductor Electronics*, 2002, pp. 1-8.

- [5] Michael L. P. Tan, R. Ismail, R. Muniandy and Wong V. K., "Velocity Saturation Dependence on Temperature, Substrate Doping Concentration and Longitudinal Electric Field in Nanoscale MOSFET," *Proceedings IEEE National Symposium on Microelectronics*, 2005, pp. 210-214.

- [6] M. Pattanaik and S. Banerjee, "A new approach to model I and V characteristics for nanoscale MOSFETs," *International Symposium on VLSI*

Technology, Systems, and Applications, 2003, pp. 92-95.

- [7] D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur, and H.-S. P. Wong, "Device Scaling Limits of Si MOSFETs and Their Application Dependencies," *Proceedings of the IEEE*, vol. 89, no. 3, pp. 259-288, 2001.

- [8] P. D. Agnello, "Process requirements for continued scaling of CMOS -The Need and Prospects for Atomic-Level Manipulation," *IBM J. Res. & Dev.*, vol. 46, no.2/3, pp. 317-338, 2002.

- [9] A. Lochtefeld, I. J. Djomehri, G. Samudra, and D. A. Antoniadis, "New insights into carrier transport in n-MOSFETs," *IBM J. Res. & Dev.*, vol. 46, no. 2/3, pp. 347-358, 2002.

- [10] J. R. Hauser, "Extraction of experimental mobility data for MOS devices," *IEEE Transactions Electron Devices*, vol. 43, no. 11, pp. 1981-1988, 1996.

- [11] R. Wang, J. Dunkley, T. A. DeMassa and L.F. Jelsma, "Threshold Voltage Variations with Temperature in MOS Transistors," *IEEE Trans. Electron Dev*, vol. 18, no. 6, pp. 386-388, 1971.

- [12] X. Zhou, K. Y. Lim and D. Lim, "A simple and unambiguous definition of threshold voltage and its implications in deep-submicron MOS device modeling," *IEEE Transactions on Electron Devices*, vol. 46, no. 4, pp. 807-809, 1999.

- [13] A. Akers, and J. J. Sanchez, "Threshold voltage models of short, narrow, and small geometry MOSFET's: A review," *Solid-State Electron*, vol. 25, no. 7, pp. 621-641, 1982.

- [14] H. S. Wong, M. H.White, T. J. Krutsick and R. V. Booth, "Modeling of transconductance degradation and extraction of threshold voltage in thin oxide MOSFET's," *Solid-State Electron.*, vol. 30, no. 9, pp. 953-968, 1987.

- [15] S. A. Schwarz and S. E. Russek, "Semi-empirical equations for electron velocity in silicon: Part II— MOS inversion layer," *IEEE Trans. Electron Devices*, vol. 30, no. 12, pp. 1634-1639, 1983.

- [16] K. Y. Lim and X. Zhou, "A physically-based semiempirical effective mobility model for MOSFET compact I–V modeling," *Solid-State Electron*, vol. 45, no. 1, pp. 193-197, 2001.

- [17] H. Shin, G. M. Yeric, A. F. Tasch and C. M. Maziar, "Physically-based Models for Effective Mobility and Local Field Mobility of Electrons in MOS Inversion Layers," *Solid-State Electron.*, vol. 34, no. 6, pp. 545-552, 1991.

- [18] X. Zhou and K. Y. Lim, "Unified MOSFET compact I-V model formulation through physics-based effective transformation," *IEEE Transactions on Electron Devices*, vol. 48, no. 5, pp. 887-896, 2001.

- [19] X. Zhou and K. Y. Lim, "Physically-based semiempirical series resistance model for deep-submicron MOSFET I-V modeling," *IEEE Transactions on Electron Devices*, vol. 47, no. 6, pp.1300-1302, 2000.

- [20] F. Assaderaghi, P. K. Ko and C. Hu, "Observation of velocity overshoot in silicon inversion layers," *IEEE Electron Device Letters*, vol. 14, no. 10, pp. 484-86, 1993.

- [21] P. K. Ko, "Approaches to scaling," VLSI Electronics: Microstructure Science, vol.18, no.1, pp.1-37, 1989.