# Analysis, Design and Simulation of RC Passive Damping Network in a Simple Distributed DC Power System using PSpice

Awang Jusoh\*, Zainal Salam and Lim Aik Jin

Faculty of Electrical Engineering, Universiti Teknologi Malaysia, 81310 UTM Skudai, Johor, Malaysia.

\*Corresponding author: awang@fke.utm.my (Awang Jusoh), Tel: 607-5535787, Fax: 607-5566262

**Abstract:** The sub-system interaction and instability phenomena are a common problem in the Distributed Power System (DPS). In order to regulate the output voltage or the speed, the internal control function of a converter known as constant power load (CPL) results in the converter tends to draw a constant power. This phenomenon cause the input impedance of CPL has negative incremental input impedance, which tends to create instability as it is connected to a system. This paper concerns about the compensation method used to improve the stability of two or more connected subsystems, consisting of an L-C filter and a CPL. A compensation method known as passive damping network containing only RC components is examined purposely to eliminate and reduce the instability of the subsystem. The passive damping network was designed and simulated using PSpice. The results show that the designed passive damping network is suitable for small-scale power distribution system that contains constant power load with power level of 1 kW.

**Keywords:** Constant power load, DC-DC converter, Passive damping circuit.

### 1. INTRODUCTION

In a distributed power system (DPS), the instability phenomenon is a common problem. DPS is a system, where the power processing functions are distributed among many power processing units or DC/DC converters at the point of need. It is being used in applications such as aircraft, spacecraft, hybrid-electric and electric vehicles, ships, defense electronic power systems, communication and computer systems. The beneficial in terms of weight, size, isolation, voltage regulation, flexibility, capability to integrate a large variety of loads and also enables one to control more easily the quality of power reaching each separate board [1-2] are the reason of using it.

However DPS has some drawbacks such as interaction between the converters and bus instability, as well as imbalance in power distribution among parallel converters, which leads to an unequal distribution of output current hence may create excessive stress on some of the modules and increase their rate of failure. The interaction arises because each individual converter has internal control functions, such as the regulation of the converter output voltage or motor speed [3-6]. As a result, the converter tends to draw a constant power and therefore has a negative incremental input resistance within the bandwidth of the converter control loop. The negative incremental input impedance characteristic is a main characteristic of the constant power load (CPL). When the source voltage falls, then the operation of the internal controller results in the converter drawing more current. This in turn could cause the source voltage to fall even further.

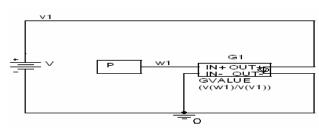

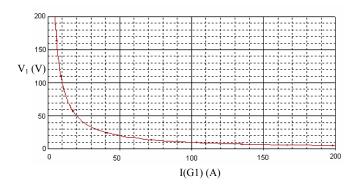

The negative incremental impedance of a CPL means that it has a hyperbolic characteristic of the voltage against current. CPL can be modeled as a dependent current source, that is i = v/P, where v in the input voltage and P is the output power. A CPL can be constructed using Analogue Behavior Model (ABM) using block GVALUE in Orcard PSpice simulator. In order to ensure constant power, GVALUE is used as a voltage control current source (VCCS), in such away that it tries to maintain constant current by controlling the voltage of the DC bus voltage. A simple CPL model with bus voltage V and power level P is shown in Figure 1. It shows that constant current is obtained by power (P) divided by voltage (v). Figure 2 shows the CPL characteristic as the input voltage varies with P is set to 1 kW. It clearly shows that as the input voltage increases, the current decreases as expected, the symbol of the impedance can be expressed as  $-R_L$ .

Figure 1. CPL block diagram

Figure 2. The CPL characteristics

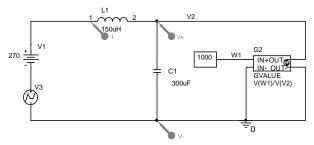

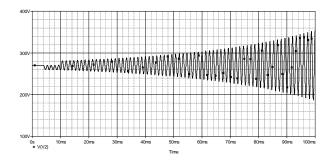

The instability phenomenon causes by the interaction of LC filter and CPL can be shown in a simple circuit, Figure 3. The L-C filter and a CPL are connected to supply voltage of 270 Vdc. The values is chosen based on typical practical values. The input voltage disturbance  $V_3$  with magnitude of 50 V is injected. The simulation result is shown in Figure 4. The plot shows that prior to the disturbance, the bus voltage  $V_2$  is stable at 270 V. As the disturbance voltage is imposed at simulation time of 4 ms, the bus voltage experiences oscillation and ringing which indicates instability in the system due to the interaction of the negative incremental input impedance of the CPL with the input filter.

Figure 3. LC Filter with CPL

Figure 4. Bus voltage as 50 V input voltage imposed.

#### 2. ANALYSIS

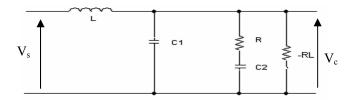

Although there is always some natural damping in the L-C filter due to the parasitic components such as equavalent series resistor in the inductor, normally it is not enough to damp instabilty. The schematic diagram with the insertion of RC passive damping network is shown in Figure 5. The series damping capacitor used to block DC thus prevent DC current from entering the

damping resistor. On the other hand, the damping resistor performs the damping function at filter resonant frequency. Figure 5 shows a constant power load (-R\_L) connected to the L-C\_1 filter with a RC\_2 passive damping network. The total effective resistance of this circuit is  $R_{\text{eff}},$  where  $R_{\text{eff}}$  can be written as  $R_{\text{eff}} = \frac{-RR_L}{R-R_L}$ . Based on stability criteria set by Middlebrook's[7], that is  $R < R_L$  for a system to be stable, the passive damping resistor

on stability criteria set by Middlebrook's[7], that is  $R < R_{\rm L}$  for a system to be stable, the passive damping resistor R has to be smaller than  $R_{\rm L}$  so that the total effective resistance will be positive. The output to the input voltage transfer function of Figure 5 is given in Equation (1).

Figure 5: LC Filter with CPL and passive damping network

$$\frac{V_{C}}{V_{S}} = \frac{\frac{(1+sC_{2}R)}{LC_{1}C_{2}R}}{s^{3} + s^{2} \left(\frac{C_{1}R_{L} + C_{2}R_{L} - C_{2}R}{C_{1}C_{2}RR_{L}}\right) + s\left(\frac{C_{2}RR_{L} - L}{LC_{1}C_{2}R_{L}R}\right) + \frac{1}{LC_{1}C_{2}R}}$$

(1)

By equating the denominator part of Equation (1) to zero, and rearranging this characteristic yields Equation (2).

$$-R = -\frac{1}{K} = \frac{s^2(LC_1R_L + LC_2R_L) - sL + R_L}{s^3LC_1C_2R_L - s^2LC_2 + sR_1C_2}$$

(2)

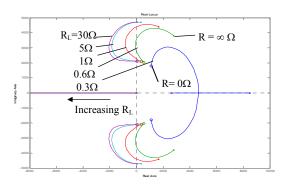

Equation (2) actually is a root locus plot where a parameter (R) can be adjusted so that the system poles can be located as a specific place in s-plane for stability purposes. The plot of pole movements as the damping resistor R varies is given in Figure 6. Parameters used are: L = 150uH,  $C_1$  = 300uF,  $C_2$  = 1.2mF and 5 different values of CPL resistance ( $R_L$ ) are 0.3  $\Omega$ , 0.6  $\Omega$ , 1  $\Omega$ , 5  $\Omega$  and 30  $\Omega$ . These values are equivalent to the CPL power level of 243 kW, 122 kW, 73 kW, 14.6 kW and 2.4 kW,

i.e

$$\left(R_L = \frac{V^2}{P}\right)$$

. The DC voltage source applied is 270 V.

Figure 6 indicates that the poles are in the right half plane for a damping resistor of zero and infinity. As the damping resistance varies between zero and infinity the poles move to the left, and may cross into the left-half plane, as in the case for  $R_L = 0.6~\Omega$  and above. With  $R_L = 0.3~\Omega$  the system remains unstable for all values of damping resistance, showing the limitation of the approximate stability condition derived earlier, namely  $R < |R_L|$ .

Figure 6: System poles movement with different R<sub>L</sub>

#### 3. DESIGN

The design procedures of obtaining the passive damping network is based on Equation (1). The characteristic equation is factorised as in Equation (3). Multiplied out Equation (3) yields Equation (4).

$$\left(s + \frac{1}{C_2 R}\right) \left(s^2 + s \frac{1}{C_2} \left[\frac{R_L - R}{R_L R}\right] + \frac{1}{LC_1}\right) = 0$$

(3)

$$s^{3}+s^{2}\!\!\left(\!\frac{C_{1}R_{L}\!+\!C_{2}(R_{L}\!-\!R)}{C_{1}C_{2}RR_{L}}\!\right)\!+\!s\!\!\left(\!\frac{C_{2}RR_{L}\!+\!\frac{L}{R}\!\left[\!R_{L}\!-\!R\right]\!\right)\!+\!\frac{1}{LC_{1}C_{2}R}\!=\!0\!\!\left(\!4\right)$$

By camparing Equation (1) and (4), an extra term  $s \frac{LR_L}{R}$  has appeared. In order to validate the Equation (1), term  $C_2RR_L >> \frac{LR_L}{R}$ . This condition creates a condition that is

$$C_2 \gg \frac{L}{R^2} \tag{5}$$

Therefore the design procedure is to choose R such that the effective resistance in the quadratic portion of Equation (3) provides satisfactory damping of the complex poles, then  $C_2$  must be chosen to ensure that equation 5 is satisfied. For example the design is to place the complex system poles on the 45-degree of theta angle ( $\theta$ ) in the s-plane, then the magnitudes of the real part and the imaginary part of the quadratic characteristic equation of Equation (3) must be equal. The damping resistor R is given as

$$R = \frac{R_{L}\sqrt{LC_{1}}}{\sqrt{LC_{1}} + \sqrt{2}C_{1}R_{L}}$$

(6)

Using the second order equation, the damping resistor in term of  $\theta$  angle can be presented as Equation (7)

$$R = \frac{R_L \sqrt{LC_1}}{2Cos\theta C_1 R_L + \sqrt{LC_1}}$$

(7)

Table 1 shows the values of R and  $C_2$  with the variation of  $\theta$ . The load resistance  $R_L$  used is 72.9  $\Omega$  (

typical 1000 W load ) with the supply voltage of 270 V and the  $C_1 = 150$  uF.  $C_2$  is obtained using equation  $C_2 = \frac{L}{R^2}$ .

Table 1. RC damping parameter with different poles

| θ (°) | $R(\Omega)$ | C <sub>2</sub> (mF) |

|-------|-------------|---------------------|

| 0°    | 0.351       | 1.211               |

| 10°   | 0.357       | 1.177               |

| 20°   | 0.374       | 1.073               |

| 30°   | 0.405       | 0.914               |

| 40°   | 0.458       | 0.715               |

| 50°   | 0.546       | 0.503               |

| 60°   | 0.700       | 0.306               |

| 70°   | 1.019       | 0.144               |

| 80°   | 1.981       | Very small          |

| 90°   | 72.9        | Very small          |

#### 4. RESULTS

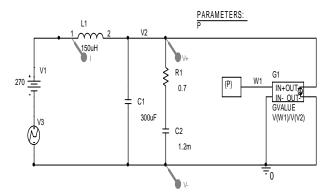

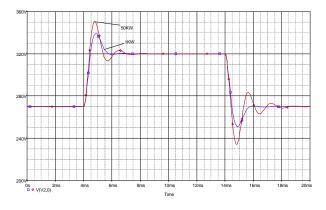

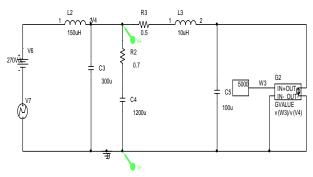

The schematic diagram for the PSpice simulation with RC passive damping network is shown in Figure 7. All the component values used are shown clearly. The RC damping network is represented as  $R_1$  and  $C_2$ . The source and L-C filter components are as previous section. The damping network was chosen to place the system complex poles on the  $60^{\circ}$  line in the complex plane. The values of damping resistor R are  $0.7~\Omega$  and a blocking capacitor  $C_2$  of 1.2~mF. The input voltage step signal is shown as  $V_3$ . The +50~V voltage transient is imposed at simulation time 4 ms, and at simulation time 14 ms, the transient is removed.

The simulation results for bus voltage for both CPL power level of 1 kW and 50 kW is shown in Figure 8. The plot shows that bus voltage experiences a single overshoot and then quickly settle to the new steady-state value 280 V, illustrating the effectiveness of the damping network. The system is well damped at low power level (1 kW) and experiences slightly oscillatory behavior as the power increased (50 kW).

Figure 7. Schematic diagram of RC damping, LC filter and CPL

Figure 8. Simulated bus voltage V<sub>2</sub>

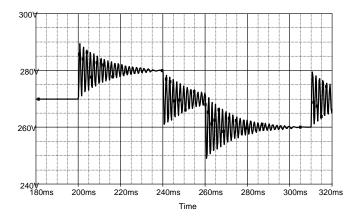

The effectiveness of the passive damper can be proven further. In this case, the CPL is connected to DC bus bar through a long cabling system. Typical components values for the cabling can be represented by the series R-L element [8]. This can be shown in Figure 9 where  $R_3$ - $L_3$ is the cable parameter. C<sub>5</sub> is a decoupling capacitor normally connected across CPL. The simulation results of the bus voltage without passive damping is shown in Figure 10, with CPL power level of 5 kW connected through. The plot shows that at simulation time of 200 ms, a +10V voltage transient was imposed for a 40 ms period of simulation. There is severe oscillatory response in the bus voltage. Likewise the same phenomena can be observed as the voltage step down -10V at 260 ms simulation time.

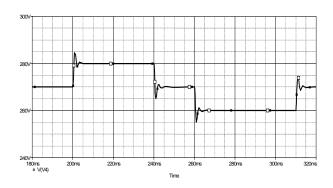

However with the insertion of the passive damping network, the problem of bus interaction and instability phenomena were eliminated. This is shown in the plot of Figure 11. The plot shows that at simulation time 200 ms, +10V voltage transient is imposed for a period of 40 ms, and at simulation time of 260 ms, a -10 V voltage transient is again imposed for the period of time of 50 ms. The plot shows that the system is well damped where the bus voltage experiences a single overshoot and then quickly settle to the steady-state value, illustrating the effectiveness of the damping network.

Figure 9. Schematic diagram with R-L cabling connected

Figure 10. Simulated bus voltage V<sub>2</sub> without passive damping

Figure 11. Simulated bus voltage V<sub>2</sub> with passive damping

## 5. CONCLUSION

The analysis, theoretical design and simulation of the RC damping network were examined extensively in a simple system consisting of LC filter and constant power load. Detail analysis and design of obtaining the damper components for CPL of 1 kW were given. The PSpice simulation results show the effectiveness of the designed passive damping network that satisfactorily maintained the DC bus bar from any oscillation due to the interaction of negative incremental impedance and LC filter. The simulation result also proved that the designed RC damping network could be further implemented for higher CPL power level of 5 kW.

#### REFERENCES

- [1] Gua, G. C, Tabisz, W. A, Leu, C. S, Dai, N, Watson, R. and Lee, F. C. "Development of A DC Distributed Power System," IEEE Applied Power Electronics Electronics Conference, APEC'94, pp.763-769, 1994.

- [2] W. A. Tabisz, Milan M. Jovanovic, F. C. Lee, "Present and Future of Distributed Power Systems," IEEE Applied Power Electronics Conference, APEC'92, pp. 11-18, Feb. 1992.

- APEC'92, pp. 11-18, Feb. 1992.

[3] Jusoh, A, "The instability Effect of Constant Power Loads". IEEE National Power and Energy Conference, PECon 04, Kuala Lumpur, 175-179, 2004.

- [4] M. Alfayyoumi, A. H. Nayfeh, and D. Borojevic, "Input Filter Interactions in DC-DC Switching Regulators," IEEE Power Electronic Specialists Conference, PESC'99, Vol. 2, pp. 926-932, 1999.

- [5] R. B. Ridley, B. H. Cho, F. C. Lee, "Analysis and Interpretation of Loop Gains of Multiloop-Controlled Switching Regulators," IEEE Transaction on Power Electronics, Vol. 3, No. 4, pp.489-498, Oct. 1988.

- [6] S. Chandrasekaran, D.K. Lindner and D. Boroyevich, "Analysis of Subsystem Integration in Aircraft Power Distribution System," IEEE International

- Symposium on Circuits & Systems, ISCAS'99, Vol. 5, pp. 82-85, May 1999.

- [7] R. D. Middlebrook, "Input Filter Considerations in Design and Application of Switching Regulators," IEEE Proceeding on Industry Application Society Annual Meeting, pp. 11-14, October 1976.

- [8] A. M. Cross, A. J. Forsyth, D. R. Trainer and N. Baydar, "Simulation of Power Quality Issues in MEA Actuator Supplies," EPE Power Electronics Conference, paper no. 183, Sept 2003.