# HIGH FIDELITY SIMULATION MODELS FOR EQUIPMENT PERFORMANCE PREDICTION IN SEMICONDUCTOR INDUSTRY

# ANWAR ALI BIN VALI MOHAMED

A dissertation submitted in partial fulfilment of the requirements for the award of the degree of

Doctor of Engineering (Engineering Business Management)

Razak School of Engineering and Advanced Technology

Universiti Teknologi Malaysia

To my beloved wife and children

#### ACKNOWLEDGEMENT

This dissertation was prepared while I am working full time researching and practicing what was written here. I would like to thank my employer for funding the Engineering Doctorate program fees and providing the necessary support and encouragement allowing me to convert my research and work into academic writing. In particular, my ex-manager, Mariam Jamal, who persuaded me to enroll into the doctorate program, my current manager, Dr. Thomas Rucker, who provided management encouragement so that I complete this program, and my mentor, Devadas Pillai, who reviewed the dissertation many times and always provided valuable inputs and motivation. I also want to thank all, especially Devadas Pillai and Jeffrey Pettinato, who were involved in the internal review and approval process allowing this dissertation to be published while making sure the company's policies on Intellectual Property are not violated.

I also wish to express my sincere appreciation to my academic advisor, Professor Dr. Awaluddin Mohd Shaharoum, who patiently waited for me to complete the dissertation write-up while providing guidance, critics, and encouragement. I am also grateful that my family members were able to bear the effect of doing doctorate while working full time. I hope this will provide encouragement to my first three children who are already pursuing tertiary education and my youngest who is still in secondary school.

#### **ABSTRACT**

Semiconductor manufacturing is a high-technology industry which is capital intensive and operationally complex with its process technology refreshed every two years. Precision in capacity planning is critical to ensure the right amount of capital equipment is purchased to match the demand while meeting aggressive cost and operational targets. The key input parameter for capacity calculations is the equipment output rate. As equipment get more complex, its output rate become difficult to predict using spreadsheets, thus the need for detailed dynamic equipment simulation models. However, literature on how to build detailed equipment simulation models for real-world is scarce. Practitioners do not share their experience openly due to proprietary reasons. This dissertation investigates the complexity of semiconductor manufacturing which makes its capacity planning difficult. The techniques to build, verify and validate high fidelity equipment simulation models were developed. The models are then used to augment capacity planning and productivity improvement decision making. Case studies are conducted using the models to improve capacity forecast planning accuracy for capital purchase decisions which resulted in million dollars capital avoidance, test equipment productivity improvement ideas and decide which ones have benefits to pursue, and determine the effect of different operator manning ratios for manufacturing execution decisions. The results show that raw model accuracy can be up to 99% using the methods described here. For manufacturing execution, model accuracy can be up to 95% due to variability in human performance, but good enough to provide insights on manning ratio strategies. The case studies demonstrate how the results directly contribute to company performance in terms of capital efficiency, capital expenditure avoidance, and waste reduction. It enables optimal equipment configuration decisions to be made upfront during technology development. It also earns credibility and senior management confidence in using such simulation models for decision making.

#### **ABSTRAK**

Pembuatan semikonduktor merupakan industri teknologi tinggi berintensif modal, tahap pengendalian yang kompleks serta mengalami pembaharuan teknologi proses setiap dwitahunan. Ketepatan perancangan kapasiti adalah penting untuk memastikan modal peralatan dibeli dapat dipadankan dengan permintaan serta sasaran kos dan operasi yang agresif tercapai. Parameter utama untuk pengiraan kapasiti ialah kadar keluaran peralatan. Peralatan yang semakin kompleks merumitkan penggunaan lembaran hamparan untuk meramal kadar keluaran. Justeru, model simulasi peralatan yang dinamik dan terperinci diperlukan. Sorotan kajian mengenai proses pembinaan model simulasi peralatan dunia nyata secara terperinci sukar didapati. Pengalaman pengamal-pengamal bidang berkaitan tidak dikongsi secara terbuka atas alasan harta milik intelektual. Disertasi ini mengkaji kerumitan yang dialami oleh pembuatan semikonduktor sehingga menyukarkan aktiviti perancangan kapasiti. Model simulasi peralatan fideliti tinggi dibina, ditentusah dan digunakan sebagai alat bantu di dalam membuat keputusan berkaitan peningkatan serta pembaikan perancangan kapasiti dan produktiviti. Penggunaan model simulasi di dalam beberapa kajian kes bertujuan untuk meningkatkan ketepatan ramalan keputusan kapasiti pembelian modal, menilai kebernasan ideaidea untuk meningkatkan produktiviti peralatan serta menentukan kesan nisbah pengendalian operator yang berbeza ke atas perlaksanaan keputusan berkaitan pembuatan. Keputusan menunjukkan ketepatan model asas sehingga 99% dengan menggunakan kaedah yang diterangkan di sini. Bagi pelakuan pembuatan, walaupun keragaman prestasi manusia menjadikan ketepatan model mencapai 95%, ia masih memadai untuk memberi gambaran awal kesan strategi nisbah pengendalian Keputusan yang diperolehi daripada kajian kes menunjukkan kesan operator. langsung ke atas prestasi syarikat dari aspek kecekapan modal, pengurangan perbelanjaan modal dan pembaziran. Segala keputusan yang melibatkan konfigurasi peralatan secara optimum boleh dibuat di sepanjang waktu teknologi dibangunkan. Hasil daripada model simulasi yang berkaitan turut berupaya meningkatkan kebolehpercayaan dan keyakinan pihak pengurusan atasan di dalam pembuatan keputusan.

# TABLE OF CONTENTS

| CH | APTE | TITLE                                       | PAGE |

|----|------|---------------------------------------------|------|

|    |      | DECLARATION                                 | ii   |

|    |      | DEDICATION                                  | iii  |

|    |      | ACKNOWLEDGEMENT                             | iv   |

|    |      | ABSTRACT                                    | v    |

|    |      | ABSTRAK                                     | vi   |

|    |      | TABLE OF CONTENTS                           | vii  |

|    |      | LIST OF TABLES                              | xiii |

|    |      | LIST OF FIGURES                             | xiv  |

|    |      | LIST OF ABBREVIATIONS                       | xvii |

|    |      | LIST OF APPENDICES                          | xix  |

| 1  | INT  | RODUCTION                                   | 1    |

|    | 1.1  | Prologue                                    | 1    |

|    | 1.2  | Research Background                         | 1    |

|    | 1.3  | Research Problem                            | 3    |

|    | 1.4  | Research Justification                      | 6    |

|    | 1.5  | Research Objectives                         | 7    |

|    | 1.6  | Research Scope                              | 8    |

|    | 1.7  | Organization of the Dissertation            | 8    |

| 2  | LIT  | ERATURE REVIEW                              | 11   |

|    | 2.1  | Introduction                                | 11   |

|    | 2.2  | Introduction to Semiconductor Manufacturing | 11   |

|   |      |                   |                      |                                                   | viii       |

|---|------|-------------------|----------------------|---------------------------------------------------|------------|

|   |      | 2.2.1             | Wafer P              | reparation                                        | 13         |

|   |      | 2.2.2             | Wafer F              | abrication                                        | 13         |

|   |      | 2.2.3             | Sort                 |                                                   | 15         |

|   |      | 2.2.4             | Die Prep             | paration                                          | 15         |

|   |      | 2.2.5             | Assemb               | ly                                                | 15         |

|   |      | 2.2.6             | Test                 |                                                   | 19         |

|   |      | 2.2.7             | Finish               |                                                   | 19         |

|   | 2.3  | The Co            | mplexity             | of Semiconductor Manufacturing                    | 20         |

|   | 2.4  | Capacit           | y Plannin            | g for Semiconductor Manufacturing                 | 23         |

|   | 2.5  | Using S<br>Comple |                      | n to Address Semiconductor Manufacturing          | 30         |

|   |      | 2.5.1             | Full Fac             | tory Simulation Modeling                          | 31         |

|   |      | 2.5.2             | Equipme              | ent Modeling                                      | 34         |

|   |      | 2.5.3             | AMHS                 | Simulation                                        | 36         |

|   |      | 2.5.4             | Combin               | ing Static Modeling, Simulation, and Optimization | 37         |

|   | 2.6  | Definiti          | on of Hig            | th Fidelity Simulation                            | 38         |

|   | 2.7  | Simulat           | ion Abstr            | raction                                           | 40         |

|   | 2.8  | Operato           | or Modeli            | ng                                                | 41         |

|   |      | 2.8.1             | DES So               | ftware Capability                                 | 44         |

|   |      |                   | 2.8.1.1              | Standard Downtime Modeling Techniques             | 44         |

|   |      |                   | 2.8.1.2              | Standard Operator Modeling Technique              | 45         |

|   | 2.9  | Generic           | Steps in             | Simulation Study                                  | 46         |

|   | 2.10 | Chapter           | Summar               | у                                                 | 50         |

| • | DEC  | E A D <i>C</i> H  |                      | anot ocy                                          | <b>5</b> 1 |

| 3 |      |                   |                      | ODOLOGY                                           | 51         |

|   | 3.1  | Introduc          |                      |                                                   | 51         |

|   | 3.2  |                   | udy Rese             |                                                   | 51         |

|   | 3.3  |                   | h Questio            |                                                   | 54         |

|   | 3.4  |                   | th Theory            |                                                   | 54         |

|   | 3.5  |                   | udy Desig            |                                                   | 55         |

|   |      | 3.5.1             | Step 1: 1<br>Equipme | Develop HFSME Methodology for Generic ent         | 55         |

|   |     | 3.5.2            | Step 2: Demonstrate HFSME Usage in Real World                                         | 56 |

|---|-----|------------------|---------------------------------------------------------------------------------------|----|

|   |     | 3.5.3            | Step 3: Extend HFSME to Comprehend Downtime and Operator Interactions                 | 56 |

|   |     | 3.5.4            | Step 4: Demonstrate Extended HFSME Usage in Real World                                | 57 |

|   | 3.6 | Mainta           | ining Confidentiality and IP                                                          | 58 |

|   | 3.7 | Softwa           | re Used                                                                               | 59 |

| 4 |     | SME ME<br>UIPMEN | ETHODOLOGY DEVELOPMENT FOR GENERIC                                                    | 61 |

|   | 4.1 | Introdu          | action                                                                                | 61 |

|   | 4.2 | Simula           | tion Abstraction Levels for Semiconductor Manufacturing                               | 61 |

|   | 4.3 | HFSM             | E Abstraction Levels                                                                  | 62 |

|   |     | 4.3.1            | Non-Moving Components                                                                 | 62 |

|   |     | 4.3.2            | Simple Delays                                                                         | 63 |

|   |     | 4.3.3            | Locations                                                                             | 64 |

|   |     | 4.3.4            | Simple Movement Systems                                                               | 64 |

|   |     | 4.3.5            | Complex Movement Systems                                                              | 66 |

|   | 4.4 | Phases           | of Simulation Study                                                                   | 67 |

|   | 4.5 | Steps in         | n HFSME                                                                               | 70 |

|   |     | 4.5.1            | Clarifying the Questions Simulation Needs to Answer and When the Answers are Required | 70 |

|   |     | 4.5.2            | Understand Data Availability and Modeling Assumptions                                 | 72 |

|   |     | 4.5.3            | HFSME Creation                                                                        | 72 |

|   |     |                  | 4.5.3.1 Model Decomposition, Abstraction, and Reuse                                   | 72 |

|   |     |                  | 4.5.3.2 Model Drawing                                                                 | 74 |

|   |     |                  | 4.5.3.3 Create Systems and Sub-Models                                                 | 74 |

|   |     | 4.5.4            | Data Collection                                                                       | 75 |

|   |     | 4.5.5            | Coding                                                                                | 75 |

|   |     |                  | 4.5.5.1 Create Input Data Files                                                       | 75 |

|   |     |                  | 4.5.5.2 Logic Coding                                                                  | 76 |

|   |     | 4.5.6            | Model Verification                                                                    | 77 |

|   |     | 4.5.7   | Model '   | Validation                                                             | 78  |

|---|-----|---------|-----------|------------------------------------------------------------------------|-----|

|   |     | 4.5.8   | Simulat   | ion Experimentation                                                    | 79  |

|   |     | 4.5.9   | Present   | ing Simulation Results and Recommendation                              | 80  |

|   | 4.6 | Case S  | tudy of G | eneric Equipment                                                       | 83  |

|   |     | 4.6.1   | Modelin   | ng Objectives                                                          | 83  |

|   |     | 4.6.2   | Modeli    | ng Assumptions                                                         | 83  |

|   |     | 4.6.3   | Model (   | Creation                                                               | 86  |

|   |     |         | 4.6.3.1   | Model Decomposition and Abstraction                                    | 86  |

|   |     |         | 4.6.3.2   | Model Drawing                                                          | 87  |

|   |     |         | 4.6.3.3   | Systems and Sub-Model Creation                                         | 89  |

|   |     | 4.6.4   | Data Co   | ollection                                                              | 95  |

|   |     |         | 4.6.4.1   | Movement Time from Equipment Log Files                                 | 95  |

|   |     |         | 4.6.4.2   | Movement Times from Video Time Study                                   | 95  |

|   |     |         | 4.6.4.3   | Movement Times from Equipment Design<br>Parameters                     | 98  |

|   |     | 4.6.5   | Control   | and Logic Coding                                                       | 98  |

|   |     | 4.6.6   | Model '   | Verification                                                           | 101 |

|   |     | 4.6.7   | Model '   | Validation                                                             | 102 |

|   |     | 4.6.8   | Simulat   | ion Experimentation                                                    | 103 |

|   | 4.7 | Chapte  | r Summa   | ry                                                                     | 104 |

| 5 | HFS | ME IM   | PLEME     | NTATION                                                                | 105 |

|   | 5.1 | Introdu | ction     |                                                                        | 105 |

|   | 5.2 | Validat | ion Teste | r Modeling and Analyses                                                | 105 |

|   |     | 5.2.1   | VT Mo     | deling Approach                                                        | 107 |

|   |     | 5.2.2   | VT Mo     | deling for Product 1                                                   | 109 |

|   |     |         | 5.2.2.1   | Model Validation                                                       | 109 |

|   |     |         | 5.2.2.2   | Simulation Experimentation: Determining Number of TCs                  | 111 |

|   |     |         | 5.2.2.3   | Validating Simulation Prediction                                       | 112 |

|   |     |         | 5.2.2.4   | Simulation Experimentation: Gantry Robot Pick<br>Logic Option Analysis | 113 |

|   |     | 5.2.3   | VT Modeling for Product 2                                                 | 114 |

|---|-----|---------|---------------------------------------------------------------------------|-----|

|   |     |         | 5.2.3.1 Model Validation                                                  | 114 |

|   |     |         | 5.2.3.2 Simulation Experimentation: Determining Optimal Number of TC      | 115 |

|   |     | 5.2.4   | Overall Benefits of VT Modeling                                           | 119 |

|   | 5.3 | Chip A  | Assembly Line Simulation and Analyses                                     | 120 |

|   |     | 5.3.1   | CAL Modeling Approach                                                     | 122 |

|   |     | 5.3.2   | Model Validation                                                          | 126 |

|   |     | 5.3.3   | Simulation Experimentation: Constraint Identification                     | 127 |

|   |     | 5.3.4   | Simulation Experimentation: Vary Printer Auto-Cleaning Interval           | 128 |

|   |     | 5.3.5   | Simulation Experimentation: SMD Placement Feeder Assignment               | 129 |

|   |     | 5.3.6   | Simulation Experimentation: Buffer between SMD Placement and IC Placement | 130 |

|   |     | 5.3.7   | Overall Benefits of CAL Modeling                                          | 132 |

|   | 5.4 | Chapte  | er Summary                                                                | 133 |

| 6 | EXT | rendei  | D HFSME                                                                   | 134 |

|   | 6.1 | Introdu | iction                                                                    | 134 |

|   | 6.2 | Modeli  | ing Requirements                                                          | 134 |

|   | 6.3 | Model   | Experimentation and Scenarios                                             | 136 |

|   | 6.4 | Equipn  | ment Description                                                          | 137 |

|   |     | 6.4.1   | Operational Description of a LAL                                          | 138 |

|   |     | 6.4.2   | Configurations of LAL                                                     | 138 |

|   |     | 6.4.3   | Equipment Interaction                                                     | 139 |

|   |     | 6.4.4   | Operator Interaction                                                      | 140 |

|   | 6.5 | Buildir | ng the LAL HFSME                                                          | 141 |

|   | 6.6 | Extend  | ling LAL HFSME                                                            | 143 |

|   |     | 6.6.1   | Downtime and Operator Modeling Framework                                  | 146 |

|   |     | 6.6.2   | Global Operators                                                          | 146 |

|   |     | 6.6.3   | Downtime Modeling of Each Line                                            | 149 |

|     |      |         |                                                                                          | xii       |

|-----|------|---------|------------------------------------------------------------------------------------------|-----------|

|     |      | 6.6.4   | Operator Modeling of Each Line                                                           | 154       |

|     |      | 6.6.5   | Managing Operators During Runtime                                                        | 158       |

|     | 6.7  | Model   | Verification and Validation                                                              | 161       |

|     | 6.8  | Simula  | tion Experimentation                                                                     | 162       |

|     |      | 6.8.1   | Using the Model to Quantify the Effect of Different<br>Operator Strategies for Factory A | 162       |

|     |      | 6.8.2   | Using the Model to Quantify the Effect of Different<br>Operator Strategies for Factory B | 165       |

|     | 6.9  | Chapter | r Summary                                                                                | 168       |

| 7   | CO   | NCLUSI  | ONS AND FUTURE RESEARCH                                                                  | 170       |

|     | 7.1  | Introdu | ction                                                                                    | 170       |

|     | 7.2  | Summa   | ary of Research Results                                                                  | 170       |

|     | 7.3  | Future  | Research                                                                                 | 173       |

| REF | ERE  | NCES    |                                                                                          | 175       |

| APP | ENDI | CES A - | C                                                                                        | 185 - 210 |

# LIST OF TABLES

| TABLE NO. | TITLE                                                       | PAGE |

|-----------|-------------------------------------------------------------|------|

| 1.1       | WinterSim papers from A/T in Malaysia                       | 5    |

| 2.1       | Summary of semiconductor manufacturing complexity           | 23   |

| 2.2       | Examples of FFSM application areas                          | 34   |

| 2.3       | High fidelity simulation transferable for medicine [63]     | 39   |

| 3.1       | Roadmap for developing theory using simulation methods [85] | 53   |

| 4.1       | Video frame-by-frame analysis                               | 97   |

| 4.2       | Video time study data                                       | 97   |

| 5.1       | Product 1 VT model validation 1                             | 110  |

| 5.2       | Product 1 VT model validation 2                             | 110  |

| 5.3       | Product 1 MTBT comparison using simulated test time         | 111  |

| 5.4       | Product 2 MTBT Comparison                                   | 115  |

| 5.5       | Product 3 and Product 4 main differences                    | 123  |

| 5.6       | CAL validation for Product 3                                | 126  |

| 5.7       | CAL validation for Product 4                                | 126  |

| 5.8       | SMD placement feeder assignment experimentation             | 130  |

| 6.1       | Operators and technicians definition                        | 148  |

| 6.2       | Break time definitions                                      | 148  |

| 6.3       | Resource definition for a line                              | 150  |

| 6.4       | Repair and Assist parameters                                | 153  |

| 6.5       | Time-based activities definition                            | 155  |

| 6.6       | Lot-based activities definition                             | 156  |

| 6.7       | Run-based activities definition                             | 156  |

| 6.8       | Lot setup activities definition                             | 157  |

| 7.1       | Summary of HFSME results                                    | 172  |

# LIST OF FIGURES

| FIGURE NO | TITLE                                                                                              | PAGE |

|-----------|----------------------------------------------------------------------------------------------------|------|

| 1.1       | Dissertation structure                                                                             | 10   |

| 2.1       | Semiconductor manufacturing high level process flow                                                | 12   |

| 2.2       | Front-end semiconductor manufacturing process flow adopted from Intel [19]                         | 14   |

| 2.3       | Wire bond Assembly Test process flow                                                               | 17   |

| 2.4       | Flip chip Assembly Test process flow                                                               | 18   |

| 2.5       | Assortment of different JEDEC tray densities [22]                                                  | 20   |

| 2.6       | Future manufacturing challenges by Pillai [23]                                                     | 21   |

| 2.7       | Planning levels and decisions, adapted from [26]                                                   | 24   |

| 2.8       | SEMI E10 breakdown of time [27]                                                                    | 25   |

| 2.9       | SEMI E10 basic state stack chart [28]                                                              | 26   |

| 2.10      | High level overview of semiconductor A/T capacity modeling                                         | 29   |

| 2.11      | Relationship between the effort to build the model and the quality of results, Peikert et al. [69] | 41   |

| 2.12      | The human performance modeling theoritical framework [76]                                          | 43   |

| 2.13      | Simulation steps by Law [79,80]                                                                    | 47   |

| 2.14      | Steps in simulation study by Banks et al. [61]                                                     | 48   |

| 2.15      | Real world and simulation world relationships with verification and validation by Sargent [81]     | 49   |

| 3.1       | Research methodology                                                                               | 58   |

| 3.2       | Inserting a new system into AutoMod model                                                          | 60   |

| 4.1       | Semiconductor manufacturing model abstraction levels                                               | 62   |

| 4.2       | HFSME abstraction levels                                                                           | 67   |

| 4.3       | Simulation fidelity requirement over equipment life cycle                                          | 68   |

| 4.4       | HFSME approach                                                                                     | 70   |

| 4.5       | Steps in HFSME study                                                                               | 82   |

| 4.6  | Media change over in flip chip assembly processes          | 85  |

|------|------------------------------------------------------------|-----|

| 4.7  | Simulation graphics of empty and fully loaded boats        | 86  |

| 4.8  | Block diagram of Media Transfer equipment                  | 86  |

| 4.9  | Model structure                                            | 87  |

| 4.10 | Scaled layout drawing used as outline                      | 88  |

| 4.11 | Rear view of completed drawing of Magazine Load and Unload | 88  |

| 4.12 | Robotics pick-and-place kinematics system                  | 89  |

| 4.13 | Kinematics setup                                           | 90  |

| 4.14 | Unload path mover system                                   | 91  |

| 4.15 | Unload conveyor system                                     | 91  |

| 4.16 | Model top view                                             | 93  |

| 4.17 | Model front view                                           | 94  |

| 4.18 | Model rear view                                            | 94  |

| 4.19 | A boat traveling to lane 1                                 | 99  |

| 4.20 | A boat traveling to lane 2                                 | 99  |

| 5.1  | Validation Tester block diagram                            | 106 |

| 5.2  | Front view of VT simulation model                          | 108 |

| 5.3  | Rear view of VT simulation model                           | 108 |

| 5.4  | Actual versus simulation MTBT                              | 111 |

| 5.5  | Required number of TCs based on various test times         | 112 |

| 5.6  | Simulation versus IE model and validation results          | 113 |

| 5.7  | Evaluating different handler search algorithms             | 114 |

| 5.8  | Actual versus simulation MTBT                              | 115 |

| 5.9  | Required TCs based on various test times                   | 116 |

| 5.10 | Product 2 VT UPH with 6.3% TC downtime                     | 117 |

| 5.11 | Product 2 VT UPH with 4.2% TC downtime                     | 118 |

| 5.12 | Product 2 VT UPH with 5.0% TC downtime                     | 118 |

| 5.13 | Product 2 VT UPH with 8.4% TC downtime                     | 119 |

| 5.14 | Product 2 VT UPH with 12.5% TC downtime                    | 119 |

| 5.15 | CAL block diagram                                          | 121 |

| 5.16 | Flip Chip Package with and without DSC [88]                | 123 |

| 5.17 | CAL HFSME structure                                        | 124 |

| 5.18 | CAL HFSME input parameters                                 | 125 |

| 5.19 | CAL constraint identification when running Product 3       | 127 |

| 5.20 | CAL constraint identification when running Product 4          | 128 |

|------|---------------------------------------------------------------|-----|

| 5.21 | Relative improvement due to increasing auto-cleaning interval | 129 |

| 5.22 | Location of buffer                                            | 130 |

| 5.23 | Product 3 UPH comparison without and with buffer              | 131 |

| 5.24 | Product 3 UPH improvement without and with buffer             | 131 |

| 5.25 | Product 4 UPH comparison without and with buffer              | 132 |

| 5.26 | Product 4 UPH improvement without and with buffer             | 132 |

| 6.1  | A typical flip chip LAL                                       | 138 |

| 6.2  | LAL-A configuration                                           | 139 |

| 6.3  | LAL-B configuration                                           | 139 |

| 6.4  | Two adjacent lines with some operator activities described    | 141 |

| 6.5  | LAL high-level HFSME structure                                | 142 |

| 6.6  | LAL HFSME                                                     | 143 |

| 6.7  | LAL functional area layout                                    | 145 |

| 6.8  | LAL composite model hierarchy                                 | 146 |

| 6.9  | Control points examples                                       | 151 |

| 6.10 | Watch dog timer concept for downtime modeling                 | 153 |

| 6.11 | Simulation input parameters and responses                     | 159 |

| 6.12 | LAL functional area simulation model for Factory A            | 160 |

| 6.13 | Effect of manning ratio to LAL-A                              | 163 |

| 6.14 | Effect of manning ratio to LAL-B                              | 164 |

| 6.15 | Travel and idle percentages of time                           | 165 |

| 6.16 | 2-line LAL functional area simulation model for Factory B     | 166 |

| 6.17 | Reducing ½ operator for LAL-C                                 | 167 |

| 6.18 | Reducing ½ operator for LAL-D                                 | 167 |

| 6.19 | Detailed equipment states for LAL-C                           | 168 |

| 6.20 | Detailed equipment states for LAL-D                           | 168 |

|      |                                                               |     |

## LIST OF ABBREVIATIONS

3D - Three-dimensional

A/T - Semiconductor Assembly and Test

AMHS - Automated material handling system

CAL - Chip Attach Line

DES - Discrete event simulation

DO - Direct observation

DRAM - Dynamic random-access memory

Fab - Semiconductor wafer fabrication plant

FC-BGA - Flip Chip Ball Grid Array

FFSM - Full factory simulation modeling

FOUP - Front Opening Unified Pod

HFSM - High fidelity simulation model(s)

HFSME - High fidelity simulation model(s)/modeling of equipment

HLA - High Level Architecture

HVM - High volume manufacturing

IC - Integrated circuits

IE - Industrial Engineer

ISMI - International Manufacturing Initiative

JEDEC - Joint Electron Devices Engineering Council

LAL - Lid Attach Line

MASM - Modeling and Analysis of Semiconductor Manufacturing

Laboratory

MHS - Material handling system

MILP - Mixed integer linear programming

MNC - Multinational companies

PCB - Printed circuit board

P&P - Pick-and-place (referring to robotics system end effector)

PR - Photoresist

Prep - Preparation (used in Wafer and Die Preparation)

SEC - Samsung Electronics Corp.

SEMATECH - Semiconductor Manufacturing Technology

SEMI - Semiconductor Equipment and Materials International

SME - Small and medium enterprise

SMT - Surface Mount Technology

TD - Technology Development

TPM - Total Productive Maintenance

UPH - Unit(s) per hour

USA - United States of America

UV - Ultra-violet

VT - Validation Tester

WinterSim - Winter Simulation Conference

# LIST OF APPENDICES

| APPENDIX | TITLE                                            | PAGE |

|----------|--------------------------------------------------|------|

|          |                                                  |      |

| A        | Complete Simulation Codes for Chapter 4          | 185  |

| В        | Simulation Codes for Managing Operators          | 190  |

| С        | Simulation Codes for Managing Equipment Downtime | 196  |

#### **CHAPTER 1**

### INTRODUCTION

# 1.1 Prologue

This research focuses on high fidelity simulation modeling of equipment (HFSME) in semiconductor manufacturing. The aim is to develop and apply HFSME methodology that can be used to accurately predict complex equipment capability, augmenting capacity planning and productivity improvement decisions in achieving capital equipment and operational efficiencies.

# 1.2 Research Background

Simulation is the imitation of the operation of real-world process or system over time [1] on a computer so that it can be used to study and predict the system when variables are changed. Simulation is a powerful tool for analysis of new system designs, retrofits to existing systems, and proposed changes to operating rules [2]. Some of the specific issues that simulation is used to address in manufacturing include determining the required quantity of equipment and personnel, performance evaluation such as throughput and bottleneck analyses, and evaluation of operational procedures such as production scheduling, inventory policies, control strategies, and reliability analysis [3].

In manufacturing and service industries, it is important to ensure that the capacity needed to setup manufacturing or services matches the demand. Unused excess capacity will lead to wasted equipment utilization while on the other hand

capacity shortage will lead to inability to meet demand, thus causing opportunity lost and factory congestion. Therefore, it is very important to have precise capacity model to determine the right amount of capacity required to support demand, especially for operations which require huge capital investment.

There are various methods to perform capacity planning depending on the operational complexity. For operations without much complexity, the easiest form of capacity planning can be done with spreadsheet models. For highly complex operations, capacity planning requires combination of discrete event simulation (DES) modeling, mathematical optimization, and data integration with enterprise systems. This is true for the industry of interest in this research – the highly complex semiconductor industry where silicon is used to fabricate the ubiquitous integrated circuits (IC) used in computers, communication devices, and electronics appliances.

Semiconductor manufacturing can be divided into wafer fabrication (fab), sort, die preparation (prep), assembly and test (A/T), the last two involving assembling dies into various package types and testing them. The cost of setting up a wafer fab with the latest technology is about 4 to 5 billion dollars [4,5], for plant, capital equipment cost, and collaterals. Despite the high cost, the technology can only last a few years as the number of transistors doubles approximately every two years based on Moore's law [6]. In other words, factory with newer process technology is required every two years. Thus, it is very important to determine the right amount of capital investment which will pay back within two years before the technology becomes obsolete.

Due to very high capital cost to setup wafer fab, simulation is widely used for strategic and operational decision making. Simulation is one of the major quantitative techniques used to understand a system, predict its capability, quantify improvement ideas, and provide valuable insights on where to focus and whether it makes sense to pursue the idea and understanding the trade-off. There was less focus for A/T since traditionally it costs about 10% of wafer fab. However, the cost to build and start an A/T factory has gone up as well, for example, it costs a billion dollar for Intel's latest A/T factory in Vietnam [7]. More than two third of the cost is capital expenditure for equipment. The complexity of A/T has increased due to miniaturization of die and packaging, thus requiring more mechanization and

automation instead of just relying on cheap operators for manual assembly. Having large A/T factories instead of many small factories helps improve efficiency.

The capital equipment purchased will be used to manufacture various types of products. Due to high complexity of the equipment, each product has its own robot speed, process recipe, form factor, and media density parameters. The equipment capability expressed in units per hour (UPH) will be product-specific. If spreadsheet model is used, its accuracy can only be determined after every different combination of input parameters is validated during initial production runs. This is a very tedious process since validation needs to be performed for all products. It cannot be done for new products which are still under development. If simulation model is used, it must be able to mimick the complexity of the equipment faithfully for all possible combinations of input parameters, hence the need for a very detailed and accurate equipment simulation model. The detailed simulation model needs be validated for existing products so that it can be used to predict equipment capability of existing and future products. Otherwise the simulation model will not be able to augment capacity modeling in increasing its accuracy.

This research is about real-world application of how HFSME was successfully developed and used to augment enterprise capacity planning system and productivity decisions, enabling precise capacity planning of A/T factories resulting in millions of dollars savings achieved through capital equipment avoidance. The simulation team has developed and applied state-of-the art techniques for detailed and faithful modeling of highly complex equipment. The methods developed here can be generalized and applied to many other industries using moderate to highly complex equipment.

# 1.3 Research Problem

There are many research and publications on using factory simulations and mathematical models for semiconductor manufacturing capacity planning. These will be described in Chapter 2. Unfortunately, there was not much focus on how to get accurate input data into the capacity models such as equipment processing time

or UPH. The equipment UPH must be understood well and accurately quantified for various run conditions before it can be used as input to the capacity models, regardless of how novel the methods used in the capacity modeling. Otherwise, the capacity calculations will be inaccurate, resulting in coarse estimates and leading to risky decision making.

Detailed equipment simulation modeling can be used to generate various UPH responses for various equipment run conditions. However, publications on detailed equipment modeling are scarce compared to full factory simulation modeling (FFSM). Most of the publications on equipment modeling come from industry practitioners but the modeling methods applied were shared at high level only. For academic research on wafer fab, there are various data provided by industry such as the Intel Five-Machine Six Step Mini-Fab [8] and other datasets made available by Modeling and Analysis of Semiconductor Manufacturing Laboratory (MASM Lab) of Arizona State University [9]. The Semiconductor Manufacturing Technology (SEMATECH) International Manufacturing Initiative (ISMI) provides sample working models for wafer fab FFSM using AutoSched AP (ASAP) and automated material handling system (AMHS) using AutoMod [10], both software from Applied Materials. However, there is no sample model for any semiconductor equipment modeling.

The literatures reviewed show that the application of DES in A/T is not as widespread and common as in wafer fab. Based on proceedings from Winter Simulation Conference (WinterSim) from 2001 to 2012 where most of the semiconductor manufacturing simulation practices are shared, the number of papers presented on A/T or back-end manufacturing of semiconductor is less than 10% of papers presented on wafer fab. Given that there are many semiconductor A/T factories operating in Malaysia, the number of papers from Malaysia is negligible compared to United States of America (USA), Singapore, Korea, and Taiwan. There are only a handful of papers from Malaysia as summarized in Table 2.1. "Malaysia" keyword search in WinterSim archive from 1968 to 2012 returns 25 hits from 11 articles, most of them referring to authors who originated from Malaysia and doing research in other countries.

Table 2.1 WinterSim papers from A/T in Malaysia

| Year | Authors                                                                    | Topic                                                                                |

|------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 2001 | McAllister, Altuntas,<br>Frank (Penn State U),<br>Potoradi (Infineon) [11] | Infineon Melaka A/T factory modeling of scheduled maintenance strategy               |

| 2001 | Rosen, Geist, Finke,<br>Nanda, Barton (Penn State<br>U) [12]               | Infineon Melaka A/T factory burn-in process modeling using graphical methods         |

| 2002 | Potoradi, Boon (Infineon),<br>Mason (UoA), Fowler,<br>Pfund (ASU) [13]     | Infineon Melaka A/T factory simulation-<br>based scheduling for lot release planning |

| 2007 | Ong (Intel) [14]                                                           | Intel Malaysia A/T factory establishing man-machine ratio using simulation           |

Most of the technology companies headquartered in California, USA have its presence in Malaysia, especially Penang, which is dubbed as the silicon valley of Asia. This research will not try to study the reasons why there are only a few publications on simulation modeling from Malaysia indicating lack of simulation modeling practices in semiconductor factories based in Malaysia. For some companies, simulation analyses are performed by centralized team located at the company's headquarter outside of Malaysia. The Malaysia factory team will take the recommendation from simulation analysis and implement the idea, but will not have the knowledge and skills on how to perform simulation modeling and analysis.

Finally, this research is also trying to address the lack of knowledge sharing on how to develop and apply very detailed DES models for semiconductor manufacturing equipment, not just for A/T, but for wafer fab equipment modeling as well. There are experts in equipment modeling in various companies, but the knowledge and methods may be treated as company's intellectual property (IP), thus the lack of knowledge sharing. When a new engineer is hired into simulation organization, even after attending basic and advanced simulation classes, the new engineer needs to be trained and coached internally before the person can do the job. Without proper coaching, the reference for examples of equipment models is from AutoMod demonstration models. Unfortunately, only 1 out of the 16 demonstration models has the fidelity that is required. However, it was developed using the old

AutoMod version requiring low-level C programming. Without the proper documented methodology, standardizing modeling technique will be a challenge for in-house simulation team and create issues with model reusability and sustaining. Each simulation engineer will end up developing own approach in modeling instead of adopting a standardized method. As described by Shannon [15], the process of conducting a simulation study requires both art and science. Simulation modeling is an art that requires specialized training and therefore the practitioners' skill levels vary widely.

#### 1.4 Research Justification

It was described earlier that semiconductor manufacturing is highly capital intensive costing up to a billion dollar for A/T and four to five billion dollars for wafer fab plants. Since equipment output rate is the key input parameter to capacity planning system when making strategic and tactical decisions, it is necessary to ensure the values are accurate. The use of HFSME makes this possible to achieve. The methods developed in this research can be generalized for other similar industries such as electrical and electronic products manufacturing.

Electrical and electronic products continue to be Malaysia's largest export. Based on Ministry of International Trade and Industry statistics [16], the export of electrical and electronic products is 34.4% of total export, far exceeding the other major categories such as palm oil (9.3%), liquid natural gas (LNG, 7.2%), and chemicals and chemical product (6.8%). Manufacturing sector generates employment for 1 million people. Manufacturing sector also created business opportunities for small and medium enterprise (SME) in supporting the ecosystem such as building construction and maintenance, precision tooling, equipment supply and maintenance, transportation, and human resource training and development. Some of the mature SME ended up supporting and exporting their products to the multinational companies (MNC) worldwide. Without manufacturing sector's presence, the SME will not be able to learn and grow to the current level.

Penang has the highest foreign direct investment in 2010 and 2011, mainly driven by investment of high technology companies. However, investors also consider other emerging markets such as Vietnam and Indonesia as their cost of manufacturing is lower with abundance of cheap operator. Due to that, it's important for Malaysia to strive productivity improvement to remain competitive despite the cost disadvantage.

Simulation is one of the key scientific methods to improve manufacturing's productivity. If the application of simulation is more widespread in manufacturing and service sectors, more productivity and efficiency can be achieved. This will help Malaysia to remain competitive with the use of knowledge workers and using science in improving operations of manufacturing and services.

There are many simulation practitioners around the world, including for semiconductor industry. The simulation consultants who present tutorials during simulation conferences share generalized techniques for modeling to cater for broad range of audience, mainly academic researchers and students. Also, their motive of sharing is to market their product superiority. The simulation practitioners who work in semiconductor manufacturing companies and its related ecosystem such as equipment suppliers have expertise in simulation modeling but are not sharing the experience, most likely due to confidentiality and IP. Thus, if someone tries to look for "a guide for dummies" how to develop and apply detailed equipment simulation models, there is none available. Even the practitioner's handbook by Chung [17] covers only the basic modeling techniques.

## 1.5 Research Objectives

The research aim is to develop and apply HFSME methodology to accurately predict complex equipment capability, augmenting capacity planning and productivity improvement decisions in achieving capital equipment and operational efficiencies. The research objectives of the dissertation are as follow:

- a) Develop HFSME methodology for use in predicting complex equipment capability accurately.

- b) Demonstrate HFSME to augment A/T capacity planning system and show how it solves the inaccuracy problem when calculating equipment capability using spreadsheet models.

- c) Demonstrate HFSME for use in equipment productivity improvement decision making, which include quantifying the impact of improvement ideas and recommending which ideas to pursue.

- d) Develop methodology to extend HFSME so that operational considerations such as equipment interrupts and operator interactions can be comprehended faithfully. Demonstrate the extended HFSME methodology for use in manufacturing planning and execution decision making.

## 1.6 Research Scope

The scope of research is for semiconductor manufacturing, specifically A/T. It covers from technology development (TD) to high volume manufacturing (HVM). It will be shown that the objectives can be achieved through case studies of real-world industry problems and how the HFSME results directly contribute to the company's performance by eliminating the need to purchase additional capital equipment costing millions of dollars. The scope also includes developing the guidelines on how to apply HFSME in real world.

# 1.7 Organization of the Dissertation

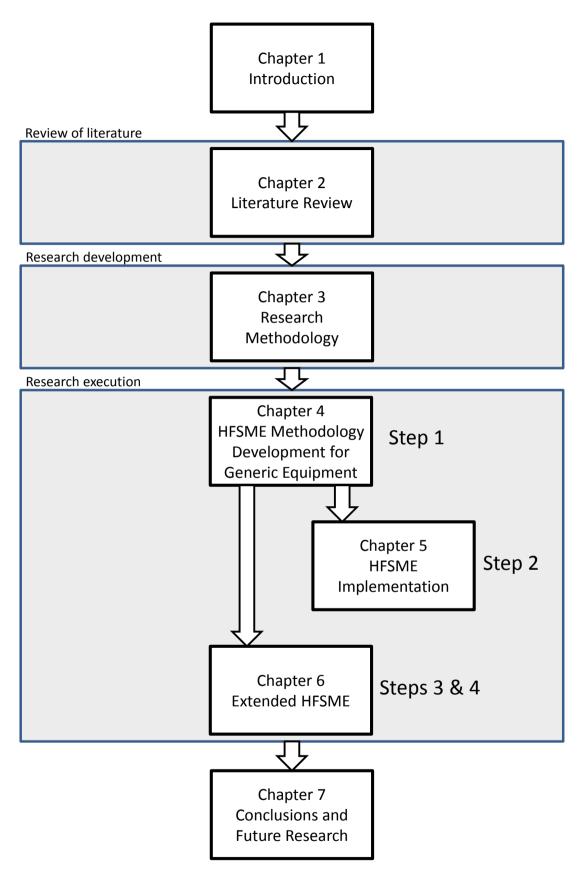

This dissertation is organized as follows and summarized in Figure 2.1. Chapter 2 provides an overview of semiconductor manufacturing process flows and a background of different types of simulation used in semiconductor manufacturing. Literature reviews are done mainly in this chapter and supplemented in subsequent

chapters. Chapter 3 briefly summarizes the problem statement from literature reviews and outlines the research methodology. Chapter 4 describes how detailed equipment simulation models are developed and used to answer various questions on equipment capability, an extension of a conference proceeding paper jointly written by the simulation team [18]. It includes a detailed guide of how a detailed equipment simulation model for a generic linked-equipment is developed. Chapter 5 provides a few case studies on how HFSME are developed and used to drive capital reduction and productivity decisions. Chapter 6 describes how HFSME is extended to include equipment downtime and operator interactions, followed by case studies of its usage in manufacturing execution decisions. Chapter 7 concludes the research and suggests future research areas.

Figure 2.1 Dissertation structure

#### REFERENCES

- 1. Banks, J. Introduction to Simulation. *Proceedings of the 2000 Winter Simulation Conference*, Orlando, Florida, 2000; 9-16.

- 2. Carson, J. S. Introduction to Modeling and Simulation. *Proceedings of the Winter Simulation Conference*, New Orleans, Louisiana, 2003; 7-13.

- 3. Law, A. M.; McComas, M. G. Simulation of Manufacturing Systems.

Proceedings of the 1997 Winter Simulation Conference, Atlanta, Georgia, 1997; 86-89.

- 4. Intel. Intel to Invest More than \$5 Billion to Build New Factory in Arizona. <a href="http://newsroom.intel.com/community/intel\_newsroom/blog/2011/02/18/intel\_to-invest-more-than-5-billion-to-build-new-factory-in-arizona">http://newsroom.intel.com/community/intel\_newsroom/blog/2011/02/18/intel\_to-invest-more-than-5-billion-to-build-new-factory-in-arizona</a> (accessed May 1, 2012).

- 5. Mokhoff, N. Samsung proceeding to expand Austin fab.

<a href="http://www.eetimes.com/electronics-news/4403432/Samsung-proceeding-to-expand-Austin-fab">http://www.eetimes.com/electronics-news/4403432/Samsung-proceeding-to-expand-Austin-fab</a> (accessed Dec 26, 2012).

- 6. Moore, G. E. Cramming more components into integrated circuits. *Electronics Magazine*, 1965.

- 7. Intel. Intel Expands Investment in Vietnam.

<a href="http://www.intel.com/pressroom/archive/releases/2006/20061110corp.htm">http://www.intel.com/pressroom/archive/releases/2006/20061110corp.htm</a>

(accessed May 1, 2012).

- 8. Kempf, K. Intel Five-Machine Six Step Mini-Fab Description. <a href="http://aar.faculty.asu.edu/research/intel/papers/fabspec.html">http://aar.faculty.asu.edu/research/intel/papers/fabspec.html</a>.

- Arizona State University. Modeling and Analysis for Semiconductor

Manufacturing Laboratory. <a href="http://masmlab.engineering.asu.edu/home.htm">http://masmlab.engineering.asu.edu/home.htm</a>.

- 10. International Sematech Manufacturing Initiative. Fab Simulation Models. <a href="http://ismi.sematech.org/modeling/simulation/index.htm">http://ismi.sematech.org/modeling/simulation/index.htm</a>.

- 11. McAllister, C. D.; Altuntas, B.; Frank, M.; Potoradi, J. Implementation of Response Surface Methodology Using Variance Reduction Techniques in Semiconductor Manufacturing. *Proceedings of the 2001 Winter Simulation Conference*, Arlington, Virginia, 2001; 1225-1230.

- 12. Rosen, S. L.; Geist, C. A.; Finke, D. A.; Nanda, J.; Barton, R. R. Graphical Methods for Robust Design of a Semiconductor Burn-In Process. *Proceedings* of the 2001 Winter Simulation Conference, Arlington, Virginia, 2001; 1231-1237.

- 13. Potoradi, J.; Ong, S. B.; Mason, S. J.; Fowler, J. W.; Pfund, M. E. Using Simulation-Based Scheduling to Maximize Demand Fulfillment in a Semiconductor Assembly Facility. *Proceedings of the 2002 Winter Simulation Conference*, Piscataway, New Jersey, 2002; 1857-1861.

- 14. Ong, H. H. Establishing Man-Machine Ratio Using Simulation. *Proceedings of the 2007 Winter Simulation Conference*, Washington D.C., 2007; 1663-1666.

- 15. Shannon, R. E. Introduction to the Art and Science of Simulation. *Proceedings* of the 1998 Winter Simulation Conference, Piscataway, New Jersey, 1998; 7-14.

- 16. Ministry of International Trade and Industry. Exports by Major Products, 2011. <a href="http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689">http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689</a> <a href="http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689">http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689</a> <a href="http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689">http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689</a> <a href="http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689">http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689</a> <a href="http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689">http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689</a> <a href="http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689">http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689</a> <a href="http://www.miti.gov.my/cms/content.jsp?id=com.tms.cms.article.Article\_dc689">http://www.miti.gov.my/cms/content.jsp?id=com.tms.article.Article\_dc689</a> <a href="http://www.miti.gov.my/cms/content.jsp?id=com.tms.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.article.ar

- 17. Chung, C. A. Simulation Modeling Handbook: A Practical Approach; CRC Press LLC: Boca Raton, Florida, 2004.

- 18. Yeoh, H.Y.; Ali, A.; Yeoh, E.P.; Lam, W.F.; Mohideen, S. High Fidelity Simulation Models for Accurate Equipment Performance Prediction. *Advanced Semiconductor Manufacturing Conference*, Stressa, Italy, 2007; 384-389.

- 19. Public Relations, Intel. From Sand to Silicon the Making of a Chip. <a href="http://newsroom.intel.com/docs/DOC-2476">http://newsroom.intel.com/docs/DOC-2476</a> (accessed June 3, 2013).

- 20. Rivera, J.; Meulen, R. v.d. Worldwide Semiconductor Revenue Declined 2.6 Percent in 2012, According to Final Results by Gartner. <a href="http://www.gartner.com/newsroom/id/2405215">http://www.gartner.com/newsroom/id/2405215</a> (accessed June 3, 2013).

- 21. Ford, D. Qualcomm Rides Wireless Wave to Take Third Place in Global Semiconductor Market in 2012. <a href="http://www.isuppli.com/Semiconductor-Value-Chain/News/Pages/Qualcomm-Rides-Wireless-Wave-to-Take-Third-Place-in-Global-Semiconductor-Market-in-2012.aspx">http://www.isuppli.com/Semiconductor-Value-Chain/News/Pages/Qualcomm-Rides-Wireless-Wave-to-Take-Third-Place-in-Global-Semiconductor-Market-in-2012.aspx</a> (accessed June 3, 2013).

- 22. Free Word Trade Center.

<a href="http://www.freewtc.com/images/products/ic\_trays\_9\_18162.jpg">http://www.freewtc.com/images/products/ic\_trays\_9\_18162.jpg</a> (accessed June 4, 2013).

- 23. Pillai, D. The Future of Semiconductor Manufacturing. *IEEE Robotics & Automation Magazine*, December 2006, 16-24.

- 24. Fowler, J. F.; Rose, O. Grand Challenges in Modeling and Simulation of Complex Manufacturing Systems. *SIMULATION* 2004, *80* (9), 469-476.

- 25. Kiran, A. S.; Kaplan, C.; Unal, T. A. Simulation of Electronics Manufacturing and Assembly Operations: A Survey. *Proceedings of the 1993 Winter Simulation Conference*, Los Angeles, California, 1993; 773-779.

- 26. Arnold, J.R. T.; Chapman, S. N. *Introduction to Materials Management;* Pearson Prentice Hall: New Jersey, 2004.

- 27. Dilorio, S. SEMI Equipment Performance Standards Integration, 2006.

<a href="http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5">http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5</a>

<a href="http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5">http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5</a>

<a href="http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5">http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5</a>

<a href="http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5">http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5</a>

<a href="http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5">http://dom.semi.org/web/wstandards.nsf/211ED72C1CACF054882571A7000E5</a>

- 28. Pomorski, T. SEMI E10 Specification for Equipment Reliability, Availability and Maintainability. <a href="http://www.semi.org/en/standards/ctr\_031244">http://www.semi.org/en/standards/ctr\_031244</a> (accessed June 10, 2013).

- 29. Gent, N.; Jiang, Z. A Review on Medium Capacity Planning for Semiconductor Wafer Fabrication. *IEEE International Conference on Systems, Man, and Cybernetics*, Montreal, Quebec, 2007.

- 30. Wu, D. S.; Erkoc, M.; Karabuk, S. Managing Capacity in the High-Tech Industry: A Review of Literature. *The Engineering Economist* 2005, *50*, 125-158.

- 31. Occhino, T. J. Capacity Planning Model: The Important Inputs, Formulas, and Benefits. *IEEE/SEMI Advanced Semiconductor Manufacturing Conference*, Boston, Massachusetts, 2000; 455-458.

- 32. Witte, J. D. Using Static Capacity Modeling Techniques in Semiconductor Manufacturing. *IEEE/SEMI Advanced Semiconductor Manufacturing Conference*, Cambridge, Massachusetts, 1996; 31-35.

- 33. Etman, L.F.P.; Veeger, C.P.L.; Lefeber, E.; Adan, I.J.B.F.; Rooda, J.E. Aggregate Modeling of Semiconductor Equipment Using Effective Process Times. *Proceedings of the 2011 Winter Simulation Conference*, Phoenix, Arizona, 2011; 1790-1802.

- 34. Hopp, W. J.; Spearman, M. L. Factory Physics: Foundations of Manufacturing Management, 3rd edition; IRWIN/McGraw-Hill: New York, 2008.

- 35. Catay, B.; Erenguc, S. S.; Vakharia, A. J. Tool capacity planning in semiconductor manufacturing. *Computer & Operations Research* 2003, *30*, 1349-1366.

- 36. Swaminathan, J. M. Tool capacity planning for semiconductor fabrication facilities under demand uncertainty. *European Journal of Operations Research* 2000, *120*, 545-558.

- 37. Habla, C.; Monch, L. Solving Volume and Capacity Planning Problems in Semiconductor Manufacturing: A Computational Study. *Proceedings of the 2008 Winter Simulation Conference*, Miami, Florida, 2008; 2260-2266.

- 38. Wang, K.-J.; Wang, S.-M. Simultaneous resource portfolio planning under demand and technology uncertainty in the semiconductor testing industry. *Robotics and Computer-Integrated Manufacturing* 2013, *29*, 278-287.

- 39. Sweat, S.; Niu, S.; Zhang, M. T.; Zhang, Z.; Zheng, L. Multi-factory capacity planning in semiconductor assembly test manufacturing with multiple-chip products. *Proceeding of the 2006 IEEE International Conference on Automation Science and Engineering*, Shanghai, China, 2006.

- 40. Ali, A.; Campbell, W. J.; Solomon, I. L.; Walsh, A. M.; Wuerfel, R. J. Intel's Process for Capacity Planning Optimization. *Intel Technology Journal* 2005, *9* (3), 211-221.

- 41. Smith, J. S. Survey on the Use of Simulation for Manufacturing System Design and Operation. *Journal of Manufacturing Systems* 2003, 22 (2), 157-171.

- 42. Bodner, D. A.; McGinnis, L. F. A Structured Approach to Simulation Modeling of Manufacturing Systems. *Proceedings of the 2002 Industrial Engineering Research Conference*, Orlando, Florida, 2002.

- 43. Jain, S.; Chan, S. Experiences with Backward Simulation Based Approaches for Lot Release Planning. *Proceedings of the 1997 Winter Simulation Conference*, Atlanta, Georgia, 1997; 773-780.

- 44. Chang, Y. S.; Choe, S. H.; Besant, C. B. Discrete Event Simulation in a Semiconductor Assembly Area. *Proceedings of the 1997 5th International Conference on FACTORY 2000 the Technology Exploitation Process*, Cambridge, 1997; 183-188.

- 45. Godding, G.; Sarjoughian, H.; Kempf, K. Application of Combined Discrete-Event Simulation and Optimization Models in Semiconductor Enterprise Manufacturing Systems. *Proceedings of the 2007 Winter Simulation Conference*, Washington D.C., 2007; 1729-1736.

- 46. Brown, S.; Domaschke, J.; Leibl, F. 'No Cost' Applications for Assembly Cycle Time Reduction. *Proceedings of the 1999 International Conference on Semiconductor Manufacturing Operational Modeling and Simulation*, San Francisco, California, 1999.

- 47. Brown, S.; Domaschke, J.; Leibl, F. Cycle Time Reductions for Test Area Bottleneck Equipment. *Proceedings of the Second Annual SEMI Test, Assembly, and Packaging Automation and Integration Conference*, Mesa, Arizona, 1998; B1-B5.

- 48. Sivakumar, A. I.; Chong, C. S. A simulation based analysis of cycle time distribution, and throughput in semiconductor backend manufacturing. *Computers in Industry* 2001, *45*, 59-78.

- 49. Pillai, D. D.; Bass, E. L.; Dempsey, J. C.; Yellig, E. J. 300-mm Full-Factory Simulations for 90- and 65-nm IC Manufacturing. *IEEE Transactions on Semiconductor Manufacturing* 2004, *17* (3), 292-298.

- 50. Mauer, J. L.; Schelasin, R. E.A. The Simulation of Integrated Tool Performance in Semiconductor Manufacturing. *Proceedings of the 1993 Winter Simulation Conference*, Los Angeles, California, 1993; 814-818.

- 51. Mauer, J.; Schelasin, R. Using Simulation To Analyze Integrated Tool Performance in Semiconductor Manufacturing. *Microelectronic Engineering* 1994, 25, 139-146.

- 52. Gupta, A. K.; Lendermann, P.; Sivakumar, A. I.; Priyadi, J. Simulation Analysis of Cluster Tool Operations in Wafer Fabrication. *Proceedings of the 2008 Winter Simulation Conference*, Miami, Florida, 2008; 2141-2147.

- 53. Park, K.; Morrison, J. R. Cluster Tool Design Comparison via Simulation. *Proceedings of the 2011 Winter Simulation Conference*, Phoenix, Arizona, 2011; 1872-1882.

- 54. Kohn, R.; Noack, D.; Mosinki, M.; Zhou, Z.; Rose, O. Evaluation of Modeling, Simulation and Optimization Approaches for Work Flow Management in Semiconductor Manufacturing. *Proceedings of the 2009 Winter Simulation Conference*, Austin, Texas, 2009; 1592-1600.

- 55. Jarugumilli, S.; Fu, M.; Keng, N.; DeJong, C.; Askin, R.; Fowler, J. Framework for Execution Level Capacity Allocation Decisions for Assembly Test Facilities Using Integrated Optimization Simulation Models. *Proceedings of the 2008 Winter Simulation Conference*, Miami, Florida, 2008; 2292-2297.

- 56. Leachman, R. C.; Kang, J.; Lin, V. SLIM: Short Cycle Time and Low Inventory in Manufacturing at Samsung Electronics. *INTERFACES* 2002, *32* (1), 61-77.

- 57. Merriam Webster Online. "high fidelity". <a href="http://www.merriam-webster.com/dictionary/high%20fidelity">http://www.merriam-webster.com/dictionary/high%20fidelity</a> (accessed April 7, 2013).

- 58. Oxford Dictionaries. "high fidelity".

<a href="http://oxforddictionaries.com/definition/english/high+fidelity">http://oxforddictionaries.com/definition/english/high+fidelity</a> (accessed April 7, 2013).

- 59. Hays, R. T. *Simulator Fidelity: A Concept Paper;* Technical Report; US Army Research Institute for the Behavioral and Social Sciences: Alexandria, Virginia, 1980.

- 60. Gross, D. C. Report from the Fidelity Implementation Study Group; Reference Document; Simulation Interoperability Standards Organization: Orlando, Florida, 1999.

- 61. Banks, J.; Carson, J. S.; Nelson, B. L.; Nicol, D. M. *Discrete-Event System Simulation, 3rd Edition;* Prentice Hall: New Jersey, 2000.

- 62. McFetrich, J. A structured literature review on the use of high fidelity patient simulators for teaching in emergency medicine. *Emergency Medicine Journal* 2006, 23 (7), 509-511.

- 63. Carron, P.-N.; Trueb, L.; Yersin, B. High-fidelity simulation in the nonmedical domain: practices and potential transferable competencies for the medical field. *Advances in Medical Education and Practice* 2011, 2, 149-155.

- 64. Frantz, F. K. A Taxonomy of Model Abstraction Techniques. *Proceedings of the* 1995 Winter Simulation Conference, Arlington, Virginia, 1995; 1413-1420.

- 65. Sisti, A. F.; Farr, S. D. Model abstraction techniques: an intuitive overview. Aerospace and Electronics Conference. NAECON 1998, Dayton, Ohio, USA, 1998; 447-450.

- 66. Benjamin, P.; Erraguntla, M.; Delen, D.; Mayer, R. Simulation Modeling at Multiple Levels of Abstraction. *Proceedings of the 1998 Winter Simulation Conference*, Washington DC, 1998; 391-398.

- 67. Vasudevan, K.; Lote, R.; Williams, E.; Ulgen, O. High Speed Bottle Manufacturing Lines: Case Studies and Simulation Software Selection Techniques. *Proceedings of the 2009 Winter Simulation Conference*, Austin, Texas, 2009; 322-332.

- 68. Vasudevan, K.; Devikar, A. Selecting Simulation Abstraction Levels in Simulation Models of Complex Manufacturing Systems. *Proceedings of the 2011 Winter Simulation Conference*, Phoenix, Arizona, 2011; 2268-2277.

- 69. Peikert, A.; Thoma, J.; Brown, S. A Rapid Modeling Technique for Measurable Improvements in Factory Performance. *Proceedings of the 1998 Winter Simulation Conference*, Washington DC, 1998; 1011-1015.

- 70. Baum, S. S.; O'Donnell, C. S. An Approach to Modeling Labor and Machine Down Time in Semiconductor Fabrication. *Proceedings of the 1991 Winter Simulation Conference*, Phoenix, Arizona, 1991; 448-454.

- 71. Meyersdorf, D.; Biron, O.; Ozelkan, E. C.; Fowler, J. W. Staffing Analysis Tool for Operator-Machine-Lot Interference in Semiconductor Manufacturing. 1997 IEEE/SEMI Advanced Semiconductor Manufacturing Conference, Cambridge, Massachusetts, 1997; 335-340.

- 72. Chen, H.-N.; Dabbas, R. Modeling Staffing Requirements within a Semiconductor Manufacturing Environment. 2002 IEEE/SEMI Advanced Semiconductor Manufacturing Conference, Boston, Massachusetts, 2002; 234-239.

- 73. Mosley, S. A.; Teyner, T.; Uszoy, R. M. Maintenance Scheduling and Staffing Policies in a Wafer Fabrication Facility. *IEEE Transaction on Semiconductor Manufacturing* 1998, *11* (2), 316-323.

- 74. Baines, T.; Mason, S.; Siebers, P.-O.; Ladbrook, J. Humans: the missing link in manufacturing simulation? *Simulation Modelling Practice and Theory* 2004, *12*, 515-526.

- 75. Mason, S.; Baines, T.; Kay, J. M.; Ladbrook, J. Improving the Design Process for Factories: Modeling Human Performance Variation. *Journal of Manufacturing Systems* 2005, 24 (1), 47-54.

- 76. Baines, T. S.; Asch, R.; Hadfield, L.; Mason, P. J.; Fletcher, S.; Kay, M. J. Towards a theoritical framework for human performance modelling with manufacturing systems design. *Simulation Modelling Practice and Theory* 2005, 13, 486-504.

- 77. Shahrokhi, M.; Bernard, A. A framework to develop an analysis agent for evaluating human performance in manufacturing systems. *CIRP Journal of Manufacturing Science and Technology* 2009, 2, 55-60.

- 78. Lamkull, D.; Hanson, L.; Ortengren, R. A comparative study of digital human modelling simulation results and their outcomes in reality: A case study within manual assembly of automobiles. *International Journal of Industrial Ergonomics* 2009, *39*, 428-441.

- 79. Law, A. M.; McComas, M. G. Secrets of Successful Simulation Studies. *Proceedings of the 1991 Winter Simulation Conference*, Phoenix, Arizona, 1991; 21-27.

- 80. Law, A. M. How to Conduct a Successful Simulation Study. *Proceedings of the 2003 Winter Simulation Conference*, New Orleans, Louisiana, 2003; 66-70.

- 81. Sargent, R. G. Verification and Validation of Simulation Models. *Proceedings* of the 2010 Winter Simulation Conference, Baltimore, Maryland, 2010; 166-183.

- 82. Yin, R. K. Case Study Research: Design and Methods, 3rd edition; Sage Publications: California, 2003.

- 83. Yin, R. K. *Applications of Case Study Research, 2nd edition;* Sage Publications: California, 2003.

- 84. McLean, C.; Shao, G. Generic Case Studies for Manufacturing Simulation Applications. *Proceedings of the 2003 Winter Simulation Conference*, New Orleans, Lousinia, 2003; 1217-1224.

- 85. Davis, J. P.; Eisenhardt, K. M.; Bingham, C. B. Developing Theory Through Simulation Methods. *Academy of Management Review* 2007, *32* (2), 480-499.

- 86. Runeson, P.; Host, M. Guidelines for conducting and reporting case study research in software engineering. *Empirical Software Engineering* 2009, *14*, 131-164.

- 87. Meredith, J. Building operations management theory through case and field research. *Journal of Operations Management* 1998, *16*, 441-454.

- 88. Package Types for Mobile Intel (R) Processors.

<a href="http://www.intel.com/support/processors/sb/cs-009864.htm">http://www.intel.com/support/processors/sb/cs-009864.htm</a> (accessed April 15, 2012).

- 89. Prasher, R.; Chiu, C.-P. Thermal Interface Materials. In *Materials for Advanced Packaging*; Lu, D., Wong, C.P., Eds.; Springer: US, 2009; pp 437-458.