# HIGH SPEED – ENERGY EFFICIENT SUCCESSIVE APPROXIMATION ANALOG TO DIGITAL CONVERTER USING TRI-LEVEL SWITCHING

# SAHAR SARAFI

A thesis submitted in fulfilment of the requirements for the award of the degree of Doctor of Philosophy (Electrical Engineering)

Faculty of Electrical Engineering Universiti Teknologi Malaysia

NOVEMBER 2015

To my beloved husband and family

#### **ACKNOWLEDGEMENT**

I am ever so grateful that after four years I am able to complete my PhD degree here at UTM. I have been blessed to be surrounded by family, friends, professors, officemates and colleagues who have provided cheers and support throughout my PhD.

My deep appreciation and gratitude goes to my supervisors Professor. Dr. Abu Khari Bin Aain for his kindness, constant endeavor, guidance and the numerous moments of attention he devoted throughout this work.

I would like to express my deepest gratitude to my parents who have given me unconditional support. I would like to thank my dearest husband for his patience, and his endless support in any possible way. This research would have never reached to this point without his support and patience. My success will always be his success too.

Last but not least, thanks to those who have helped me in the whole duration of my research development. For other researchers or students who wish to contact me, please do so via my email, Sahar.sarrafil@gmail.com.

#### **ABSTRACT**

This thesis reports issues and design methods used to achieve high-speed and high-resolution Successive Approximation Register analog to digital converters (SAR ADCs). A major drawback of this technique relates to the mismatch in the binary ratios of capacitors which causes nonlinearity. Another issue is the use of large capacitors due to nonlinear effect of parasitic capacitance. Nonlinear effect of capacitor mismatch is investigated in this thesis. Based on the analysis, a new Trilevel switching algorithm is proposed to reduce the matching requirement for capacitors in SAR ADCs. The integral non-linearity (INL) and the differential nonlinearity (DNL) of the proposed scheme are reduced by factor of two over conventional SAR ADC, which is the lowest compared to the previously reported schemes. In addition, the switching energy of the proposed scheme is reduced by 98.02% compared with the conventional SAR architecture. A new correction method to solve metastability error of comparator based on a novel design approach is proposed which reduces the required settling time about 1.1 t for each conversion cycle. Based on the above proposed methods two SAR ADCs: an 8-bit SAR ADC with 50MS/sec sampling rate, and a 10-bit SAR split ADC with 70 MS/sec sampling rate have been designed in 0.18µm Silterra complementary metal oxide semiconductor (CMOS) technology process which works at 1.2V supply voltage and input voltage of 2.4Vp-p. The 8-bit ADC digitizes 25MHz input signal with 48.16dB signal to noise and distortion ratio (SNDR) and 52.41dB spurious free dynamic range (SFDR) while consuming about 589µW. The figure of merit (FOM) of this ADC is 56.65 fJ/conv-step. The post layout of the 10-bit ADC with 1MHz input frequency produces SNDR, SFDR and effective number of bits (ENOB) of 57.1dB, 64.05dB and 9.17Bit, respectively, while its DNL and INL are -0.9/+2.8 least significant bit (LSB) and -2.5/+2.7 LSB, respectively. The total power consumption, including digital, analog and reference power, is 1.6mW. The FOM is 71.75fJ/conv. step.

#### **ABSTRAK**

Tesis ini melaporkan isu dan teknik reka bentuk yang diguna untuk menghasilkan penukar analog kepada digital Daftar Penghampiran Berturutan (SAR ADCs) yang berkelajuan dan resolusi tinggi. Satu kelemahan utama teknik ini berkaitan dengan ketakpadanan dalam nisbah perduaan kapasitor yang menyebabkan ketaklinaran. Satu lagi isu ialah penggunaan kapasitor besar disebabkan oleh kesan ketaklinaran kapasitor parasitik. Kesan ketidaklinaran kapasitor parasitik ini dikaji dalam tesis ini. Hasil daripada kajian ini, satu cara pensuisan Tri-tahap algoritma dicadangkan untuk mengurangkan keperluan sepadan kapasitor dalam SAR ADC. Ketidaklelurusan kamilan (INL) dan ketidaklelurusan perbezaan (DNL) pensuisan yang dicadangkan berjaya dikurangkan sebanyak dua kali ganda dan ini adalah yang paling rendah berbanding kaedah konvensional. Kuasa pensuisan juga dikurangkan sebanyak 98.02%. Satu cara pembetulan untuk menyelesaikan ralat metastabiliti juga dicadangkan dan berjaya mengurangkan masa menetap kepada 1.1τ bagi setiap kitar penukaran. Berdasarkan kepada teknik yang dicadangkan, dua SAR ADC telah direka bentuk: satu 8-bit SAR ADC dengan kadar pensampelan 50MS/saat dan satu 10-bit SAR ADC-Pecahan dengan kadar pensampelan 70MS/saat. Keduanya menggunakan proses CMOS 0.18µm daripada Silterra dengan bekalan kuasa 1.2V dan voltan masukan 2.4Vp-p. Bagi masukan 25MHz, ADC 8-bit mendigitalkan 48.16dB isyarat kepada hingar dan kadar herotan (SNDR) dan 52.41dB julat dinamik bebas palsu (SFDR) dengan menggunakan kuasa 589µW. Angka kebaikan (FOM) untuk ADC ini adalah 56.65 fJ/penukaran langkah. Pasca bentangan bagi ADC 10-bit dengan ulangan masukan 1MHz menghasilkan SNDR, SFDR and nombor bit berkesan (ENOB) of 57.1dB, 64.05dB dan 9.17Bit, setiap satu, manakala DNL and INL adalah -0.9/+2.8 bit paling kurang nilaian (LSB) dan -2.5/+2.7 LSB. Jumlah semua kuasa yang diguna termasuk litar digital, analog dan kuasa rujukan adalah 1.6mW. FOM pula adalah 71.75fJ/penukaran langkah.

# TABLE OF CONTENTS

| CHAPTER | TITLE                                      | PAGE |

|---------|--------------------------------------------|------|

|         | DECLARATION                                | ii   |

|         | DEDICATION                                 | iii  |

|         | ACKNOWLEDGEMENT                            | iv   |

|         | ABSTRACT                                   | v    |

|         | ABSTRAK                                    | vi   |

|         | TABLE OF CONTENTS                          | vii  |

|         | LIST OF TABLES                             | X    |

|         | LIST OF FIGURES                            | xi   |

|         | LIST OF ABBREVIATION                       | xvii |

|         | LIST OF SYMBOLS                            | xix  |

|         | LIST OF APPENDICES                         | xxi  |

| 1       | INTRODUCTION                               | 1    |

|         | 1.1 Introduction                           | 1    |

|         | 1.2 Problem statement                      | 2    |

|         | 1.3 Objectives                             | 7    |

|         | 1.4 Scope of work                          | 7    |

|         | 1.5 Contributions                          | 9    |

|         | 1.6 Thesis Organization                    | 10   |

| 2       | LITERATURE REVIEW                          | 12   |

|         | 2.1 Introduction                           | 12   |

|         | 2.2 ADC overview                           | 12   |

|         | 2.2.1 Analog-to-Digital Conversion Process | 12   |

|         | 2.3 ADC Architectures                      | 13   |

|           |                                                         | viii |

|-----------|---------------------------------------------------------|------|

| 2.4 Succ  | cessive Approximation Register ADC                      | 16   |

| 2.4.1     | Search Algorithm                                        | 17   |

| 2.4.2     | DAC architecture                                        | 18   |

| 2.4.3     | Switching algorithms                                    | 28   |

| 2.5 Meta  | astability Error of Comparator                          | 34   |

| 2.6 Sam   | pling switch                                            | 36   |

| 2.7 Sum   | nmary                                                   | 37   |

| RESEAI    | RCH METHODOLOGY                                         | 39   |

| 3.1 Intro | oduction                                                | 39   |

| 3.2 Inve  | estigation of nonlinear effect of capacitor mismatch on |      |

| SAR       | RADCs                                                   | 43   |

| 3.2.1     | Conventional method for linearity analysis              | 44   |

| 3.2.2     | Proposed Linearity-analysis method                      | 45   |

| 3.2.3     | Behavioral simulation results                           | 49   |

| 3.2.4     | Conclusion of investigation                             | 52   |

| 3.3 Prop  | posed switching algorithm                               | 53   |

| 3.3.1     | Linearity performance analysis of the proposed          |      |

|           | switching algorithm                                     | 55   |

| 3.3.2     | Switching energy of proposed switching algorithm        | 58   |

| 3.4 First | t designed ADC                                          | 60   |

| 3.5 Seco  | ond designed ADC                                        | 61   |

| 3.5.1     | Split DAC                                               | 61   |

| 3.5.2     | Analysis of parasitic capacitors effect on the Split    |      |

|           | SAR ADCs                                                | 63   |

| 3.5.3     | Proposed solution for nonlinear effect of parasitic     |      |

|           | capacitors on the Split SAR ADCs                        | 65   |

| 3.5.4     | Implementation of the proposed compensation             |      |

|           | method                                                  | 68   |

| 3.5.5     | Metastability Solution                                  | 74   |

| CIRCUI    | T DESIGN AND LAYOUT                                     | 78   |

| 4.1 Intro | oduction                                                | 78   |

| 4.2 Circ  | uit design                                              | 78   |

| • |   |

|---|---|

| 1 | X |

|              | 4.2.1 Sampling switch                                  | 78   |

|--------------|--------------------------------------------------------|------|

|              | 4.2.2 Comparator                                       | 86   |

|              | 4.2.3 Clock generator design                           | 102  |

|              | 4.3 Layout design                                      | 106  |

|              | 4.3.1 Layout plan                                      | 106  |

|              | 4.3.2 Capacitive DAC Array Layout                      | 109  |

| 5            | SIMULATION RESULTS                                     | 110  |

|              | 5.1 Introduction                                       | 110  |

|              | 5.2 Simulation results of sampling switch              | 110  |

|              | 5.3 Comparator simulation results                      | 120  |

|              | 5.4 Comparison proposed switching algorithm with other |      |

|              | algorithms                                             | 123  |

|              | 5.5 Simulation results of overall ADCs                 | 124  |

|              | 5.5.1 Circuit Model of a Package Lead                  | 125  |

|              | 5.5.2 Power Supply                                     | 126  |

|              | 5.5.3 Dynamic test of ADC                              | 127  |

|              | 5.5.4 INL and DNL Tests                                | 133  |

|              | 5.5.5 Energy efficiency test                           | 136  |

|              | 5.6 Comparison                                         | 139  |

| 6            | CONCLUSION AND FUTURE WORK                             | 143  |

|              | 6.1 Conclusion                                         | 143  |

|              | 6.2 Future work                                        | 145  |

| REFFEREN     | CES                                                    | 146  |

| Appendices A | A-C 155                                                | -161 |

|              |                                                        |      |

# LIST OF TABLES

| TABLE NO. | TITLE                                                                                                         | PAGE |

|-----------|---------------------------------------------------------------------------------------------------------------|------|

| 3.1       | Measured errors from different capacitors of MSB-array and LSB-array                                          | 71   |

| 5.1       | Comparison of THD of different switches (a) Vdd=1V, Fs=100MHz, Vin=2Vp-p (b) Vdd=0.8V, Fs=50MHz, Vin=0.7 Vp-p |      |

| 5.2       | Comparison of different switching Schemes in N-bit SAR ADC                                                    | 124  |

| 5.3       | Summary of performance of designed ADCs                                                                       | 138  |

| 5.4       | Comparison with state-of-the-art ADCs                                                                         | 141  |

| 5.5       | Comparison of 2nd SAR ADC with the state-of-the-art                                                           | 142  |

# LIST OF FIGURES

| FIGURE NO. | TITLE                                                              | PAGE |

|------------|--------------------------------------------------------------------|------|

| 1.1        | Conversion rate of SAR ADCs in different CMOS                      |      |

|            | technology process [7].                                            | 4    |

| 1.2        | gds-Vds curve at different Vgs for an NMOS transistor with         |      |

|            | size of w/l=10 $\mu$ /10 $\mu$ in Silterra 0.18um CMOS technology. | 6    |

| 1.3        | Conversion rate of SAR ADCs in different CMOS                      |      |

|            | technology process versus (Vdd -Vth) (from 1997 to 2014)           |      |

|            | [7].                                                               | 6    |

| 2.1        | Block diagram of ADC to show the conversion process [36].          | 14   |

| 2.2        | The resolution versus sampling frequency for the published         |      |

|            | ADCs in ISSCC and VLSI (from 1997 to 2014) [4].                    | 15   |

| 2.3        | The sampling rate versus technology process for the                | 1.0  |

|            | published ADCs (from 1997 to 2014) [4]                             | 16   |

| 2.4        | The block diagram of SAR ADC.                                      | 17   |

| 2.5        | Binary search algorithm [37].                                      | 18   |

| 2.6        | Charge redistribution 4-bit SAR DAC [43].                          | 19   |

| 2.7        | a) Conventional C-2C array [47]. b) Pseudo C-2C capacitor          |      |

|            | array [49].                                                        | 22   |

| 2.8        | a) simplified schematic of serial DAC [45]. b) Block               |      |

|            | diagram of proposed charge sharing SAR ADC in [47].                | 24   |

| 2.9        | Conventional split SAR ADC [76].                                   | 26   |

| 2.10       | MIM capacitor schematic with its parasitics [79].                  | 27   |

| 2.11       | a) Presented split capacitor array in [80]. b) Presented split     |      |

|            | capacitor array in [81]. c) Presented split capacitor array in     |      |

|            | [67].                                                              | 28   |

| 2.12       | A 3-bit set-and-down switching procedure.                          | 30   |

| 2.13 | A 3-bit common mode voltage based switching (merged            |    |

|------|----------------------------------------------------------------|----|

|      | capacitor switching) procedure.                                | 31 |

| 2.14 | A 3-bit Tri-Level switching procedure.                         | 32 |

| 2.15 | Waveform of conventional switching scheme, and waveform        |    |

|      | of tri-level switching scheme in [88].                         | 33 |

| 2.16 | Outputs of a typical clocked comparator [96].                  | 35 |

| 3.1  | Flowchart of research methodology.                             | 41 |

| 3.2  | ADC design procedure flowchart.                                | 43 |

| 3.3  | A simple capacitor array to investigate the linearity          |    |

|      | performance of DACs in SAR-ADCs.                               | 47 |

| 3.4  | Standard deviation of INL versus output code. a) by            |    |

|      | calculation. b) by Monte-Carlo simulation.                     | 51 |

| 3.5  | Standard deviation of DNL versus output code. a) by            |    |

|      | calculation. b) by Monte-Carlo simulation.                     | 52 |

| 3.6  | Proposed switching algorithm for a 4-Bit ADC.(Sampling         |    |

|      | phase and detection two MSBs)                                  | 55 |

| 3.7  | Proposed switching algorithm for a 4-Bit ADC. (After           |    |

|      | detection of first two bits).                                  | 56 |

| 3.8  | a) Standard deviation of INL versus output code. a) Standard   |    |

|      | deviation of DNL versus output code.                           | 58 |

| 3.9  | Schematic of the first designed SAR ADC.                       | 61 |

| 3.10 | The second Designed SAR ADC (Split DAC with proposed           |    |

|      | switching algorithm).                                          | 63 |

| 3.11 | Flowchart of implementing the proposed compensation            |    |

|      | method in ADC working phases.                                  | 70 |

| 3.12 | The status of capacitor arrays at the end of conversion        |    |

|      | process for output codes of a) 1000001001. b) 1000010010.      |    |

|      | c) 1000100010. d) 1001000100.                                  | 72 |

| 3.13 | SAR ADC operation phase. a) Sampling phase. b) MSB-            |    |

|      | phase of conversion. c) LSB-phase of conversion.               | 74 |

| 3.14 | Investigation of metastablity error in presence of DAC         |    |

|      | settling issue in four different states.                       | 77 |

| 3.15 | Metastability solution. a) Block diagram of output flip-flops. |    |

|      | b) Circuit of metastable state detector. c) Circuit of output            |     |

|------|--------------------------------------------------------------------------|-----|

|      | flip flop with metastable solution.                                      | 78  |

| 4.1  | Threshold voltage variation versus input voltage (Vbs). a) by            | 0.1 |

|      | MOSIS models [116]. b) by PTM models [117].                              | 81  |

| 4.2  | Block diagram of the proposed switch.                                    | 83  |

| 4.3  | Threshold voltage curve, variable factor of Vth and its                  |     |

|      | approximated curve as a linear function of input                         |     |

|      | voltage.(180nm Silterra CMOS technology)                                 | 85  |

| 4.4  | a) The proposed CMOS switch. b) Bootstrapping circuit for                |     |

|      | NMOS switch. c) Boosting circuit for PMOS switch.                        | 88  |

| 4.5  | Dynamic latched comparator.                                              | 89  |

| 4.6  | Transient of regeneration latch outputs.                                 | 91  |

| 4.7  | Latch delay versus Vcm for different power supply voltages               |     |

|      | $(\Delta Vin=1mV).$                                                      | 92  |

| 4.8  | Investigation of power supply (Vdd) and input common-                    |     |

|      | mode voltage (Vcm) on the latch noise.                                   | 95  |

| 4.9  | Input referred noise as a function of $\rho$ . ( $\Phi$ =1.4, Vdd =1.2V, |     |

|      | Vcm=0.75V)                                                               | 96  |

| 4.10 | Input referred noise as a function of $\Phi$ . ( $\rho$ =2, Vdd =1.2V,   |     |

|      | Vcm=0.75V)                                                               | 97  |

| 4.11 | Input referred offset voltage of dynamic latch versus Vcm in             |     |

|      | different supply voltages.                                               | 101 |

| 4.12 | Pre-amplifier design.                                                    | 102 |

| 4.13 | Conventional clocking system. a) Ring oscillator. b) Clock               |     |

|      | signals to pick comparator output.                                       | 104 |

| 4.14 | Timing of each conversion cycle.                                         | 105 |

| 4.15 | a) Flip flop circuit used as a cell in ring oscillator. b) circuit       |     |

|      | to produce Qi signals.                                                   | 106 |

| 4.16 | Circuit to produce sampling clock.                                       | 106 |

| 4.17 | Layout plan.                                                             | 109 |

| 4.18 | Prepared layout for the 2nd ADC.                                         | 109 |

| 4.19 | DAC array layout plan.                                                   | 110 |

| 5.1  | a) Bootstrapped clock signals by conventional and proposed               |     |

|      | circuits. (at Vdd =1V and Fs=100 MS/sec) b) enlarged         |     |

|------|--------------------------------------------------------------|-----|

|      | bootstrapped clock for input voltage close to the "gnd". c)  |     |

|      | enlarged bootstrapped clock for input voltage close to the   |     |

|      | "vdd" .                                                      | 112 |

| 5.2  | Comparison of Total Harmonic Distortion (THD) of the         |     |

|      | proposed bootstrapped switch with the conventional switch    |     |

|      | for various sampling frequencies at different power supply   | 110 |

|      | voltages.                                                    | 113 |

| 5.3  | On-state resistance (Ron) of switch versus input voltage     | 115 |

| 5.4  | The effect of devices size ratio on sampling performance for |     |

|      | various temperatures. a) HD2 versus (Wp/Wn). b) HD3          |     |

|      | versus (Wp/Wn). c) THD versus (Wp/Wn) for single-ended       |     |

|      | mode. d) THD versus (Wp/Wn) for differential modes. (        |     |

|      | NMOS switch size is 5 um/0.18 um and fs=100 MHz, fin=1       |     |

|      | MHz at Vdd=1 V)                                              | 117 |

| 5.5  | The proposed CMOS switch performance in time domain.         | 110 |

|      | (Vdd =1.2 V, Vin =1.2 Vpp).                                  | 118 |

| 5.6  | The performance of the proposed structure in time domain.    |     |

|      | a) Vdd =0.8 V, Vin=0.8 Vp-p, fin=9.3 MHz, fs=50 MHz b)       |     |

|      | Vdd=1V, Vin=1V p-p, fin=9.3 MHz, fs=100 MHz.                 | 119 |

| 5.7  | The FFT spectrums. a) Vdd =1.2V and Fs=70MHZ (for            |     |

|      | designed ADC). b) Vdd =1V and Fs=100 MHZ. c) Vdd             |     |

|      | =0.8V and Fs=50 MHZ.                                         | 120 |

| 5.8  | THD versus sampling frequency                                | 121 |

| 5.9  | Worse case test of comparator.                               | 122 |

| 5.10 | Test set up to determine the input referred offset voltage.  | 123 |

| 5.11 | Comparator offset voltage obtained from 100 samples of       |     |

|      | transient Monte-Carlo simulations. (Vcm=0.8V)                | 124 |

| 5.12 | Comparison of switching energy at each output code for       |     |

|      | different algorithms.                                        | 125 |

| 5.13 | The equivalent circuit of bonding-wire and Package-Leads.    | 127 |

| 5.14 | The circuit to produce supply voltage with noise and         |     |

|      | package effects.                                             | 128 |

| 5.15 | Power supply voltage waveform in ideal state, with noise     |     |

|------|--------------------------------------------------------------|-----|

|      | (out of chip) and after passing through package and pad      |     |

|      | equivalent circuit (inside chip).                            | 128 |

| 5.16 | Test bench to investigate the dynamic performance of         |     |

|      | designed ADCs.                                               | 129 |

| 5.17 | FFT plot of the proposed ADC with sampling rate at 50 MS     |     |

|      | for two different input frequencies.                         | 130 |

| 5.18 | Dynamic performance versus input frequency at 50MS.          | 130 |

| 5.19 | FFt spectrum of the 2nd designed SAR ADC at 70MS/sec         |     |

|      | with Fin=1 MHz. a) Before compensation. b) After             |     |

|      | compensation. (post-layout)                                  | 132 |

| 5.20 | SNDR plot versus input frequency (Vdd =1.2, Fs =             |     |

|      | 70MS/sec, $Vin = 2.4Vpp$ ).                                  | 133 |

| 5.21 | SFDR plot versus input frequency (Vdd =1.2, Fs =             |     |

|      | 70MS/sec, $Vin = 2.4Vpp$ ).                                  | 133 |

| 5.22 | ENOB plot versus input frequency (Vdd =1.2, Fs =             |     |

|      | 70MS/sec, $Vin = 2.4Vpp$ ).                                  | 134 |

| 5.23 | Test bench to investigate the static performance of designed |     |

|      | ADCs.                                                        | 135 |

| 5.24 | DNL and INL versus output code.                              | 135 |

| 5.25 | DNL of 10Bit split SAR ADC versus output codes. a) Before    |     |

|      | compensation. b) After compensation.                         | 136 |

| 5.26 | INL of 10Bit split SAR ADC versus output codes. a) Before    |     |

|      | compensation. b) After compensation.                         | 137 |

| 5.27 | Dynamic performance of designed split SAR ADC at             |     |

|      | different sampling rates (Vdd =1.2, Vin = 2.4Vp-p and Fin=   |     |

|      | Nyquist frequency).                                          | 138 |

| 5.28 | Figure of merit FOM, of designed split SAR ADC at            |     |

|      | different sampling rates (Vdd =1.2, Vin = 2.4Vp-p and Fin=   |     |

|      | Nyquist frequency).                                          | 139 |

| 5.29 | Comparison of conversion rate of SAR ADCs in different       |     |

|      | CMOS technology process with this work.                      | 140 |

5.30 The FOM versus conversion rate of SAR ADCs in different 142 CMOS technology process with this work.

## LIST OF ABBREVIATION

A/D - Analog-to-Digital

ADC - Analog-to-Digital Converter

BW - bandwidth product

CM - Common Mode

CMOS - Complementary Metal Oxide Semiconductor

D/A - Digital-to-Analog

DAC - Digital-to-Analog Converter

dB - Decibel

DC - Direct Current

DNL - Differential Non-Linearity

DR - Dynamic Range

ENOB - Effective Number Of Bits

FOM - Figure-of-merit

IC - Integrated Circuit

INL - Integral Non-Linearity

IOT - Internet of Things

LSB - Least Significant Bit

MOSFET - Metal Oxide Semiconductor Field Efect Transistor

MSB - Most Significant Bit

NMOS - n-channel Metal Oxide Semiconductor

OTA - Operational Transconductance Amplifier

PMOS - p-channel Metal Oxide Semiconductor

S/H - Sample-and-Hold

SAR - Successive Approximation Register

SC - Switched Capacitor

SFDR - Spurious Free Dynamic Range

SNDR - Signal-to-Noise-and-Distortion Ratio

SNR - Signal-to-Noise Ratio

SoC - System on a Chip

SOI - Silicon On Insulator

T/H - Track-and-Hold

THD - Total Harmonic Distortion

VCO - Voltage Controlled Oscillator

Vpp - Volts peak-to-peak

## LIST OF SYMBOLS

C - Capacitor

$C_G$  - Gate capacitance

C<sub>L</sub> - Load capacitance

$C_{ox}$  - Gate oxide capacitance

dB - Decibel

f - Frequency

f<sub>S</sub> - Sampling frequency

$g_{m}$  - Transconductance

$g_{ds}$  - Channel conductance

h(t) - Sampling function

I<sub>D</sub> - Drain current

kHz - Kilohertz

K - Boltzmann's constant

L - Channel length

$L_{min}$  - Minimum channel length

MHz - Megahertz

N - Number of bits

nF - Nanofarad

pF - Picofarad

R - Resistor

R<sub>ON</sub> - Switch on-resistance

T - Absolute temperature, sampling period

t - Time

$t_{ox}$  - Oxide thickness

τ - Time constant

V- Inverting Input

V+ - Non-inverting Input

$V_{dd}$  - Positive supply voltage

$V_{dsat}$  - Drain-source saturation voltage

$V_{FS}$  - Full-scale voltage

$V_{GS}$  - Gate-source voltage

$V_{pp}$  - Voltage Peak-to-Peak

$V_{ref}$  - Voltage Reference

$V_{Supply} \qquad \text{-} \qquad Voltage \ Supply \\$

$V_{\text{th}}$  - Threshold voltage

W - Channel width

$\mu F$  - Microfarad

$\mu$  - Carrier mobility

$\sigma^2$  - Variance

# LIST OF APPENDICES

| APPENDIX | TITLE                                                      | PAGE |

|----------|------------------------------------------------------------|------|

| A        | MATLAB code for switching energy of the proposed switching |      |

|          | algorithm                                                  | 157  |

| В        | MATLAB code for behavioural simulation of linearity        |      |

|          | performance of the proposed switching algorithm            | 160  |

| C        | List of publications                                       | 163  |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Introduction

Due to the advancement in fabrication technology in recent decades, transistors have become faster making possible to achieve high-rate energy-efficient digital circuits. For analog circuits the evolution of technology is not as beneficial. Besides of high speed performance and energy efficiency, there are several advantages of processing in digital domain such as storage capability, unlimited signal to noise ratio, programmability and performing complex algorithms. Thus, there is an increasing trend to perform more and more signal processing functions in digital.

Since the nature of signals needed to be processed in real world is analog, there is an increasing demand for analog to digital converters (ADCs). ADCs act as the entrance gates in digital signal processing systems. They have crucial roles in modern signal processing and communication systems because their speed and accuracy can effect on overall system performance.

Recently, the applications of ADCs have been expanded widely as many electronic systems that used to be entirely analog have been implemented using digital electronics [1]. This research is focused on high speed ADCs with sampling frequencies greater than 5 MS/sec and resolutions 10-14 bits used in many types of instrumentation (including digital oscilloscopes, spectrum analyzers, and medical imaging), video, radar, communications applications (including IF sampling,

software radio, base stations, and set-top boxes) and consumer electronics equipment (such as digital cameras, display electronics, DVDs, enhanced definition TVs).

On the other hand, during the last decade much effort has been put into the reduction of the supply voltage and the supply power of mixed signal CMOS systems. Three main reasons can be given for the necessity of low-voltage circuits. The first one comes from the continued down-scaling of device feature size. As the channel length is scaled down into submicron and the gate-oxide thickness becomes only several nanometres thick, the supply voltage has to be reduced due to reliability issues. The second reason is referred to the increasing components on chip. A silicon chip can only dissipate a limited amount of power per unit area. The last reason is dictated by portable, battery-powered equipment. One of the most effective ways to reduce active power consumption is by lowering the supply voltage [2].

However lowering supply voltage creates a number of challenges in high speed, high resolution circuit design. Unlike digital circuits and systems that have enjoyed benefits of scaling, there are some serious issues which analog circuits deal with them such as ever-shrinking signal range, lower device gain, poor matching, and increased substrate noise [3]. Since there is only comparator circuit as analog component in SAR-ADCs and there isn't any gain stage to amplify residue in SAR ADCs, this architecture is more popular among various ADC architectures for low voltage applications.

This work concentrates on low voltage SAR ADC by searching for and developing techniques and circuit structures suitable for low voltage designs. In parallel, this work also aims to achieve high-accuracy high-speed low-power design.

#### 1.2 Problem statement

SAR ADCs are conventionally used for medium-speed medium-resolution applications as categorized as the first group of applications mentioned above. Recently, many intelligent design techniques and advances in CMOS technologies

have enhanced the conversion rate and resolution achieved by SAR architecture. However there are some issues to design high speed low-voltage SAR ADC with high resolution as explained below.

## 1.2.1.1 Architectural issues of SAR ADC to achieve high sampling rate

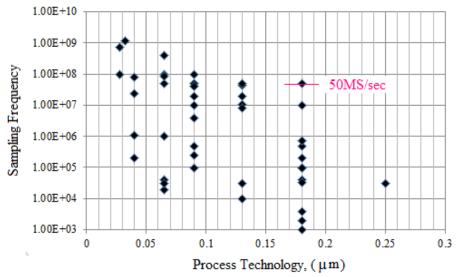

As mentioned above the most component of SAR ADC are digital circuits and digital circuits benefit from scaling technology process. Therefore it is expected that SAR ADCs, also benefit from small technology process. Figure 1.1 shows the sampling rate of SAR ADCs versus their technologies consisting of all SAR ADCs published from 1999 to 2014 from [4] and other outstanding designs from different journals such as [5-7]. As explained it is clear that SAR ADC is a compatible architecture with technology advancement.

**Figure 1.1** Conversion rate of SAR ADCs in different CMOS technology process [7].

Although SAR ADC benefits from technology scaling, the main limitation of this ADC to achieve high conversion rate is not related to the technology. The main obstacle to speed up the SAR ADCs is due to large capacitor- arrays consisting of a number of unit capacitors. To achieve high resolution, large size and large number of unit capacitors are needed which takes longer time to settle the comparison voltage levels in every conversion cycles [8].

Decreasing the total capacitance of the capacitor arrays is an effective solution to obtain high speed SAR ADC which can be implemented with two methods. The first method is reduction of the unit capacitor size. Since the

comparison voltage in each conversion cycle is obtained by charge redistribution in capacitor array, the ratios between capacitors determine the comparison voltage level. Therefore any mismatch between capacitor leads to errors in conversion steps and deviation from ideal I/O transfer function which is known as non-linearity effects. Therefore some extra circuits should be added for calibration or error correction. The second method to decrease the total capacitance array is by decreasing the number of unit capacitors which requires a new search algorithm or new switching methods.

# 1.2.1.2 Effect of lowering supply voltage on SAR ADC sampling rate

As mentioned above most SAR ADC components are digital circuits. Although down scaling supply voltage leads to decrease energy per operation in digital circuits, it causes increase in delay [9-12]. In fact power consumption is reduced at the cost of lower performance. Since changes in supply voltage affects all gates in the same way, delay of any gate remains roughly proportional to the delay of an inverter which is investigated with detail in [13]. As conclusion, as power supply voltage approximates to the threshold voltage, delay of digital cells is increased and maximum operation speed is limited.

Further SAR ADC operation is based on consecutive switching of capacitive DAC, there is another effective factor of switch conductance to determine the required DAC settling time. In real implementation, NMOS and PMOS devices are used as switches which operate on linear region like a resistor. There is a direct relation between current from drain to source,  $I_{ds}$ , of MOSFETs in ON-state and applied voltage to the gate-source connection,  $V_{gs}$ .

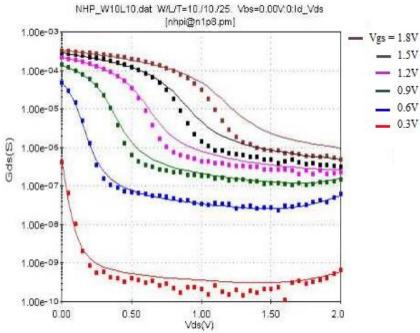

Since the maximum applied  $V_{gs}$  is limited to the supply voltage, supply voltage reduction results to decrease the conductance of MOSFETs. As  $V_{gs}$  is decreased, the conductance of switch is reduced which means more time is required for DAC settling. Figure 1.2 shows the conductance of switch,  $g_{ds}$ , versus  $V_{ds}$  for different  $V_{gs}$  values for an NMOS transistor of Silterra's 0.18um CMOS technology. As explained above, as supply voltage reduces and  $(V_{dd}$  - $V_{th})$  decreases, digital circuit delay

increases. Hence the SAR logic unit consisting of digital circuits needs more time which means less conversion speed.

**Figure 1.2**  $g_{ds}$ - $V_{ds}$  curve at different  $V_{gs}$  for an NMOS transistor with size of w/l=10  $\mu$ /10 $\mu$  in Silterra 0.18um CMOS technology.

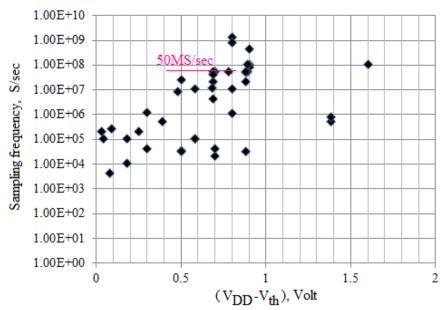

Based on the above explanation, as supply voltage approximates to the threshold voltage it is expected to limit the conversion rate of SAR. Figure 1.3 shows sampling rate of SAR ADCs versus ( $V_{dd}$ - $V_{th}$ ) of all SAR ADCs published from 1999 to 2014 from [4] and other outstanding designs from different journals. This graph confirms that sampling rate of SAR ADCs decreases as ( $V_{dd}$ - $V_{th}$ ) reduces.

**Figure 1.3** Conversion rate of SAR ADCs in different CMOS technology process versus  $(V_{dd} - V_{th})$  (from 1997 to 2014) [7].

#### 1.2.1.3 Sampling switch issues

The low supply voltage inherently limits the maximum input signal swing of an ADC, and thus may lead to a poor peak signal-to-noise ratio (SNR). To achieve higher accuracy and higher signal to noise and distortion ratio (SNDR), it is better to have larger input range which is limited to the power rails. However rail-to-rail input leads to the difficulty of circuit design (especially analog parts) in rail-to-rail condition.

The sampling switches as the input gate of SAR ADC has an important role in determining the overall performance. MOSFET transistor is a natural switch which is extensively used in S/H. However there are several issues (such as charge injection [14], clock feed through, MOS transconductance variation [15-17], body effect [18-23]) which are exacerbated for low voltage rail-to-rail condition. By considering the limitation of maximum tolerable voltage for gate-source connection of MOSFETs, tracking rail-to-rail input voltage is not possible with a simple MOSFET switch. Furthermore, in comparison to input signal range, threshold voltage variation is not negligible and causes nonlinearity effect on "ON" state switch resistance [14, 24, 25]. To achieve high-speed high-resolution ADCs, high-resolution high speed switches are needed.

Although there are some techniques to boost the  $V_{gs}$  and make it signal independent, final achieved  $V_{gs}$  value is a function of  $V_{dd}$ , too. Thus lowering supply voltage means restricting the band width of switches performances, too. The techniques mentioned above are discussed and analyzed more deeply in the following chapters.

The above mentioned issues to enhance the conversion rate of SAR ADCs and additional difficulties resulting from lowering supply voltage call for research work to design proper circuits, concentrated on rail-to-rail low voltage designs, and finding new methods for enhancing SAR-ADC characteristics at this condition.

# 1.2.1.4 Metastability error of comparator

One of the comparator error which is known as metastability error is a degrading factor in SAR ADC performance. Metastability is a problem that occurs in

all latching comparators as the output does not saturate to valid regions of logical one or zero during comparison time. Since the conversion process of SAR ADC is a serial operation, any error in output of comparator in each cycle penetrates to the remind process without any chance to get back and doing correction. Although there are some techniques to solve this issue, but most of them are not suitable solutions for low voltage applications due to the required analog components. Further investigation of metastable error besides of incomplete DAC settling shows more research work is required to develop current solutions or find new approach.

# 1.3 Objectives

This PhD thesis focuses on design of a rail-to-rail low voltage SAR ADC in 0.18µm process CMOS technology. By taking into account the aforementioned problem statements, the following objectives are the main concern of this research.

- 1. To investigate non-linear effect of capacitor mismatch and effective methods to control it.

- 2. To implement the design using a small power supply voltage of 1.2V.

- 3. To enhance SAR-ADC conversion speed higher than 50MS/sec.

#### 1.4 Scope of work

The scope of this research is as explained below:

• Investigation capacitor mismatch:

Capacitor mismatch is an inevitable issue of capacitive DAC arrays and all SAR ADCs suffer from this issue beyond their used technologies and applied supply voltages. Thus investigation of capacitor mismatch and finding a model consisting of all effective factors to control the resulted nonlinearities in converter performance is within the scope of this research.

# • Proposing a new switching algorithm

Since the mismatch requirement and switching algorithm determine the size and number of unit capacitors in SAR ADC, a switching algorithm is developed to decrease the number of unit capacitors without damaging the linearity of performance.

# • The choice of process technology and supply voltage

When we look at the new application areas where we see the future wave of sub stream innovation happening such as medical and wearable's, IoT, ... we see that it is not necessarily needed to use the most advanced technologies such as 28nm [26]. The chosen technology for this work is 0.18um CMOS technology process which is the most popular and commercial technologies in the last decade [26-28]. Now the main challenge in this mature technology is enhancement of energy efficiency which is studied through circuit architecture development and decreasing the supply voltage [6, 7, 29-32]. According to the shown supply voltage margin reduction in [33], 1.2 volt is considered as the supply voltage.

# • Development of conversion rate

CMOS technology and supply voltage in this work are 0.18µm and 1.2V, respectively. As shown in Figure 1.1, the maximum achieved conversion rate in 0.18µm technology is 50MS/sec in [6, 7]. Further (V<sub>dd</sub> -V<sub>th</sub>) is a value between 0.6V and 0.7V which the maximum achieved conversion rate is 50MS/sec as shown in Figure 1.3. The highest speed converters in this range are 9-bit with 40MS/sec and two 10-bit ADCs with 50MS/sec in 90nm, 65nm and 0.18µm technologies, respectively [6, 34, 35]. The goal of this work is to achieve conversion rate higher than 50 MS/sec.

# • Development in sampling switch design

The sampling switches as the fundamental block are investigated at low supply voltage. Some solutions are proposed to enhance their performance.

#### Development in metastability solution

A new development in correction method for metastability error is proposed which is useful for incomplete settling of DAC output voltage, also.

#### 1.5 Contributions

In this thesis, two SAR ADCs are presented with 5 contributions which are listed below. The main contributions leads to improve the conversion rate and linearity performance of SAR ADCs at low supply voltage, energy efficient condition.

- Nonlinear effect of capacitor mismatch on SAR ADC performance is investigated which leads to the development of a new model of capacitor mismatch on capacitive-DACs. Based on the new model, effective factors to control the non-linear effect of capacitor mismatch are determined.

- 2. From the achieved results from the above mentioned investigation, a new Trilevel switching algorithm is proposed to reduce the matching requirement for capacitors in SAR ADCs. The integral non-linearity (INL) and the differential non-linearity (DNL) of the proposed scheme are reduced by factor of two over the conventional SAR ADC which is the lowest compared to the previous schemes. In addition, the switching energy of the proposed scheme is reduced by 98.02% as compared with the conventional architecture which is the most energy-efficient algorithms in comparison with the previous algorithms, too.

- 3. Nonlinear effect of parasitic capacitors on split SAR ADC performance is investigated and a new error correction method is proposed to improve its performance. In the proposed method, the maximum possible error is measure before the ADC starts the conversion process. Since this error is negative, it is injected to the DAC array by pre-charging the LSB array during MSB conversion phase. After complete the conversion process, an error correction is applied through MATLAB software. Differential nonlinearity (DNL) of ADC before compensation is within -1LSB and +4.3LSB which is restricted to

-0.9LSB and +2.8LSB after applying compensation. Also, integral nonlinearity (INL) of ADC before compensation is within -4.4LSB and +5.3LSB which is restricted to -2.5LSB and +2.7LSB after applying compensation.

- 4. One of the comparator error which is known as metastability error is a degrading factor in SAR ADC performance. A new development in correction method for metastability error is proposed which is useful for incomplete settling of DAC output voltage, also.

- 5. A new optimized CMOS switch is proposed consisting of a bootstrapped NMOS switch and a boosted PMOS switch as a transmission gate. By utilizing this technique, the nonlinearity resulting from the threshold voltage variation (body effect) of NMOS switch is mitigated, considerably, compared to standard CMOS switch or a bootstrapped NMOS switch.

# 1.6 Thesis Organization

The rest of the thesis is organized as follows.

Chapter 2 reviews the successive approximation structure and its positive and negative characteristics. This chapter is followed by introducing the previous solutions and designs in terms of search algorithms and switching schemes in the published high-performance SAR ADCs. After review of conversion process and algorithms, the metastable state of comparator and conventional solution is introduced. At the last part of this chapter a review on sampling switches, which is subjected to develop in this thesis, is presented.

Chapter 3 presents research methodology of this research. At first, analysis of nonlinear effect resulted from capacitor mismatch is discussed. Then the proposed switching algorithm is presented with its performance details in aspect of linearity and energy consumption. Next the first ADC design which is based on the presented algorithm is explained. For the second ADC design split architecture is combined

with the new algorithm. This section is followed by investigation of nonlinear error from parasitic capacitors. The presented investigation is a way to reach the proposed correction method.

Chapter 4 presents the circuit design details and layout preparation. This chapter starts with the proposed sampling CMOS switch which acts as entrance gate of ADC. The circuits of comparator, clock generation and output buffers are presented at the following of this chapter. At the second part of this chapter layout of the second ADC is exposed and discussed.

Chapter 5 exposes the achieved results from simulation of each circuit. The simulation condition applied to the designed ADCs is discussed which is followed by simulation results of both designed ADCs. Finally, the performances of designed ADCs are compared with previous published works.

Chapter 6 concludes the research findings. Recommendations for future works are also addressed to assist other researchers in pursuing the works for further development and improvement.

#### REFFERENCES

- 1. Zjajo, A., *Design and debugging of multi-step analog to digital converters*. Netherlands, Universiteitsdrukerij Technische Universiteit Eindhoven, 2010.

- 2. Meijer, M. and J.P. de Gyvez, *Technological boundaries of voltage and frequency scaling for power performance tuning*, in *Adaptive Techniques for Dynamic Processor Optimization*. 2008, Springer. p. 25-47.

- 3. Byeong-Ha, P. Mixed-signal ICs in nano-scale technologies: Design and challenges. in Electron Devices and Solid-State Circuits, 2009. EDSSC 2009. IEEE International Conference of. 2009.

- 4. Murmann, B. *ADC Performance Survey 1997-2014*. Available from: <a href="http://web.stanford.edu/~murmann/adcsurvey.html">http://web.stanford.edu/~murmann/adcsurvey.html</a>.

- 5. Rahimi, E. and M. Yavari, *Energy-efficient high-accuracy switching method for SAR ADCs*. Electronics Letters, 2014. **50**(7): p. 499-501.

- 6. Arian, A., et al., A 10-bit 50-MS/s redundant SAR ADC with split capacitive-array DAC. Analog Integrated Circuits and Signal Processing, 2012. **71**(3): p. 583-589.

- 7. Ning, Q., et al., A 10-bit 50-MS/s reference-free low power SAR ADC in 0.18-μm SOI CMOS technology. Journal of Semiconductors, 2012. **33**(9): p. 095005.

- 8. YoungJoo, L., S. Jinook, and P. In-Cheol. Statistical modeling of capacitor mismatch effects for successive approximation register ADCs. in SoC Design Conference (ISOCC), 2011 International. 2011.

- 9. Nielsen, L.S., et al., Low-power operation using self-timed circuits and adaptive scaling of the supply voltage. Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, 1994. **2**(4): p. 391-397.

- 10. Wang, A., A.P. Chandrakasan, and S.V. Kosonocky. *Optimal supply and threshold scaling for subthreshold CMOS circuits*. in *VLSI*, 2002. *Proceedings. IEEE Computer Society Annual Symposium on*. 2002.

- 11. Calhoun, B.H. and A.P. Chandrakasan, *Ultra-dynamic Voltage scaling* (*UDVS*) using sub-threshold operation and local Voltage dithering. Solid-State Circuits, IEEE Journal of, 2006. **41**(1): p. 238-245.

- 12. Liang, D., et al. *Power switch characterization for fine-grained dynamic voltage scaling*. in *Computer Design*, 2008. *ICCD* 2008. *IEEE International Conference on*. 2008.

- 13. Gonzalez, R., B.M. Gordon, and M.A. Horowitz, *Supply and threshold voltage scaling for low power CMOS*. Solid-State Circuits, IEEE Journal of, 1997. **32**(8): p. 1210-1216.

- 14. Centurelli, F., et al., *Design Solutions for Sample-and-Hold Circuits in CMOS Nanometer Technologies*. Circuits and Systems II: Express Briefs, IEEE Transactions on, 2009. **56**(6): p. 459-463.

- 15. Abo, A.M. and P.R. Gray. A 1.5 V, 10-bit, 14 MS/s CMOS pipeline analog-to-digital converter. in VLSI Circuits, 1998. Digest of Technical Papers. 1998 Symposium on. 1998.

- 16. Asgari, M.R., S.H. Pishgar, and O. Hashemipour. A reliable full-swing low-distortion CMOS bootstrapped sampling switch. in 18th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2011. 2011.

- 17. Yunfeng, P., et al. A Novel Technique for Improving the Linearity of MOS Sampling Switch. in Communications, Circuits and Systems Proceedings, 2006 International Conference on. 2006.

- 18. Steensgaard, J. Bootstrapped low-voltage analog switches. in Circuits and Systems, 1999. ISCAS '99. Proceedings of the 1999 IEEE International Symposium on. 1999.

- 19. Fayomi, C.J.B., G.W. Roberts, and M. Sawan. Low-voltage CMOS analog switch for high precision sample-and-hold circuit. in Circuits and Systems, 2000. Proceedings of the 43rd IEEE Midwest Symposium on. 2000.

- 20. Waltari, M. and K. Halonen, *Bootstrapped switch without bulk effect in standard CMOS technology*. Electronics Letters, 2002. **38**(12): p. 555-557.

- 21. Sonkusale, S.R. and J. Van der Spiegel. A low distortion MOS sampling circuit. in Circuits and Systems, 2002. ISCAS 2002. IEEE International Symposium on. 2002.

- 22. Chun-Yueh, Y. and H. Chung-Chih, A low-voltage low-distortion MOS sampling switch, in Circuits and Systems, 2005. ISCAS 2005. IEEE International Symposium on. 2005. p. 3131-3134 Vol. 4.

- 23. Asgari, M. and O. Hashemipour, *Body effect compensation of analog switches using variable voltage function*. IEICE Electronics Express, 2011. **8**: p. 189-194.

- 24. Galhardo, A., J. Goes, and N. Paulino. Design of Improved Rail-to-Rail Low-Distortion and Low-Stress Switches in Advanced CMOS Technologies. in Electronics, Circuits and Systems, 2007. ICECS 2007. 14th IEEE International Conference on. 2007.

- 25. Keskin, M., A low-voltage CMOS switch with a novel clock boosting scheme. Circuits and Systems II: Express Briefs, IEEE Transactions on, 2005. **52**(4): p. 185-188.

- 26. Europractice, I., service: 'Activity report 2014'. 2015.

- 27. Europractice, I., service: 'Activity report 2013'. 2014.

- 28. anysilicon, Semiconductor Technology Nodes History, Trends and Forecast 2013.

- 29. Ng, M.Y. 0.18 um low voltage 12-bit successive-approximation-register analog-to-digital converter (SAR ADC). in Quality Electronic Design (ASQED), 2011 3rd Asia Symposium on. 2011: IEEE.

- 30. Huang, H.-Y., et al. A 9.2 b 47fJ/conversion-step asynchronous SAR ADC with input range prediction DAC switching. in Circuits and Systems (ISCAS), 2012 IEEE International Symposium on. 2012: IEEE.

- 31. Venkatram, H., et al. A 48 fJ/CS, 74 dB SNDR, 87 dB SFDR, 85 dB THD, 30 MS/s pipelined ADC using hybrid dynamic amplifier. in VLSI Circuits Digest of Technical Papers, 2014 Symposium on. 2014: IEEE.

- 32. Khojasteh Lazarjan, V. and K. Hajsadeghi. 12 bits, 40MS/s, low power pipelined SAR ADC. in Circuits and Systems (MWSCAS), 2014 IEEE 57th International Midwest Symposium on. 2014: IEEE.

- 33. Baschirotto, A., et al., Low power analog design in scaled technologies. 2009.

- 34. Giannini, V., et al. An 820uW 9b 40MS/s Noise-Tolerant Dynamic-SAR ADC in 90nm Digital CMOS. in Solid-State Circuits Conference, 2008. ISSCC 2008. Digest of Technical Papers. IEEE International. 2008.

- 35. Yoshioka, M., et al., A 10-b 50-MS/s 820-uW SAR ADC With On-Chip Digital Calibration. Biomedical Circuits and Systems, IEEE Transactions on, 2010. **4**(6): p. 410-416.

- 36. Delić-Ibukić, A., Digital background calibration techniques for highresolution, wide bandwidth analog-to-digital converters, in Electrical Engineering. 2008, University of Maine.

- 37. Sang-Hyun, C., et al., A 550-μW 10-b 40-MS/s SAR ADC With Multistep Addition-Only Digital Error Correction. Solid-State Circuits, IEEE Journal of, 2011. **46**(8): p. 1881-1892.

- 38. Cecil, J. A CMOS 10-bit D/A converter. in Solid-State Circuits Conference. Digest of Technical Papers. 1974 IEEE International. 1974.

- 39. Hamad'e, A. and E. Campbell. A single-chip 8-bit A/D converter. in Solid-State Circuits Conference. Digest of Technical Papers. 1976 IEEE International. 1976.

- 40. Hamade, A.R., *A single chip all-MOS 8-bit A/D converter*. Solid-State Circuits, IEEE Journal of, 1978. **13**(6): p. 785-791.

- 41. Comer, D., *A monolithic 12-bit DAC*. Circuits and Systems, IEEE Transactions on, 1978. **25**(7): p. 504-509.

- 42. Suarez, R.E., P.R. Gray, and D.A. Hodges, *All-MOS charge-redistribution analog-to-digital conversion techniques*. *II*. Solid-State Circuits, IEEE Journal of, 1975. **10**(6): p. 379-385.

- 43. McCreary, J.L. and P.R. Gray, *All-MOS charge redistribution analog-to-digital conversion techniques*. *I.* Solid-State Circuits, IEEE Journal of, 1975. **10**(6): p. 371-379.

- 44. J. Craninckx and G. Van der Plas, A 65fJ/Conversion-Step 0-to-50MS/s 0-to-0.7mW 9b Charge-Sharing SAR ADC in 90nm Digital CMOS . in Solid-State Circuits Conference ISSCC. 2007. p. 246 600

- 45. Ginsburg, B.P. and A.P. Chandrakasan. An energy-efficient charge recycling approach for a SAR converter with capacitive DAC. in Circuits and Systems, 2005. ISCAS 2005. IEEE International Symposium on. 2005.

- 46. You-Kuang, C., W. Chao-Shiun, and W. Chorng-Kuang. A 8-bit 500-KS/s low power SAR ADC for bio-medical applications. in Solid-State Circuits Conference, 2007. ASSCC '07. IEEE Asian. 2007.

- 47. Yang, J., T.L. Naing, and R.W. Brodersen, A 1 GS/s 6 bit 6.7 mW successive approximation ADC using asynchronous processing. Solid-State Circuits, IEEE Journal of, 2010. **45**(8): p. 1469-1478.

- 48. Bako, N. and A. Baric. A low-power fully differential 9-bit C-2C cyclic ADC. in Circuit Theory and Design (ECCTD), 2011 20th European Conference on. 2011: IEEE.

- 49. Furuta, M., M. Nozawa, and T. Itakura, *A 10-bit, 40-MS/s, 1.21 mW Pipelined SAR ADC Using Single-Ended 1.5-bit/cycle Conversion Technique*. Solid-State Circuits, IEEE Journal of, 2011. **46**(6): p. 1360-1370.

- 50. Alpman, E., et al. A 1.1V 50mW 2.5GS/s 7b Time-Interleaved C-2C SAR ADC in 45nm LP digital CMOS. in Solid-State Circuits Conference Digest of Technical Papers, 2009. ISSCC 2009. IEEE International. 2009.

- 51. Wang, Q., A 1.25 GS/S 8-BIT TIME-INTERLEAVED C-2C SAR ADC FOR WIRELINE RECEIVER APPLICATIONS. 2013, University of Toronto.

- 52. Singh, S.P., A. Prabhakar, and A.B. Bhattcharyya, *C-2C ladder-based D/A converters for PCM codecs*. Solid-State Circuits, IEEE Journal of, 1987. **22**(6): p. 1197-1200.

- 53. Hoonki, K., et al. A low power consumption 10-bit rail-to-rail SAR ADC using a C-2C capacitor array. in Electron Devices and Solid-State Circuits, 2008. EDSSC 2008. IEEE International Conference on. 2008.

- 54. L. Cong, "Pseudo C-2C ladder-based data converter technique. IEEE Transaction on Circuits and Systems. II, 2001. **48**(10): p. 927-929.

- 55. Chen, F., et al. A low-power area-efficient switching scheme for charge-sharing DACs in SAR ADCs. in Custom Integrated Circuits Conference (CICC), 2010 IEEE. 2010.

- 56. Ogawa, T., et al. Non-binary SAR ADC with digital error correction for low power applications. in Circuits and Systems (APCCAS), 2010 IEEE Asia Pacific Conference on. 2010.

- 57. Jen-Huan, T., et al. A 1-V, 8b, 40MS/s, 113uW charge-recycling SAR ADC with a 14uW asynchronous controller. in VLSI Circuits (VLSIC), 2011 Symposium on. 2011.

- 58. Sun-II, C. and Y. Euisik. A low-power area-efficient 8 bit SAR ADC using dual capacitor arrays for neural microsystems. in Engineering in Medicine and Biology Society, 2009. EMBC 2009. Annual International Conference of the IEEE. 2009.

- 59. Young-Kyun, C., et al., A 9-bit 80 MS/s Successive Approximation Register Analog-to-Digital Converter With a Capacitor Reduction Technique. Circuits and Systems II: Express Briefs, IEEE Transactions on, 2010. **57**(7): p. 502-506.

- 60. Jun, M., et al. A low power 10-bit 100-MS/s SAR ADC in 65nm CMOS. in ASIC (ASICON), 2011 IEEE 9th International Conference on. 2011.

- 61. Arian, A., M. Saberi, and S. Hosseini-Khayat. Successive approximation ADC with redundancy using split capacitive-array DAC. in Electrical Engineering (ICEE), 2011 19th Iranian Conference on. 2011.

- 62. Seong-Jin, C., et al. A 10-Bit, 50 MS/s, 55 fJ/conversion-step SAR ADC with split capacitor array. in ASIC (ASICON), 2011 IEEE 9th International Conference on. 2011.

- 63. Xiaolei, Z., et al. A 9-bit 100MS/s tri-level charge redistribution SAR ADC with asymmetric CDAC array. in VLSI Design, Automation, and Test (VLSI-DAT), 2012 International Symposium on. 2012.

- 64. Guo, W. and S. Mirabbasi. A low-power 10-bit 50-MS/s SAR ADC using a parasitic-compensated split-capacitor DAC. in Circuits and Systems (ISCAS), 2012 IEEE International Symposium on. 2012.

- 65. Huynh, A.T., et al. Design of a capacitive DAC mismatch calibrator for split SAR ADC in 65 nm CMOS. in Microwave Conference Proceedings (APMC), 2013 Asia-Pacific. 2013: IEEE.

- 66. Um, J.-Y., et al., A Digital-Domain Calibration of Split-Capacitor DAC for a Differential SAR ADC Without Additional Analog Circuits. 2013.

- 67. Yanfei, C., S. Tsukamoto, and T. Kuroda. A 9b 100MS/s 1.46mW SAR ADC in 65nm CMOS. in Solid-State Circuits Conference, 2009. A-SSCC 2009. IEEE Asian. 2009.

- 68. Li, Y. and Y. Lian, *Improved binary-weighted split-capacitive-array DAC for high-resolution SAR ADCs*. Electronics Letters, 2014. **50**(17): p. 1194-1195.

- 69. Zhu, Y., et al., Split-SAR ADCs: improved linearity with power and speed optimization. 2013.

- 70. Yan, Z., et al., A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS. Solid-State Circuits, IEEE Journal of, 2010. **45**(6): p. 1111-1121.

- 71. Zheng, Y., et al., A Novel Two-Split Capacitor Array with Linearity Analysis for High-Resolution SAR ADCs. 2015.

- 72. Huynh, A.T., et al. Design and implementation of an 11-bit 50-MS/s split SAR ADC in 65 nm CMOS. in Circuits and Systems (ISCAS), 2014 IEEE International Symposium on. 2014: IEEE.

- 73. Guo, Y., et al., *Non-binary Digital calibration for split-capacitor DAC in SAR ADC.* IEICE Electronics Express, 2015(0).

- 74. Lin, J.-Y. and C.-C. Hsieh, A 0.3 V 10-bit 1.17 f SAR ADC With Merge and Split Switching in 90 nm CMOS. 2015.

- 75. Ma Jun, Guo Yawei, and Wu Yue, A 1-V 10-bit 80-MS/s 1.6-mW SAR ADC in 65-nm GP CMOS. Journal of Semiconductors, 2013. 34(8): 085014.

- 76. Zhu, Y., et al. A power-efficient capacitor structure for high-speed charge recycling SAR ADCs. in Electronics, Circuits and Systems, 2008. ICECS 2008. 15th IEEE International Conference on. 2008: IEEE.

- 77. Allen, P.E. and D.R. Holberg, *CMOS analog circuit design*. 2002: Oxford Univ. Press.

- 78. A. Agnes, et al., A 9.4-ENOB 1V 3.8µW 100kS/s SAR ADC with Time-Domain Comparator, in ISSCC Dig. Tech. Papers. 2008. p. 246-610.

- 79. Yanfei, C., et al. Split capacitor DAC mismatch calibration in successive approximation ADC. in Custom Integrated Circuits Conference, 2009. CICC '09. IEEE. 2009.

- 80. Ying-Zu, L., et al. A 0.9-V 11-bit 25-MS/s binary-search SAR ADC in 90-nm CMOS. in Solid State Circuits Conference (A-SSCC), 2011 IEEE Asian. 2011.

- 81. Jun, M., et al., *A 1-V 10-bit 80-MS/s 1.6-mW SAR ADC in 65-nm GP CMOS*. Journal of Semiconductors, 2013. **34**(8): p. 085014.

- 82. Um, J.-Y., et al. Digital-domain calibration of split-capacitor DAC with no extra calibration DAC for a differential-type SAR ADC. in Solid State Circuits Conference (A-SSCC), 2011 IEEE Asian. 2011: IEEE.

- 83. Liu, C.-C., et al. A 0.92mW 10-bit 50-MS/s SAR ADC in 0.13um CMOS process. in VLSI Circuits, 2009 Symposium on. 2009.

- 84. Chun-Cheng, L., et al., A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure. Solid-State Circuits, IEEE Journal of, 2010. **45**(4): p. 731-740.

- 85. Hariprasath, V., et al., *Merged capacitor switching based SAR ADC with highest switching energy-efficiency*. Electronics Letters, 2010. **46**(9): p. 620-621.

- 86. Lee, B.G. and S.G. Lee, *Input-tracking DAC for low-power high-linearity SAR ADC*. Electronics Letters, 2011. **47**(16): p. 911-913.

- 87. Kuo, C.H. and C.E. Hsieh, *Floating capacitor switching SAR ADC*. Electronics Letters, 2011. **47**(13): p. 742-743.

- 88. Yuan, C. and Y. Lam, *Low-energy and area-efficient tri-level switching scheme for SAR ADC*. Electronics Letters, 2012. **48**(9): p. 482-483.

- 89. Zhu, Z., Y. Xiao, and X. Song, *VCM-based monotonic capacitor switching scheme for SAR ADC*. Electronics Letters, 2013. **49**(5): p. 327-329.

- 90. Sanyal, A. and N. Sun, *SAR ADC architecture with 98% reduction in switching energy over conventional scheme*. Electronics Letters, 2013. **49**(4): p. 248-250.

- 91. Wu, Y., X. Cheng, and X. Zeng, A 960μW 10-bit 70-MS/s SAR ADC with an energy-efficient capacitor-switching scheme. Microelectronics Journal, 2013. 44(12): p. 1260-1267.

- 92. Kim, J.E., et al., Energy-efficient charge-average switching DAC with floating capacitors for SAR ADC. Electronics Letters, 2014. **50**(16): p. 1131-1132.

- 93. Xie, L., et al., *Energy-efficient hybrid capacitor switching scheme for SAR ADC*. Electronics Letters, 2014. **50**(1): p. 22-23.

- 94. Wenbo, L., H. Pingli, and C. Yun. A 12b 22.5/45MS/s 3.0mW 0.059mm<sup>2</sup> CMOS SAR ADC achieving over 90dB SFDR. in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010 IEEE International. 2010.

- 95. Chun-Cheng, L., et al. A 10b 100MS/s 1.13mW SAR ADC with binary-scaled error compensation. in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010 IEEE International. 2010.

- 96. Hashemi, S. and B. Razavi, *Analysis of Metastability in Pipelined ADCs*. 2014.

- 97. Kull, L., et al. A 3.1mW 8b 1.2GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32nm digital SOI CMOS. in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International. 2013.

- 98. Wenbo, L., H. Pingli, and C. Yun, A 12-bit, 45-MS/s, 3-mW Redundant Successive-Approximation-Register Analog-to-Digital Converter With Digital Calibration. Solid-State Circuits, IEEE Journal of, 2011. 46(11): p. 2661-2672.

- 99. Van der Plas, G. and B. Verbruggen, A 150 MS/s 133uW 7 bit ADC in 90 nm Digital CMOS. Solid-State Circuits, IEEE Journal of, 2008. 43(12): p. 2631-2640.

- 100. Shikata, A., et al., A 0.5 V 1.1 MS/sec 6.3 fJ/Conversion-Step SAR-ADC With Tri-Level Comparator in 40 nm CMOS. Solid-State Circuits, IEEE Journal of, 2012. 47(4): p. 1022-1030.

- 101. Cho, T.B. and P.R. Gray, A 10 b, 20 Msample/s, 35 mW pipeline A/D converter. Solid-State Circuits, IEEE Journal of, 1995. vol. 30(3): p. 166-172.

- 102. Nicodimus, R.A., S. Takagi, and N. Fujii, *Reduction of bootstrapped switch area consumption using pre-charge phase*. IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 2008. **91**(2): p. 476-482.

- 103. Ong, A.K., V.I. Prodanov, and M. Tarsia. A method for reducing the variation in " on" resistance of a MOS sampling switch. in Circuits and Systems, 2000. Proceedings. ISCAS 2000 Geneva. The 2000 IEEE International Symposium on. 2000.

- 104. Sangwook, K. and E. Greeneich. Body effect compensated switch for low voltage switched-capacitor circuits. in Circuits and Systems, 2002. ISCAS 2002. IEEE International Symposium on. 2002.

- 105. Peng, Y., D. Kong, and F. Zhou. A Low-Voltage Sampling Switch with Improved Linearity. in Electrical and Computer Engineering, 2006. CCECE'06. Canadian Conference on. 2006: IEEE.

- 106. Behradfar, A., S. Zeinolabedinzadeh, and K. HajSadeghi. A clock boosting scheme for low voltage circuits. in Electronics, Circuits and Systems, 2008. ICECS 2008. 15th IEEE International Conference on. 2008.

- 107. Wang, L., et al., *Dual-channel bootstrapped switch for high-speed high-resolution sampling*. Electronics Letters, 2006. **42**(22): p. 1275-1276.

- 108. Ginsburg, B.P. and A.P. Chandrakasan, 500-MS/s 5-bit ADC in 65-nm CMOS with split capacitor array DAC. Solid-State Circuits, IEEE Journal of, 2007. 42(4): p. 739-747.

- 109. Saberi, M., et al., *Analysis of power consumption and linearity in capacitive digital-to-analog converters used in successive approximation ADCs*. Circuits and Systems I: Regular Papers, IEEE Transactions on, 2011. **58**(8): p. 1736-1748.

- 110. Sauerbrey, J., D. Schmitt-Landsiedel, and R. Thewes, *A 0.5-ν 1-μw successive approximation ADC*. Solid-State Circuits, IEEE Journal of, 2003. **38**(7): p. 1261-1265.

- 111. McNeill, J.A., et al., "Split ADC" Calibration for All-Digital Correction of Time-Interleaved ADC Errors. Circuits and Systems II: Express Briefs, IEEE Transactions on, 2009. **56**(5): p. 344-348.

- McNeill, J.A., et al., *All-Digital Background Calibration of a Successive Approximation ADC Using the "Split ADC" Architecture.* Circuits and Systems I: Regular Papers, IEEE Transactions on, 2011. **58**(10): p. 2355-2365.

- 113. http://www.mosis.com.

- 114. <a href="http://ptm.asu.edu/">http://ptm.asu.edu/</a>.

- 115. Morshed, T.H., et al., BSIM4v4. 7 MOSFET Model.

- 116. Montanaro, J., et al., *A 160-mhz, 32-b, 0.5-w CMOS RISC microprocessor*. Solid-State Circuits, IEEE Journal of, 1996. **31**(11): p. 1703-1714.

- 117. Miyahara, M., et al., *A low-noise self-calibrating dynamic comparator for high-speed ADCs*. Proc. A-SSCC, 2008: p. 269-272.

- 118. Shubin, L., et al., A high speed low power low offset dynamic comparator used in SHA-less pipelined ADC. Journal of Semiconductors, 2014. 5: p. 022.

- 119. Jeon, H., Low-power high-speed low-offset fully dynamic CMOS latched comparator. 2010.

- 120. BALLA, P. and Y.D. YKUNTAM, *High Speed and Low Power Double-Tail Comparator using Switching Transistor*. 2014.

- 121. Nuzzo, P., et al., *Noise analysis of regenerative comparators for reconfigurable ADC architectures*. Circuits and Systems I: Regular Papers, IEEE Transactions on, 2008. **55**(6): p. 1441-1454.

- 122. Nikoozadeh, A.M., An analysis of latch comparator offset due to load capacitor mismatch. 2006.

- 123. Katyal, V., R.L. Geiger, and D.J. Chen. A new high precision low offset dynamic comparator for high resolution high speed ADCs. in Circuits and Systems, 2006. APCCAS 2006. IEEE Asia Pacific Conference on. 2006: IEEE.

- 124. He, J., et al., Analyses of static and dynamic random offset voltages in dynamic comparators. Circuits and Systems I: Regular Papers, IEEE Transactions on, 2009. **56**(5): p. 911-919.

- 125. Hao-Chiao, H. and L. Guo-Ming, *A 65-fJ/Conversion-Step 0.9-V 200-kS/s Rail-to-Rail 8-bit Successive Approximation ADC*. Solid-State Circuits, IEEE Journal of, 2007. **42**(10): p. 2161-2168.

- 126. Razavi, B., *Design of analog CMOS integrated circuits*. 2002: Tata McGraw-Hill Education.

- 127. Yin, G., F. Op't Eynde, and W. Sansen, *A high-speed CMOS comparator with 8-b resolution*. Solid-State Circuits, IEEE Journal of, 1992. **27**(2): p. 208-211.

- 128. sobhi, j., Design and Implementation of a 280 MS/sec 12-bit CMOS Parallel Successive-Approximation Analog-to-Digital Converter, in electrical faculty. 2006, urmia university: urmia.

- 129. National Semiconductor Application Note 1205 "Electrical Performance of Packages", <a href="http://www.ti.com/lit/an/snoa405a/snoa405a.pdf">http://www.ti.com/lit/an/snoa405a/snoa405a.pdf</a>, 2004.

- 130. Pretzl, G., *Dynamic testing of high-speed A/D converters*. Solid-State Circuits, IEEE Journal of, 1978. **13**(3): p. 368-371.

- 131. Walden, R.H., *Analog-to-digital converter survey and analysis*. Selected Areas in Communications, IEEE Journal on, 1999. **17**(4): p. 539-550.

- 132. Murmann, B., "ADC Performance Survey 1997-2014," [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

- 133. Morie, T., et al. A 71dB-SNDR 50MS/s 4.2mW CMOS SAR ADC by SNR enhancement techniques utilizing noise. in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International. 2013.

- 134. Owens, B.E., et al., Simulation and measurement of supply and substrate noise in mixed-signal ICs. Solid-State Circuits, IEEE Journal of, 2005. **40**(2): p. 382-391.

- 135. Huang, G. and P. Lin, A 15fJ/conversion-step 8-bit 50MS/s asynchronous SAR ADC with efficient charge recycling technique. Microelectronics Journal, 2012. **43**(12): p. 941-948.

- 136. Harpe, P., et al. A 30fJ/conversion-step 8b 0-to-10MS/s asynchronous SAR ADC in 90nm CMOS. in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010 IEEE International. 2010.

- 137. Harpe, P.J.A., et al., A 26 uW 8 bit 10 MS/s Asynchronous SAR ADC for Low Energy Radios. Solid-State Circuits, IEEE Journal of, 2011. **46**(7): p. 1585-1595.

- 138. Rabuske, T.G., C.R. Rodrigues, and S. Nooshabadi, *A 5MSps 8-bit SAR ADC with single-ended or differential input.* Microelectronics Journal, 2012. **43**(10): p. 680-686.

- 139. Lee, B.-G., Power and Bandwidth Scalable 10-b 30-MS/s SAR ADC. 2015.

- 140. Malki, B., et al. A 70dB DR 10b 0-to-80MS/s current-integrating SAR ADC with adaptive dynamic range. in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2012 IEEE International. 2012.

- 141. Yoshioka, M., et al. A 10b 50MS/s 820uW SAR ADC with on-chip digital calibration. in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010 IEEE International. 2010.

- 142. Cao, T.-V., S. Aunet, and T. Ytterdal. A 9-bit 50MS/s asynchronous SAR ADC in 28nm CMOS. in NORCHIP, 2012. 2012: IEEE.

- 143. Han, X., et al. A single channel, 6-bit 410-ms/s asynchronous SAR ADC based on 3bits/stage. in New Circuits and Systems Conference (NEWCAS), 2014 IEEE 12th International. 2014: IEEE.

- 144. Deng, H. and P. Li. A 8-bit 10MS/s asynchronous SAR ADC with resistor-capacitor array DAC. in Anti-counterfeiting, Security, and Identification (ASID), 2014 International Conference on. 2014: IEEE.