# Design and Simulation of a High Performance Lateral BJTs on TFSOI

Ismail Saad and Razali Ismail

Faculty of Electrical Engineering, University Technology Malaysia, 81310, Skudai, Johor Bharu, E-mail: <u>ismail s@ums.edu.my</u>, <u>razali@fke.utm.my</u>

Abstract Lateral BJT's have received renewed interest with the advent of BiCMOS and Silicon on Insulator (SOI) technology. It's been reported in [1] that a 67 GHz  $f_{max}$ novel lateral BJT's on TFSOI has been fabricated with a simplified process. This paper presents an investigation of this high performance transistor by using 2D process and device numerical simulation. Accurate geometrical structure and reasonably good doping profiles with a simple fabrication process are successfully achieved in the simulation. However, a careful process attention is required to define the mesh for the device to obtain an accurate measurement of device characteristics. With a base, low-doped collector, emitter and high-doped collector concentrations of 3 x  $10^{17}$  cm<sup>-3</sup>, 1.0 x  $10^{17}$  cm<sup>-3</sup>, 5 x  $10^{20}$  cm<sup>-3</sup> and 3 x  $10^{20}$  cm<sup>-3</sup> respectively, a variation of 0.1- 0.13µm base width is observed. I-V and frequency performance of these transistors are simulated and analyzed. Y-parameter measurement at frequency 10 MHz - 1000 GHz shows a 21 GHz fmax was successfully achieved at V<sub>BE</sub>=0.7V, V<sub>CE</sub>=2.0V and  $I_{CE}$ =6.0  $\mu$ A.

#### I. INTRODUCTION

Most existing BiCMOS processes combine highperformance vertical BJT's with MOSFET's. These technologies offer a trade-off between speed and power dissipation and attain digital/analog systems with a performance exceeding that of circuits based on either technology alone [2, 3]. This results in a rather complex and expensive process due to the technological incompatibility of two types of transistors [4]. Several sophisticated technologies such as self-aligned double-polysilicon structure [5], shallow and/or deep trench isolation [6] and an epitaxial base [7] has been used. However, such superior process technologies increase fabrication costs of RF LSI's. Consequently, the cost of the extra steps to produce the buried layer and epitaxial collector vertical bipolar transistors

has also limited BiCMOS LSI's marketability [8]. With the advantages of low power and high speed operation and simpler integration of devices, Silicon on Insulator (SOI) has become an excellent candidate as an alternative substrate for BiCMOS circuits. Furthermore, the use of SOI as a substrate in BiCMOS circuits is dependent on the development of a proper bipolar device (in a lateral structure) on SOI [9]. A number of novel high performance lateral bipolar's on SOI have been proposed and implemented. All of these transistors have been fabricated with a different approach of structure. This paper presents an investigation of a high performance transistor by carrying 2D process and device numerical simulation [10]. With a base, low-doped collector, emitter and highdoped collector concentrations of 3 x  $10^{17}$  cm<sup>-3</sup>, 1.0 x  $10^{17}$  cm<sup>-3</sup>, 5 x  $10^{20}$  cm<sup>-3</sup> and 3 x  $10^{20}$  cm<sup>-3</sup> respectively, a variation of 0.1- 0.13µm base width is observed. I-V and Frequency performance of these transistors are simulated and analyzed. Y-parameter measurement at frequency 10 MHz - 1000 GHz shows a 21 GHz  $f_{max}$  was successfully achieved at V<sub>BE</sub>=0.7V,  $V_{CE}$ =2.0V and  $I_{CE}$ =6.0  $\mu$ A.

#### II. DEVICE STRUCTURE AND PROCESS

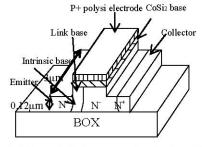

Figure 1 shows the schematic structure of the lateral bipolar transistor considered in the present study.

Fig. 1 Schematic 3D cross-sectional view of lateral BJT

The intrinsic base is formed by an angled  $(45^{\circ})$  boron and BF<sub>2</sub> ion implantation with the condition of BF<sub>2</sub>  $1.2 \times 10^{12}$  cm<sup>-2</sup> at 25KeV, boron

$2 \times 10^{12}$  cm<sup>-2</sup> at 15 KeV and boron 7.2x10<sup>12</sup> cm<sup>-2</sup> <sup>2</sup>at 35 KeV. This gives a flat profiled intrinsic base in the direction of the depth and also provides a link between intrinsic base and the p+ poly Si electrode. The length of this self-aligned link base is about 0.07 µm. An anisotropic poly Si etching process is used to form the poly Si sidewall. The emitter region is formed by ion implantation of phosphorus under the condition of 8.0x10<sup>15</sup>cm<sup>-2</sup> at 65KeV and N<sup>+</sup> collector is obtained by implanting phosphorus dose of 4.0x10<sup>15</sup>cm<sup>-2</sup> at 60KeV. RTA for 20 seconds at 950°C is applied to activate the doped impurities. Note that each of the emitter, base and collector regions has to be diffused and penetrated deeply into buried oxide. This is to maintain neutral charge within emitter/base, base/N<sup>-</sup> collector and N collector/N<sup>+</sup> collector depletion regions and to reduce the junction capacitances. TEOS SiO<sub>2</sub> is then deposited over the transistor for isolation. Cobalt Silicide ( $CoSi_2$ ) is used on the exposed p+ poly-Si to reduce the base resistance. TEOS SiO<sub>2</sub> is deposited again and conventional wiring process is carried out.

The Drift-Diffusion transport model with simplified Boltzmann carrier statistics is employed for numerical computation of the device design [10]. The bandgap narrowing effects in heavy doping surroundings has also taken into account. The standard carrier low electric field mobility concentration dependent and its smooth transition to a high electric field for carrier velocity saturation effects in the direction of current flow models was all switch on. The Auger recombination model combined with SRH model (Shockley-Read-Hall) in concentration dependent carrier lifetimes was also selected for characterization of the device [10]. The workfunction of p+ polysilicon with CoSi<sub>2</sub> is given for base electrode contact.

### III. RESULTS AND DISCUSSION

## Doping Profiles

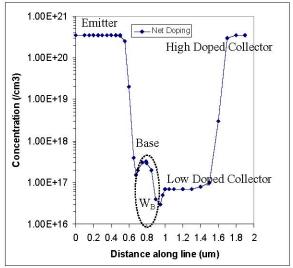

Horizontal doping profile at the center of device is shown in figure 2, impurity concentration of intrinsic base is  $3 \times 10^{17}$  cm<sup>-3</sup>. Both emitter and high-doped collector concentrations are at  $4 \times 10^{20}$ cm<sup>-3</sup> and  $3 \times 10^{20}$  cm<sup>-3</sup> respectively. Also, a slight variation in base width, W<sub>B</sub> (0.1– 0.13µm) as a function of depth is observed. For a better result, a narrow W<sub>B</sub> is vital in making sure that the injected carriers from emitter will reach the

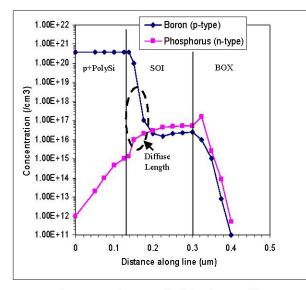

depletion region of B/C junction to be swept across the junction into collector region. Thus, an optimized doping profile of base region is very important for definition of narrow base width, W<sub>B</sub>. In addition, the vertical impurity profile of the base p+ polysi and n- collector region are also investigated as shown in Figure 3. A flat boron concentration of 2.5 x 10<sup>20</sup> cm<sup>-3</sup> is obtained in p+poly region. As shown in the figure, the boron has diffused into n- collector laver with the junction depth of 63 nm from the interface between p+poly and n<sup>-</sup> collector. This diffusion length is an important factor for the high frequency performance of transistor. The diffusion of boron into n collector causes the decrease of cross-sectional area of collector region, which results in the increase of the collector current density. Consequently, the  $f_T$ -I<sub>C</sub> curve falls down earlier as the collector current is increased mainly due to the Kirk effect. However, this will accordingly decrease the breakdown voltage. Thus, the trade-off between increasing doping level of collector region for a higher frequency or faster circuit and high value of breakdown voltage must be carefully optimized.

In overall a trade-off between decreasing the base region and increasing the collector region doping profile for definition of a narrow base width,  $W_B$  and minimizing the kirk effect in a reduce series collector resistance is essential for getting a higher frequency performance and more faster circuit operation.

Fig. 2 Horizontal doping profile at the center of device

Fig. 3 Transistor vertical doping profiles

### Device Characteristics

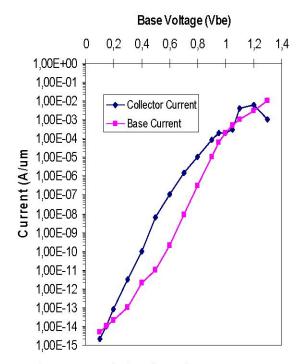

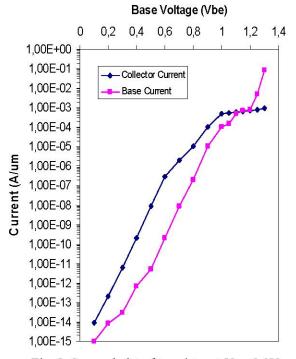

By using ATLAS DC solutions, the transistor's Gummel plot is obtained (Figure 4) at  $V_{CE}$ = 2.0V and  $V_{BE}$ = 0.4 – 1.5V. The emitter area is taken as 0.36  $\mu$ m<sup>2</sup>. I<sub>C</sub> equal to 0.2 x 10<sup>-8</sup>A/ $\mu$ m and 3 x 10<sup>-4</sup>A/ $\mu$ m and I<sub>B</sub> equal to 6x10<sup>-10</sup>A/ $\mu$ m and 6x10<sup>-7</sup>A/ $\mu$ m at V<sub>BE</sub>=0.6V and 0.8V, are exhibited respectively. Consequently, a gain of about 350 is obtained at V<sub>BE</sub>=0.6V. I<sub>C</sub> saturates at 2x10<sup>-4</sup>A, due to high series collector resistance and kirk effect.

Fig. 4. Gummel plot of transistor at  $V_{CE}$ =2.0V&  $V_{BE}$ =0.4-1.5V with  $N_{AB}$ = 3x10 <sup>17</sup>cm<sup>-3</sup>, N<sup>-</sup>  $_{DC}$ =1x10<sup>17</sup>cm<sup>-3</sup> and β=350 at  $V_{BE}$ =0.6V

This effect is minimized in the second transistor simulation by increasing the low-doped collector concentration from  $1 \times 10^{17} \text{ cm}^{-3}$  to  $5 \times 10^{17} \text{ cm}^{-3}$  and base region to  $2 \times 10^{18} \text{ cm}^{-3}$  with  $W_B \approx 0.12 \mu \text{m}$ . This resulted in a higher I<sub>C</sub> saturation at  $7 \times 10^{-4}$  A/ $\mu$ m and a larger gain (1000) (Figure 5) at the cost of decreasing the E-C breakdown voltage (BV<sub>CEO</sub>  $\approx$  4V) obtained from the output characteristics of the device.

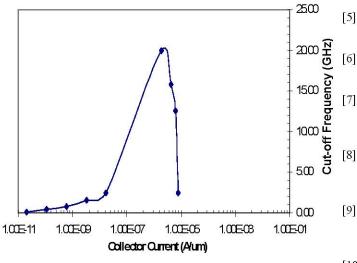

Figure 6 shows the cut-off frequency,  $f_T$  obtained from y-parameter measurements at frequency 10 MHz - 1000 GHz. A peak  $f_T$  ( $f_{MAX}$ ) of 21 GHz at  $I_{CE}$ =6.0  $\mu$ A is observed for the simulated transistor. With  $f_{MAX}$  of 21 GHz and gain of 350 – 1000, an excellent process and device simulation characteristics of the lateral bipolar transistor have been accomplished.

Fig. 5. Gummel plot of transistor at  $V_{CE}$ =2.0V and  $V_{BE}$ =0.4-1.5V with  $N_{AB}$ = 2x10 <sup>18</sup>cm<sup>-3</sup>,  $N_{DC}^{-}$ =5x10<sup>17</sup>cm<sup>-3</sup> and  $\beta$ =1000 at  $V_{BE}$ =0.6V

Fig. 6.  $f_{T}$ -I<sub>CE</sub> ( $f_{TMAX}$ ) characteristics of transistor at V<sub>CE</sub>=2.0V

IV. CONCLUSION

The simulation of a high performance lateral bipolar transistor on Thin Film Silicon-On-Insulator (TFSOI) has been successfully carried out. Both process and device simulations for lateral bipolar transistors are carried out in order to understand the device performance. In process simulation, reasonably good doping profiles have been successfully accomplished. In device simulation, the current-voltage (I-V), typical output characteristics and frequency performance of lateral bipolar transistor have been obtained. With increasing  $N_{DC}$  with a factor of less than 5 (5x10<sup>17</sup>cm<sup>-3</sup>) and reducing N<sub>AB</sub> by a factor of less than 10 (2x10<sup>18</sup>cm<sup>-3</sup>) the I<sub>Csat</sub> has been pushed to occur at 7x10<sup>-4</sup>A with V<sub>BE</sub>=1.1V. Thus, a higher gain of 1000 is obtained with a decreasing value of BV<sub>CEO</sub>≈ 4.0V. However, for both cases the  $f_{MAX}$  of 21 GHz has been obtained and a gain of 350 up to 1000 is observed respectively.

### REFERENCES

- H. Nii et. al, "A Novel Lateral Bipolar Transistor with 67 GHz f<sub>max</sub> on Thin-Film SOI for RF Analog Applications", IEEE Transactions on electron devices, vol.47. no.7, July 2000

- devices, vol.47. no.7, July 2000

[2] S. Parke et. al, "A Versatile, SOI BiCMOS Technology with Complementary Lateral BJT's", 1992 IEDM Technical Digest, p.92-453

- [3] M. Kumar et. al, "A Simple, High Performance TFSOI Complementary BiCMOS Technology for Low Power Wireless Applications", IEEE Transactions on electron devices, May 2001

- [4] A. Tamba et. al, "A Novel CMOS- Compatible Lateral Bipolar Transistor for High-Speed BiCMOS LSP", 1990 IEDM Technical Digest, p.90-395

- R. Dekker et. al, "An Ultra Low Power Lateral Bipolar Polysilicon Emitter Technology on SOI", 1993 IEDM Technical Digest, p.75

- G.G. Shahidi et. al, "A Novel High-Performance Lateral Bipolar on SOI", 1991 IEDM Technical Digest, p.91-663

- [7] B. Edholm et. al, "Very High Current Gain Enhancement by Substrate Biasing of Lateral Bipolar Transistors on Thin SOI", 1993 Elsevier Science Publishers B.V, p.379-382

- 8] R. Gomez et. al, "On the Design and Fabrication of Novel Lateral Bipolar Transistor in a Deep-Submicron Technology", Elsevier Science, September 1999

- [9] B. Edholm et. al, "A Self-Aligned Lateral Bipolar Transistor Realized on SIMOX-material", IEEE Transactions on electron devices, vol. 40, no.12, December 1993

- [10] Silvaco International, "ATLAS and ATHENA user Manual DEVICE SIMULATION SOFTWARE"