# ETCHING PERFORMANCE OF SILICON WAFERS WITH REDESIGNED ETCHING DRUM

### ROZZETA BT DOLAH

A project submitted as a partial fulfillment of the requirements for the award of the degree of Master of Engineering (Advanced Manufacturing Technology)

Faculty of Mechanical Engineering Universiti Teknologi Malaysia

# Specially dedicated to;

My husband; Mohd. Nazri b Ahmad, my daughter; Nurin Jeslina, my mother; Hjh. Kalsom bt Md. Yusof, my younger sister; Nur Fatin bt Dolah, my younger brother; Mohd. Yusrie, b Dolah and my entire colleagues.....

### ACKNOWLEDGEMENT

In the name of Allah the Almighty and Merciful

I am deeply indebted to many individuals who contributed to this project. Special thanks to my supervisor, Associate Professor Dr. Hamidon b Musa, for his continuous support, motivation and guidance in completing this project. I also would like to thanks Encik Daud b Bunal and Encik Abd. Mujib for his assistence in handling acid etching machine and contributing useful ideas in solving problems. To Pn. Norlina thanks a lot, who has helped me analyzing the data using Design of Experiment (DOE) through STAGRAPHIC software. Last but not least, thanks to all academicians and technicians for all the help and cooperation. Finally, a huge thank for my entire colleagues.

Wassalam.

#### **ABSTRACT**

Etching process involves various chemical reactions and reflects significantly on silicon wafer quality. This master project addresses the major problem on wafers during etching that is wafer removal distribution throughout etching drum compartment. The etching drum has been redesigned to overcome the lower removal problem at the end of each compartment. The characteristics of the end wafers are compared with other wafers in the compartment to study the etching difference that leads to this problem. Etching parameters are then evaluated in order to optimize the etching process in conjunction with the use of this new drum. For optimization purpose is by applying Design of Experiment (DOE) with full factorial design is employed. Etching factors namely the bubbling flow rate, wafer rotation, and etchant temperature had been varied in 11 runs in the DOE. The responses studied etching removal, total thickness variation (TTV) and wafer brightness. It is found that etchant temperature gives major a impact on all three responses stated above. The etchant temperature is the main effect factor and significantly affects TTV. Additionally, the etchant temperature and bubbling flow rate provide interaction effect on both the etching removal and wafer brightness. A higher bubbling flow rate is required to ensure etching removal and brightness within specification. Besides studying these three responses, the wafer surface after etching is additionally analyzed using ADE Infotool software which captures the etched profile and its thickness. From the ADE result, it again indicates that a higher temperature contributes to a more concave shape of etched wafer, thus resulting in higher TTV sending the wafers to be out of specification. Finally, the optimum condition is tested on a final run utilizing all the four compartments. The uniformity without lower removal at the end compartment is observed in removal distribution graph. The new drum design performance is enhanced with the optimized value of bubbling flow rate, etchant temperature and wafer rotation to achieve the best removal distribution.

#### **ABSTRAK**

Proses Punaran (Etching) melibatkan pelbagai tindak balas kimia dan memberi kesan yang ketara terhadap kualiti wafer. Projek sarjana ini mengenalpasti masalah utama dalam proses punaran terhadap wafer, iaitu penyingkiran silikon yang tidak sekata dalam keempat-empat kompatmen pada drum wafer. Rekabentuk drum diubah untuk mengatasi masalah ini. Profil permukaan wafer dianalisis dan dibandingkan dengan wafer di bahagian tengah drum untuk menganalisa perbezaan profile keduanya dan kaitannya dengan masalah ini. Parameter punaran dianalisa untuk menyelaraskan perubahan drum baru untuk mencapai proses punaran yang optimum. Kaedah eksperimen yang digunakan adalah "Design of Experiment" (DOE) dengan kaedah faktorial penuh. Faktor punaran seperti kadar aliran buih, pusingan wafer dan suhu asid dipelbagaikan dalam 11 set eksperimen. Kesan faktor-faktor ini melibatkan penyingkiran silikon, jumlah variasi ketebalan (TTV), dan kecerahan wafer. Keputusan DOE mendapati suhu acid adalah factor yang paling berpengaruh ke atas ketiga-tiga kesan proses punaran yang disebutkan tadi. Suhu asid adalah faktor utama yang paling signifikan terhadap TTV. Manakala suhu asid dan kadar aliran buih memberikan kesan menyaling terhadap peyingkiran silicon dan kecerahan wafer. Kadar aliran buih yang tinggi diperlukan untuk memastikan penyingkiran silicon dan kecerahan wafer dalam spesifikasi. Di samping keputusan itu, profil permukaan wafer selepas punaran dianalisis menggunakan perisian ADE Infotool yang memberi keputusan profail wafer dan perubahan ketebalan wafer sepanjang keratan rentas. Daripada keputusan ADE, suhu asid yang tinggi sekali lagi menunjukkan kesan yang ketara terhadap profil wafer. Suhu asid yang tinggi memberikan profil yang cerun ke dalam wafer, dan ini sekaligus menjadikan TTV keluar dari spesifikasinya. Akhir sekali, nilai optimum yang diperolehi dari DOE tadi dijalankan ke atas ekeperimen yang terakhir untuk menilai pencapaian keempat-empat kompatmen. Keseragaman tanpa penyingkiran silikon yang rendah di tepi setiap kompatmen dapat dicapai. Rekabentuk drum yang baru ini diperkukuhkan lagi dengan nilai optimum kadar aliran buih, suhu asid, dan pusingan wafer dalam drum untuk mencapai keseragaman penyingkiran silikon.

# TABLE OF CONTENT

| CHA                | APTER            |                      | PAGE |

|--------------------|------------------|----------------------|------|

|                    |                  |                      |      |

| STA                | TUS OF THE       | SIS                  | i    |

| TITI               | LE PAGE          |                      | ii   |

| DEC                | CLARATION        |                      | iii  |

| DED                | DICATION         |                      | iv   |

| ACK                | ACKNOWLEDGEMENT  |                      |      |

| ABS                | ABSTRACT         |                      |      |

| ABS                | TRAK             |                      | vii  |

| TAE                | TABLE OF CONTENT |                      |      |

| LIST OF TABLES     |                  |                      | xi   |

| LIST               | OF FIGURES       | S                    | xii  |

| LIST OF APPENDICES |                  |                      | XV   |

|                    |                  |                      |      |

|                    |                  |                      |      |

| CHA                | APTER 1:         | INTRODUCTION         |      |

| 1.1                | Background       | i                    | 1    |

| 1.2                | Problem De       | escription           | 4    |

| 1.3                | Objective        |                      | 6    |

| 1.4                | Scope            |                      | 7    |

| CHA                | APTER 2:         | LITERATURE REVIEW    |      |

|                    | •                |                      |      |

| 2.1                | Process Det      | Process Definition 9 |      |

| 2.2                | Research Review  |                      |      |

|                    | 2.2.1 Etch       | ning Temperature     | 23   |

|     | 2.2.2   | Etching Surface Roughness                           | 25 |

|-----|---------|-----------------------------------------------------|----|

|     |         | 2.2.3 Etching method in wafer cleaning process      |    |

|     | 25      |                                                     |    |

|     | 2.2.4   | Micro photonic of silicon wafer                     | 27 |

|     | 2.2.5   | Surface chemistry of N-type Silicon Etching         | 27 |

|     |         |                                                     |    |

|     |         |                                                     |    |

| CHA | PTER 3  | 3: RESEARCH METHODOLGY                              |    |

| 3.1 | Exper   | imental Approach                                    | 30 |

| 3.2 | Desig   | n and Fabrication                                   |    |

|     | 3.2.1   | New Drum with PVC Chips                             | 32 |

|     | 3.2.2   | New Drum with PVC Chips and Narrow Groove           | 33 |

| 3.3 | Initial | Experiment                                          |    |

|     | 3.3.1   | New Drum with PVC Chips                             | 34 |

|     |         | 3.3.1.1 Surface Morphology                          | 35 |

|     | 3.3.2   | New Drum with PVC Chips and Narrow Groove           | 35 |

| 3.4 | Desig   | n of Experiment (DOE)                               | 36 |

|     |         |                                                     |    |

|     |         |                                                     |    |

| CHA | PTER 4  | 4: RESULT AND DISCUSSIONS                           |    |

| 4.1 | Etcha   | nt Chemistry                                        | 38 |

| 4.2 | Existi  | ng Drum Experiment                                  | 39 |

| 4.3 | Initial | Experiment Result a): New Drum                      | 41 |

| 4.4 | Surfac  | ce Morphology                                       | 44 |

| 4.5 | Initial | Experiment Result b): New Drum with Redesign Groove |    |

|     | for Th  | in Wafers                                           | 49 |

| 4.6 | DOE     | result on Etching Performance                       | 54 |

|     | 4.6.1   | Etching Performance on TTV                          | 55 |

|     |         |                                                     |    |

| 4.6.2      | Etching Performance on Removal                         | 57  |

|------------|--------------------------------------------------------|-----|

|            | 4.6.2.1 Effect on Valley Depth (Maximum peak – Minimum |     |

|            | peak on one wafer)                                     | 61  |

| 4.6.3      | Etching Performance on Brightness                      | 65  |

| 4.6.4      | Optimum Condition Evaluation                           | 69  |

|            | 4.6.4.1 Final Experiment Result                        | 70  |

|            | 4.6.4.2 Etching Profile                                | 71  |

| CHAPTER 5  | 5: CONCLUSION                                          | 75  |

| CHAPTER (  | 5: FUTURE RECOMMENDATIONS                              | 77  |

| REFERENC   | ES                                                     | 79  |

| APPENDIX A | A: DOE RUN A                                           | 82  |

| APPENDIX I | B: DOE RUN B                                           | 84  |

| APPENDIX ( | C: DOE RUN C                                           | 86  |

| APPENDIX I | D: DOE RUN D                                           | 88  |

| APPENDIX I | E: DOE RUN E                                           | 90  |

| APPENDIX I | F: DOE RUN G                                           | 92  |

| APPENDIX ( | G: DOE RUN H                                           | 94  |

| APPENDIX I | H: DOE RUN J                                           | 96  |

| APPENDIX I | : DOE RUN K                                            | 98  |

| APPENDIX.  | : DOE RUN FOR FINAL SETTING                            | 100 |

| APPENDIX I | K: Raw Data before Placing PVC Chip                    | 104 |

| APPENDIX I | L: Final Setting Raw Data - REMOVAL (um)               | 105 |

|            | - TTV                                                  | 106 |

|            | - Brightness                                           | 107 |

### LIST OF TABLES

| 36 |

|----|

| 42 |

| 42 |

| 42 |

| 43 |

| 46 |

| 49 |

| 49 |

| 52 |

| 52 |

| 53 |

| 53 |

| 54 |

| 55 |

| 57 |

| 58 |

| 61 |

| 62 |

| 62 |

| 64 |

| 65 |

| 68 |

| 69 |

| 70 |

| 71 |

| 72 |

| 74 |

|    |

### LIST OF FIGURES

| FIGURES<br>PAGI | TITLE                                                         |    |

|-----------------|---------------------------------------------------------------|----|

| ragi            | ע                                                             |    |

| 1.1             | Existing etching drum                                         | 2  |

| 1.2             | Drum being load into etching machine                          | 3  |

| 1.3             | Low spike at beginning end of each compartment                | 5  |

| 1.4             | Low temperature region                                        | 8  |

| 2.1             | Silicon wafer process flow                                    | 10 |

| 2.2             | Float zone (FZ) method                                        | 12 |

| 2.3             | Czochralski (CZ) method                                       | 13 |

| 2.4             | Diamond tip structure                                         | 14 |

| 2.5             | Top view for ingot slicing process                            | 14 |

| 2.6             | Wafer edge profile before grinding                            | 15 |

| 2.7             | Wafer edge profile after grinding                             | 15 |

| 2.8             | Front view of lapping machine                                 | 16 |

| 2.9             | Etchant composition in mixed acid                             | 17 |

| 2.10            | HF and HNO <sub>3</sub> region                                | 18 |

| 2.11            | Bubbling effect on wafer surface                              | 20 |

| 2.12            | Sandblast process schematic diagram                           | 21 |

| 2.13            | Polishing process                                             | 22 |

| 2.14            | Wafer surface difference between before polishing and         |    |

|                 | after polishing                                               | 22 |

| 2.15            | IR spectra on n-Si/HF 0.1 M interface (source from            |    |

|                 | M. Safi et al. 2002)                                          | 28 |

| 2.16            | Hydrogen concentration, CH, for a non-abraded substrate       |    |

|                 | (curve a) and for a sandblasted surface (curve b) vs. etching |    |

|                 | time (source from M. Vergnant et al. 1995)                    | 29 |

| 3.1             | Overall view of new drum with chips                           | 32 |

| 3.2             | Drum cross-section                                            | 32 |

| 3.3             | Normal drum groove                                            | 33 |

| 3.4  | Narrow drum groove                                  | 33 |

|------|-----------------------------------------------------|----|

| 4.1  | Removal distribution before improvement             | 40 |

| 4.2  | Removal distribution after improvement              | 40 |

| 4.3  | Old drum removal distribution                       | 41 |

| 4.4  | New drum removal distribution                       | 41 |

| 4.5  | XKSS 500 new drum                                   | 42 |

| 4.6  | XTUM 527 new drum                                   | 43 |

| 4.7  | WKSS 702 new drum                                   | 43 |

| 4.8  | ADE gap wafer surface profile                       | 44 |

| 4.9  | ADE for without gap wafer profile                   | 45 |

| 4.10 | Statistical analysis on surface roughness           | 47 |

| 4.11 | AFM surface analysis                                | 48 |

| 4.12 | Wafer's gap in normal groove: $R = 0.75 \text{ mm}$ | 50 |

| 4.13 | Wafer's gap in narrow groove: $R = 0.64 \text{ mm}$ | 51 |

| 4.14 | Focus view on wafer's gap on narrow groove          | 51 |

| 4.15 | An example of wafer: YHD 1714 narrow groove drum    | 52 |

| 4.16 | Wafer: YRN 4346 Narrow groove drum                  | 53 |

| 4.17 | Main effect plot for TTV                            | 55 |

| 4.18 | Standardized pareto chart for TTV                   | 56 |

| 4.19 | TTV contours of response surface                    | 56 |

| 4.20 | Main effect plot for etching removal                | 58 |

| 4.21 | Interaction plot for etching removal                | 59 |

| 4.22 | Standardized pareto chart for etching removal       | 59 |

| 4.23 | Removal contours of estimated response surface      | 60 |

| 4.24 | Main effect plot for valley depth                   | 63 |

| 4.25 | Interaction plot for valley depth                   | 63 |

| 4.26 | Standardized pareto chart for valley depth          | 63 |

| 4.27 | Valley depth contours of estimated response surface | 64 |

| 4.28 | Standardized pareto chart for brightness            | 66 |

| 4.29 | Main effect plot for brightness                     | 66 |

| 4.30 | Interaction plot for brightness                     | 67 |

|      |                                                   | xiv |

|------|---------------------------------------------------|-----|

| 4.31 | Brightness contours of estimated response surface | 68  |

| 4.32 | Etching factors impact on target value for TTV,   |     |

|      | Etching removal, and brightness                   | 69  |

| 4.33 | Removal distribution result for final setting     | 71  |

|      |                                                   |     |

### LIST OF APPENDICES

### **APPENDIX**

## **PAGE**

| APPENDIX A: DOE RUN A                             | 82  |

|---------------------------------------------------|-----|

| APPENDIX B: DOE RUN B                             | 84  |

| APPENDIX C: DOE RUN C                             | 86  |

| APPENDIX D: DOE RUN D                             | 88  |

| APPENDIX E: DOE RUN E                             | 90  |

| APPENDIX F: DOE RUN G                             | 92  |

| APPENDIX G: DOE RUN H                             | 94  |

| APPENDIX H: DOE RUN J                             | 96  |

| APPENDIX I: DOE RUN K                             | 98  |

| APPENDIX J: DOE RUN FOR FINAL SETTING             | 100 |

| APPENDIX K: Raw Data before Placing PVC Chip      | 104 |

| APPENDIX L: Final Setting Raw Data - REMOVAL (um) | 105 |

| - TTV                                             | 106 |

| - Brightness                                      | 107 |

# **CHAPTER 1**

# **INTRODUCTION**

### 1.1 BACKGROUND

In silicon wafer manufacturing, the wafer goes through many processes before it goes to the etching process (Seth P. Bates, 2000), as depicted by the following :

[ INGOT ] → Slicing → Grinding Edge profile → Lapping → Etching →

Annealing → Sandblasting → Polishing → Complete Wafer (PW)

Before it becomes a polished wafer, so called PW wafer, the processes from slicing to sandblasting produce wafers that are referred to as CW wafers. It is crucial to sustain wafer flatness starting from the CW stage before the wafer is eventually polished.

This project will focus on the etching stage of wafer manufacturing. Overall etching process is employed to reduce the wafer thickness to an acceptable value, as well as to produce an acceptable level of brightness on both surfaces. Finally, the wafer will be subsequently polished on one surface.

The etching process done here is an isotropic etching type, in which etching happens in all directions (Shimura, Fumio 1989). Wafers are loaded inside a basket, which one basket containing 23 pieces of wafer. The etching arrangement employs one etching drum that can accommodate up to four baskets, with one basket fitting into one compartment. Thus, one etching drum contains of four compartments. This means that at any time, 92 pieces of wafer can be etched (23 pieces x 4).

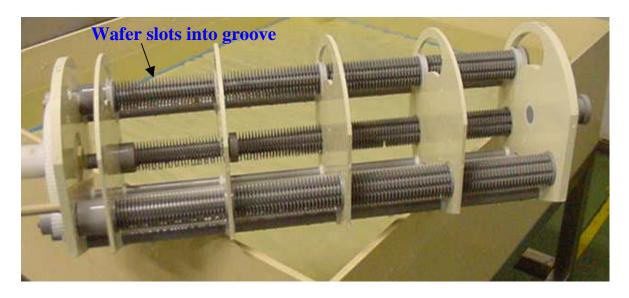

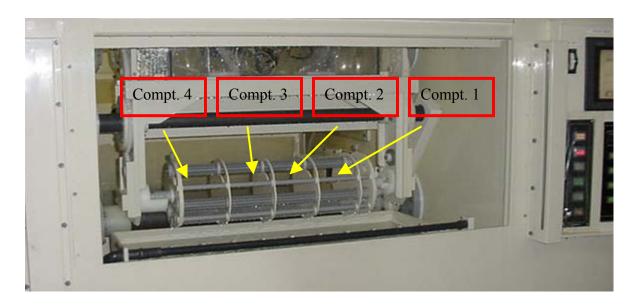

Shown below are pictures of an etching drum with four compartments and an etching drum being loaded into the etching machine:

Figure 1.1: Existing etching drum

Figure 1.2: Drum being load into the etching machine

### 1.2 PROBLEM DESCRIPTION

In the etching stage, the most important characteristic which affects wafer polishing is wafer thickness. Apart from the dimensions and qualities of an individual wafer, equally critical is the variation of such characteristics between wafers within a compartment as well as those between compartments in the whole etching drum. The whole ingot lot will be processed concurrently. Every piece in one ingot will go through the same particular condition set by machine according to its characteristic. When there are big variations, for example variations in thickness removed during etching, some of the wafers will be out of specifications. When a wafer is out of specification, there can be two possibilities:

#### a) Recovery:

The out of specification wafer will be sent to respective area that can eliminate the defect, and the wafer will be processed for the second time until it is in specification (within its tolerance). The disadvantages of recovery are it involves a waste in chemicals needed, power, water consumption, and production time (less output).

### b) Reject:

This is the last resort, and will be done when wafer cannot be salvaged anymore.

Thus, it is important to improve a process, whereby small improvement will potentially bring large saving to manufacturing.

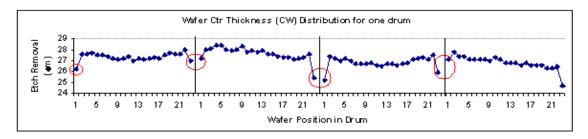

Currently, variations in wafer thickness removed during etching are observed within a compartment especially with wafers positioned at the two ends of each of the four compartments. Figure 1.3 below depicts a typical profile of etching thickness removed (labeled as etch removal) for a batch of wafers in one etching drum. There are four compartments in one drum. The reduced etch thickness removed from eight wafers on each side of the four drum compartments are indicated by the eight low spikes.

Figure 1.3: Low spike at beginning and end of each compartment

NB: Etching removal = wafer thickness before etching (lapped thickness) MINUS wafer thickness after etching

It is apparent that wafers positioned at each side of a compartment have lower removal than wafers located in the middle part of the compartment. Additionally, variations are also suspected between compartments. In other words, etching rate is not uniform between compartments. It is suspected that the middle compartments (that is compartment no. 2 & 3) provide better removal. However, this needs to be studied further. The main challenge here is how to maintain uniform removal among wafers in a compartment and between drum compartments.

It is thought that the above variations are due to various etching and etchant parameters, such as uniformity of etchant flow rate (referred to as bubbling flowrate), variation in acid temperature, silicon content in the etchant, etching drum groove dimension, existence of gaps between compartments in the etching drum and so on (Kuo Shen Chen et al, 2002, D.J. Blackwood et al 2003).

Apart from wafer thickness, the brightness of etched surface is also an important parameter. The brightness needs to be maintained at certain acceptable level. There are two types of brightness level specification after the etching process, namely:

- a) 20% to 60% for 30 µm etching removal

- b) 20% to 80% for 40 μm etching removal

It is normal for the etching process to give rise to another problem in which wafer become excessively bright. When wafer brightness exceeds the specified level, the will be more shiny than normal. Shine wafers will be more sensitive and are prone to have stains. This phenomenon will affect yield and contribute to higher rejects.

In order to fully address this challenge, many aspects need to be investigated. As stated earlier, the current study focuses on the etching stage and within the etching stage, this project looks at mainly the issue of drum design. If an improved drum design can be developed, it can be made as a basis for further and more comprehensive investigation.

Once the new drum has been designed, this project will be looking further on etching parameters evaluations. Etching machine parameters will be varied using Design of Experiment (DOE) method to obtain optimum condition setting.

### 1.3 OBJECTIVE

- 1. To study the etching performance of silicon wafers when using drum design with reduced gaps between compartments

- 2. To study etching performance of silicon wafers by varying etching parameters to obtain optimum condition

### 1.4 SCOPE

- 1. Two etching drum designs will be developed, ordered and tested, and compared against current designs.

- 2. Output parameters to be monitored during etching are thickness variation, surface brightness and surface finish.

- 3. Investigations will be conducted at different condition of etching input parameters, namely etchant temperature, bubbling flow rate and speed of wafer rotation.

- 4. The currently used proprietary etchant formulation will be employed

### **Additional Notes:**

As mentioned earlier, this project hopes to produce a better removal distribution during wafer etching process. Flatness monitoring is not included in the scope of the current project. However, if flatness measurement can be obtained, it could help to reduce whether a smaller deviation in etching removal is also coincident with better flatness.

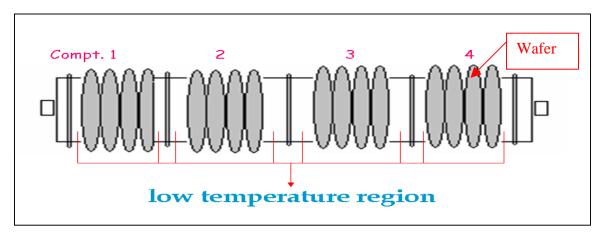

It is possible that variations are due to non-uniform etchant flow rate. In etching compartment, there are 29 slots per compartment. 23 wafers will be positioned in each compartment, using slot numbers 3 to 26. Slot numbers 1, 2, 27, 28, and 29 will be left empty. It is suggested that this gap means that a cooler region may exist next to the nearest wafers resulting in lower removal of these wafers (refer to Figure 1.4):

Figure 1.4: Low Temperature Region

#### REFERENCES

- A. Gordijn, J.K.Rath, R.E.I Schropp 2004. "Microcrystalline Silicon Growth in the presence of dopants: effect on high growth temperatures" <u>Journal of Non-crystalline Solids</u> 338 340:110 114

- Dana Cristea et al. 2002 "Experiments for Microphotonic Components Fabrication using Si <111> Etching Techniques" Sensors and Actuators 99, pg 92 97

- D.J.Blackwood, Y.Zhang 2003. "The Effect of Etching Temperature on the Photoluminiscenes Emitted from, and the Morphology of P-type porous silicon" <u>Journal of Electrochemical</u> 48: 623 630

- E.Chambon, E. Florentin et al.2005. "Optical Properties of Porous Silicon Surface."

<u>Microelectronics Journal</u> 36: 514 517

- E. Vazsonyi, E. Szilagyi, P.Petrik, Z.E.Horvath, T.Lohner, M.Fried, G. Jalsovzky

2001. "Porous Silicon Formation by Stain Etching" <u>Thin Solid Film</u> 388: 295

302

- J. Watanabe, G.Yu, et al.2005. "High Precision Chemical Mechanical Polishing of Highly Boron-doped Silicon Wafer used for Epitaxial Substrate" <u>Precision</u> <u>Engineering</u> 29: 151 – 156

- Kalpakjian, R.Schmid 2001. <u>Manufacturing Engineering and Technology.</u> 4<sup>th</sup> ed. Prentice Hall International. New Jersey

- Kuide Qin, Yongcheng Li 2003. "Mechanisms of Particle Removal from Silicon Wafer Surface in Wet Chemical Cleaning Process." <u>Journal of Colloid and Interface Science</u> 261: 569 574

- Kuo Shen Chen, Xin Zhang, Arturo A. Ayon, S.Mark Spearing 2002. "Effect of Process Parameters on the Surface Morphology and Mechanical Performance of Silicon Structures after Deep Reactive Ion Etching (DRIE)." <u>Journal of</u> <u>Microelectromechanical Systems</u>, Vol. 11, No. 3

- Lunsford, Connors 1992. The St. Martin's Handbook. St. Martin's Press, New York.

- Lun Biao Xu 1998. "The Formation of an Inhomogeneous Distribution of Oxygen in CZ-Silicon Crystal: An Investigation with Quantum Reaction-Diffusion Equation" <u>Journal of Crystal Growth</u> 193: 541 551

- M.Barranco Diaz, W.Koch et al. "Resistivity Topography: A Grain Boundary Characterization Method" <u>Solar Energy Materials and Solar Cells</u> 72 (2002): 473 486

- M. Safi, J.N Chazalviel, M. Cerkaoui, A. Belaidi, O. Gorochov 2002. "Etching of n-type silicon in (HF + oxidant) solutions: in situ characterization of surface chemistry." Journal of Electrochemical 47: 2573 2581

- M. Vergnat, N. Hadj Zoubir, A.Burneau 1995. "Homogeneous Chemical Etching of Sandblasted Silicon Substrates" <u>Thin Solid Films</u> 255: 231 233

- Mei Sun, Kevin Gabriel, "Direct Wafer Temperature Measurement for Etch Chamber Diagnostics and Process Control". USA

- N.Gabouze 2002. "A New Preferential Etch of Silicon (111) with Ammonia System" Surface Science 507 -510: 429 -433

- P.K.Singh, R.Kumar, M.Lal, S.N.Singh, B.K.Das 2001. "Effectiveness of Anisotropic Etching of Silicon in Alkaline solutions" Solar Energy Materials and Solar Cells 70: 103 113

- S.Beyer, S.Lohr, Ch.Heyn, D. Heitmann, W. Hansen 2002. "Etching Temperature Dependant Mobilities up to 190 cm<sup>2</sup>/Vs at Chlorine Etched and Regrown Interfaces." Journal of Physics 653 656

- Seth P. Bates 2000. "Silicon Wafer Processing." Applied Materials, Summer

- Sharath Chandrasekaran, Sriram Sundararajan 2004. "Effect of Micofabrication Processes on Surface Roughness Parameters of Silicon Surfaces" <u>Surface and</u>

Coating Technology 188 189: 581 587

- Shimura, Fumio 1989. <u>Semiconductor Silicon Crystal Technology</u>. Academic Press, Inc. San Diego, California.

- T.H.Wetzel, J.Virbulis 2003. "Modelling in Industrial Silicon Wafer Manufacturing From Crystal Growth to Device Processes" <u>International Scientific</u>

<u>Colloquium</u>, Modeling for Electromagnetic Processing, Hannover March 24 26.

- Wataru Natsu, Yukihiro Ito et al. 2005 "Effects of Support Method and Mechanical

- Property of 300 mm Silicon Wafer on Sori Measurement" <u>Precision</u>

<u>Engineering</u> 29 : 19 -26

- X.P.Li, T.He, M.Rahman 2005. "Tool Wear Characteristics and Their Effects on Nanoscale Ductile Mode Cutting of Silicon Wafer" Wear 259: 1207 1214

Yanbing Zu, Lie Xie et al. 1998. "Studies on Silicon Etching using the Confined Etchant Layer Technique" Journal of Electrochimical vol 43: 1683 1690