# Time and Frequency Characterization of the High Speed I/O Data Bus

### JIMMY HUANG HUAT SINCE

UNIVERSITI TEKNOLOGI MALAYSIA

# Specially dedicate to...

God the glory and the highest My beloved parents And My dearest brother and sisters

### ACKNOWLEDGEMENT

Firstly, I would like to thank God for giving me strength and wisdom in completing the work, my family in encouraging me to take this course.

I would like to take this oppurnity to express my appreciation to my supervisor, Prof Madya Dr Ahmad Zuri for his guidance and fully support to complete the thesis.

Never forget to thank Yew Teong Guan and Ahmad Jalaluddin Bin Yusof from Intel Corporation, for his guidance, support and information suppled for my thesis.

Last but not the least, thanks to my friends who help me not matter in encouragement, support, advice, discussion or commend especially Lai Yit Pin and Seah Yeow Ngee for student affair coordination.

### ABSTRACT

High speed data transfer between the CPU and peripherals on the PC motherboard is needed to support data traffic in future generation applications such as multimedia, games and broadband networks. The High Speed I/O data bus is developed to meet these applications. At high speed with multi Gbits/sec, impedance mismatch between the CPU and peripherals becomes critical and limits the possible maximum throughput. This effect can be modeled as a convolution process where the I/O bus behaves as a linear time invariant system that is defined by a channel impulse and frequency response. Since there are variations in the characteristic of the motherboards due to the fabrication and assembly process, it is desired to estimate the impulse response and frequency response of the High Speed I/O bus. This information can be used to gage the capability of the motherboard and use it as feedback to the relevant fabrication and assembly processes. By using simulation on MATLAB and EDA tools, two candidate methods will be evaluated: Impulse response and correlation method using simulated channel characteristics. Robustness of both methods will be evaluated in the presence of noise and cross talk. Further evaluation will be performed on data collected from actual production test of the I/O Bus. This is to evaluate the capability of the evaluated methods under actual manufacturing environment.

### ABSTRAK

Data Bas Kelajuan Tinggi antara CPU dan periferal atas Papan Utama Komputer diperlukan untuk penghantaran data trafik untuk kegunaan seperti multimedia, kehiburan and kemudahan internet. I/O berkelajuan tinggi diperlukan untuk memenuhi permintaan tersebut. Dengan kelajuan tinggi sehingga berjuta-juta perhantaran dalam satu saat, Keselarasan rintangan electrik antara CPU dan periferal menjadi kritikal dan boleh menghadkan penghantaran data maksimum. Kesan ini boleh diterangkan sebagai proses pendaraban di mana data bas sebagai sistem tak ubah dengan masa dan ciri-cirinya boleh dinyatakan tindak balas delta atau tindak balas frekuensi. Oleh disebabkan wujudnya pengubah semasa process perkilangan, pempaparan ciri-ciri dalam tindak balas delta dan frekuensi amat diperlukan. Dengan penggunaan MATLAB dan EDA, dua cara dikajikan, antaranya adalan tindak balas delta dan tindak balas perkaitkan. Keubahsuaian kedua-dua cara dalam kebisingan sekeliling dikajikan. Pengkajian seterusnya juga tertumpu kepada proses perkilangan supaya cara ini boleh digunakan untuk penghasilan buatan banyak.

### **CONTENTS**

| CHAPTER | TITLE                              | PAGE |

|---------|------------------------------------|------|

|         | TITLE                              | i    |

|         | VALIDATION OF E-THESIS PREPARATION | ii   |

|         | DECLARATION                        | iii  |

|         | DEDICATION                         | iv   |

|         | ACKNOWLEDGEMENT                    | v    |

|         | ABSTRACT                           | vi   |

|         | ABSTRAK                            | vii  |

|         | CONTENT                            | viii |

## CHAPTER 1 INTRODUCTION

| 1.1 | Background                                |   |

|-----|-------------------------------------------|---|

|     | 1.1.1 High Speed I/O Challenge            | 2 |

|     | 1.1.2 Communication Blocks of Bus Channel | 3 |

| 1.2 | Objective                                 | 5 |

| 1.3 | Scope                                     | 5 |

| 1.4 | Problem Statement                         | 6 |

## CHAPTER II LITERATURE REVIEW

| 2.1 | Signal Integrity Enigneering Overview        | 7  |

|-----|----------------------------------------------|----|

| 2.2 | Time Domain Analysis                         | 8  |

| 2.3 | Scattering Parameters                        | 10 |

| 2.4 | Dynamic Modeling Using Transient Response    | 13 |

| 2.5 | Dynamic System Modeling using Optimum Filter | 13 |

| 2.6 | Non Linear Modeling Using Neural Network     | 14 |

|     |                                              |    |

### CHAPTER III THEORY

| 3.1 | Transmision Line Interconnect                    | 16 |

|-----|--------------------------------------------------|----|

| 3.2 | Impulse Response Characteristic                  | 17 |

| 3.3 | Correlation Characterization                     | 18 |

| 3.4 | Crosstalk, Power Noise and Jitter Noise          | 23 |

| 3.5 | Electrical Modeling of Platform Bus Interconnect | 25 |

### CHAPTER IV METHODOLOGY

| 4.1 | Transmission Bus Channel Characterization           |          |  |

|-----|-----------------------------------------------------|----------|--|

|     | 4.1.1 Device Modeling and Circuit Setup             | 29       |  |

|     | 4.1.2 Comparison of Scaterring parameter, Impulse F | Response |  |

|     | and Correlation Method                              | 31       |  |

| 4.2 | Immunity to the Noise                               | 31       |  |

| 4.3 | Measurement in the Lab                              | 32       |  |

### CHAPTER V RESULT

| 5.1 Noise Free Er |                                                                                        | Free Environment                              | 35  |

|-------------------|----------------------------------------------------------------------------------------|-----------------------------------------------|-----|

|                   | 5.1.1                                                                                  | Proof of Concept                              | 35  |

|                   | 5.1.2                                                                                  | Determination of Correlation Parameters       | 38  |

|                   | 5.1.3                                                                                  | Windowing Technique                           | 40  |

|                   | 5.1.4                                                                                  | Simulation Using Simple Transmission Line     | 45  |

|                   | 5.1.5                                                                                  | Simulation Using Full EM Modeling Platform Da | ita |

|                   |                                                                                        | Bus Topology                                  | 47  |

| 5.2               | Immunity over Random Noise, Periodic Noise and Jitter<br>CONCLUSION AND RECOMMENDATION |                                               | 49  |

| CHAPTER VI        |                                                                                        |                                               | 51  |

|                   | REFE                                                                                   | RENCES                                        | 53  |

APPENDIX

55

Х

### **CHAPTER I**

### **INTRODUCTION**

#### 1. Introduction

High speed data transfer between the CPU and peripherals on the PC motherboard is needed to support data traffic in future generation applications such as multimedia, games and broadband networks. The high speed I/O differential bus is developed to meet these applications. At higher speed with multi Gbits/sec, impedance mismatch between the CPU and peripherals becomes critical and limits the possible maximum throughput. This effect can be modeled as a convolution process where the I/O high speed behaves as a linear time invariant system that is defined by a channel impulse and frequency response. Since there are variations in the characteristic of the motherboards due to the fabrication and assembly process, it is desired to estimate the impulse response and frequency response of the bus. This information can be used to gage the capability of the motherboard and use it as feedback to the relevant fabrication and assembly processes. By using simulation on MATLAB and EDA tools, two candidate methods will be evaluated: PDA and correlation method using simulated channel characteristics. Robustness of both methods will be evaluated in the presence of noise and cross talk. Further evaluation will be performed on data collected from actual production test of the high speed I/O bus. This is to evaluate the capability of the evaluated methods under actual manufacturing environment.

### 1.1. Background

#### 1.1.1. High Speed I/O challenge

Computer system organization has three main components, the CPU, the memory subsystem and the I/O subsystem. Bus is a terminology used to describe the interconnecting between the components in the architecture organization. Physically, a bus is a set of wire to send the information from one component to another; the source output the components onto the bus. The destination component then inputs this data from the bus. Due to the increasing complexity of computer architecture, the bus system is much more efficient in less power consumption; less space and fewer pin than direct connect from component to component<sup>1</sup>.

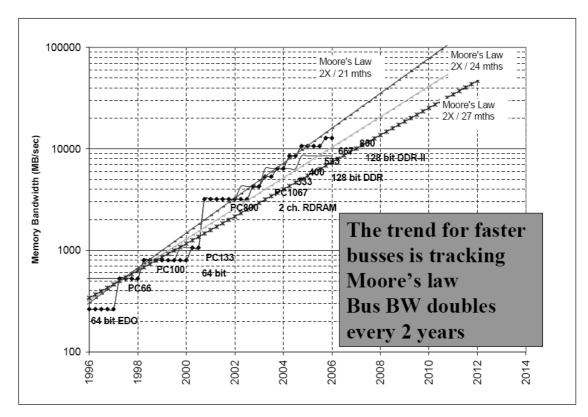

Moore's Law drives transistor scaling by 2x for every 21 months. Advanced computer system benefits from the transistor scaling allowing more processing capabilities can be achieved and higher data bandwidth is needed to support the increasing processing power (refer to Figure 1)<sup>2</sup>. The performance degrades if the computer spends most of its time waiting for the data. The needs of data bandwidth is even critical with the introduction of parallel processing, distribution computing system, multi core CPU and more efficient pipeline architecture while keep cache size smaller size or slower growing rate.

<sup>&</sup>lt;sup>1</sup> John D. Carpinelli, "Computer System Organization and Architecture", Chapter 4, page 141, Addison Wesley, 2001

<sup>&</sup>lt;sup>2</sup> Maynard Falconer, "Bus Design Boot Camp", Chapter 1, Intel Corp, 2005

Figure 1: Relationship of Moore's Law and Bus Bandwidth (Courtesy of Intel® Corp)

### 1.1.2. Communication Block of Transmission Bus Channel

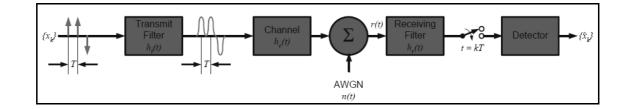

From communication view of point, the transmission bus channel is composed of transmitter block, bus channel block and receiver channel block as illustrated in Figure2. The source output is x(t), channel impulse response is h(t) and the receiver output is r(t) where n(t) is Additive White Gaussian noise. The receiver output is the convolution of h(t) and x(t) plus summation of  $n(t)^3$ .

$$r(t) = x(t) \otimes h(t) + n(t)$$

<sup>3</sup> Maynard Falconer, "Bus Design Boot Camp", Chapter 8, Intel Corp, 2005

Figure 2: Transmission line can be modeled into communication blocksets

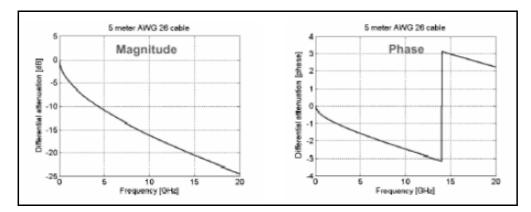

The transmission bus channel is behaves a low pass filter where the channel loss increase with the frequency. It is due to skin effect loss and dielectric loss. Instead of amplitude loss, the channel also suffers from phase distortion as Figure 3. Phase distortion is due to the channel length, dielectric length change, inductance change over the frequency. As the result, the receiver has closed Eye Diagram<sup>4</sup>.

Figure 3: Frequency response of transmission line behaves like a low pass filter

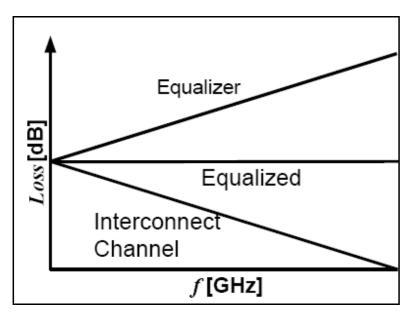

Equalizer is implemented to improve the signal quality by introducing the inverse characteristic of the transmission bus channel so that both equalizer and channel can cancel each other to retrieve the original transmitting data as Figure 4. The equalizer,  $C(f) = H^{-1}(f)$ , can be placed at the transmitter, receiver or both. The equalizer can be an analog passive high pass filter or discrete FIR filter. Some popular discrete FIR filter used are pre-emphasis (used in transmitter), Discrete Linear Equalizer (DLE) and Decision Feedback Equalizer (used at receiver) or advance adaptive equalizer. No matter which equalizer is used, the H(f) must be characterized.

<sup>&</sup>lt;sup>4</sup> Eye Diagram is electrical specification for transmitting or receiving signals. Signal is considered fail to the specification when it breaks the boundary of the Eye Diagram, where the Eye Diagram looks close.

Figure 4: Implementation of equalizer aims to resolve the lossy transmission line

### 1.2. Objective

The research aims to evaluate the performance and parameters of the proposed correlation method in transmission bus channel characterization. The evaluation includes comparison with pulse response method and Scattering parameter measurement on robustness, algorithm complexity, effectiveness, accuracy and immunity to the environment noise. An equalizer based on the correlation algorithm is build to evaluate the performance in the transmission bus channel system.

### **1.3. Scope**

The analysis is done using SPICE and MATLAB focusing on behavior level simulation excluding any RTL level simulation. The study is based on offline simulation and the measurement can only be done depending on the hardware readiness. The study focuses on electrical parameters and assumes the transmission bus channel is a time invariant system.

#### **1.4. Problem Statement**

High speed I/O bus design is always hungered due to its significant impact to the system performance. The challenge consists of large number of process variable, effecting high volume manufacturing, complex computer organization and cost impact. Parallel source synchronous bus which it used to be dominant Bus interconnect, cannot simply increase its bandwidth by scaling the number of bus size and bus speed due to the ISI (Inter Symbol Interfering) effect, increasing pin count, more variables, larger space and more tighten timing requirement. Therefore these buses such as PCI migrate to PCIe, a serial differential bus for the following advantages: noise immunity, fewer pin counts, less routing space and cost effective. Due to the limited bandwidth of transmission media, high data rates on printed circuit boards and communication networks impose significant signal integrity degradation, equalization techniques must be included in the transmitter and receiver circuitry to compensate for the lossy characteristics of the transmission channel<sup>5</sup>. Conventional method such as Scattering Parameters measurement cannot characterize the bus in active operation condition thus an active bus channel characterization is proposed to resolve the problem

<sup>&</sup>lt;sup>5</sup> M. Cases, D. N. de Araujo, E. Matoglu, "Electrical Design and Specification Challenges for High Speed Serial Links", 2005 Electronics Packaging Technology Conference