## STREAM PROCESSOR ARCHITECTURE - STREAMING MEMORY SYSTEM

NGO WAI LOON

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical - Computer & Microelectronic System)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > JUNE 2015

Specially to my beloved father and mother Brothers and all my friends for their inspiration, support and encouragement throughout my adventure of educations

### ACKNOWLEDGEMENT

To accomplish whatever I have done in my master project, there were many people along the way who have been responsible for guiding me, advising me and encouraging me.

I am deeply grateful and would like to take this opportunity to express my heartfelt appreciation to my supervisor, Prof. Dr. Mohamed Khalil bin Mohd Hani. I am deeply indebted and thankful to my supervisor for supporting me from the starting. I consider myself to be a fortunate person being guided by him on all the knowledge and skills required to accomplish my final year project.

In addition, I would like to take this opportunity to thank Intel Malaysia to support me in financially in pursuing this master degree. At the outset I would like to thank my family especially my parents and my girlfriend, Wong Siew Kuen who have given me support throughout my study. It would be hard without their moral support and understanding for me to finish this project. Nevertheless, my great appreciation is dedicated to Faculty of Electrical Engineering, UTM for the support and encouragement throughout the project. Besides, I would like to express my appreciation to individuals who were involved directly or indirectly with this project.

#### ABSTRACT

Streaming memory system in this project is defined as a process of an stream processor that need to be able to stream whole chunk of data from/to external memory with real time performance. Real-time implementation of Convolution Neural Network (CNN) application are taking large amount of CPU cycle to fetch and write data from/to external memory are popular issues in the field of media processing. So, a new FPGA-based streaming memory system was designed in order to allow the media processing application to execute multiple streaming operators. It would be a challenging task as computational capability would be increased. The hierarchy of streaming memory system consists of a memory system, stream register file (SRF) and arithmetic units. The memory system and SRF are the key part of the functional architecture of this project. This hierarchy can be used to exploit the parallelism and locality of streaming media applications. The main idea of three storage hierarchy is to allow the ALUs to operate efficiently in parallel. It is impractical to provide data on every cycle to ALU clusters using off-chip DRAM because peak bandwidth of memory system could not effectively support ALU clusters to achieve the computation rate. Moreover, the reason of creating streaming memory system is to fulfill the computational capability in media application that consists of multiple arithmetic operator. Two study case was tested which is RGB to YUV Cluster and 2D convolution cluster, and it was successfully to read or write a particular chunk of data in real time.

#### ABSTRAK

Sistem memori streaming dalam project ini adalah ditakrifkan sebagai proses di mana satu pemproses aliran yang dapat strim keseluruhan data dari/ke memori luaran dengan prestasi masa nyata. Implementasi masa nyata untuk aplikasi Konvolusi Rangkaian Neural (CNN) memerlukan jumlah kitaran CPU yang besar untuk mendapat dan menulis data dari/ke memori luaran merupakan isu yang popular dalam bidang pemprosesan media. Oleh itu, sistem memori streaming berdasar FPGA yang baru telah direka supaya membolehkan aplikasi pemprosesan imej untuk melaksanakan pelbagai pengendali streaming. Ia merupakan satu cabaran kerana keupayaan komputasi akan dipertingkatan. Hierarki sistem memori streaming terdiri daripada sistem memori, fail daftar aliran (SRF) dan unit aritmetik. Sistem memori dan SRF merupakan bahagian penting dalam arkitek fungsi projek ini. Hierarki tersebut boleh digunakan untuk mengekspoitasi keselarian dan aplikasi media streaming tempatan. Idea utama dalam tiga penyimpanan hierarki adalah untuk membolehkan ALUs beroperasi dengan cekap secara selari. Ia adalah tidak praktikal untuk membekalkan data pada setiap kitaran kepada kelompok ALU dengan menggunakan luar-pemproses DRAM kerana puncak lebar jalur sistem memori tidak dapat menyokong kelompok ALU dengan cekap untuk mencapai kadar komputasi. Bukan itu sahaja, faktor untuk mewujudkan sistem memori streaming adalah untuk memenuhi keupayaan komputasi dalan aplikasi media yang terdiri daripada pelbagai pengendali aritmetik. Dua kes kajian telad diuji di mana RGB ke kelompok YUV dan 2D kelompok konvolusi, dan ia berjaya membaca atau menulis sebahagian data tertentu dalam masa nyata.

# TABLE OF CONTENTS

| CHAPTER | TITLE                             | PAGE |

|---------|-----------------------------------|------|

|         | DECLARATION                       | ii   |

|         | DEDICATION                        | iii  |

|         | ACKNOWLEDGEMENTS                  | iv   |

|         | ABSTRACT                          | V    |

|         | ABSTRAK                           | vi   |

|         | TABLE OF CONTENTS                 | vii  |

|         | LIST OF TABLES                    | Х    |

|         | LIST OF FIGURES                   | xi   |

|         | LIST OF ABBREVIATIONS             | xiii |

|         | LIST OF APPENDICES                | xiv  |

| 1       | INTRODUCTION                      |      |

|         | 1.1 Background of study           | 1    |

|         | 1.2 Problem Statement             | 3    |

|         | 1.3 Objective                     | 4    |

|         | 1.4 Scope                         | 4    |

|         | 1.5 Project Achievement           | 5    |

| 2       | LITERATURE REVIEW                 |      |

|         | 2.1 Stream Processor Architecture | 6    |

|         | 2.2 Stream Register File          | 7    |

|         | 2.3 Streaming Memory System       | 9    |

|         | 2.4 Bandwidth Hierarchy           | 10   |

|         | 2.5 Instruction Set Architecture  | 11   |

|     | 2.5.1  | Stream-level ISA          | 11 |

|-----|--------|---------------------------|----|

|     | 2.4.2  | Stream Command ISA        | 12 |

| 2.6 | Stream | Register File and         | 15 |

|     | Stream | Controller Data Flow      |    |

| 2.7 | Data S | tream on RGB_2_YUV Kernel | 17 |

|     |        |                           |    |

| ME  | THOD   | OLOGY                     |    |

| 3.1 | Projec | t Methodology             | 19 |

| 3.2 | Design | n Methodology             | 21 |

3

| 3.2 | Design | n Methodol  | ogy                        | 21 |

|-----|--------|-------------|----------------------------|----|

| 3.3 | Desig  | n Tools     |                            | 21 |

| 3.4 | Stream | ning Memo   | ry System                  | 23 |

|     | 3.4.1  | Overview    |                            | 23 |

|     | 3.4.2  | Top-Leve    | l Design                   |    |

|     | 3.4.3  | Stream-Le   | evel Instruction Set (ISA) |    |

|     | 3.4.4  | Stream-Le   | evel ASM-Chart             | 25 |

|     | 3.4.5  | RTL Desi    | gn                         | 26 |

|     | 3.4.6  | Module D    | Design                     | 30 |

|     |        | 3.4.6.1     | Data Memory (SDRAM)        | 30 |

|     |        | 3.4.6.2     | Program Counter System     | 31 |

|     |        | 3.4.6.3     | Stream Register File (SRF) | 31 |

|     |        | 3.4.6.4     | Stream Controller          | 32 |

|     |        | 3.4.6.5     | Kernel ISA                 | 33 |

|     |        | 3.4.6.6     | Microcontroller            | 35 |

| 3.5 | Case S | Study 1: RC | B to YUV ALU Cluster       | 37 |

|     | 3.5.1  | Algorithm   | 1                          | 38 |

|     | 3.5.2  | Specificat  | ion                        | 38 |

|     | 3.5.3  | ASM Cha     | rt                         | 39 |

|     | 3.5.4  | RTL Desi    | gn                         | 40 |

|     | 3.5.5  | Top-Leve    | l Design                   | 42 |

|     | 3.5.6  | Datapath    | Unit (DU)                  | 43 |

|     | 3.5.7  | Control U   | Init (CU)                  | 46 |

|     | 3.5.8  | RGB to Y    | UV Kernel                  | 49 |

| 3.6 | Case S | Study 2: 2D | Convolution Cluster        | 51 |

|     |        |             |                            |    |

|     | 3.6.1  | Algorithm                        | 51 |

|-----|--------|----------------------------------|----|

|     | 3.6.2  | Data Flow Graph                  | 52 |

|     | 3.6.3  | ASM Chart                        | 53 |

|     | 3.6.4  | RTL Design                       | 54 |

|     | 3.6.5  | Top-Level Design                 | 56 |

|     | 3.6.6  | Datapath Unit (DU)               | 57 |

|     | 3.6.7  | Control Unit (CU)                | 58 |

|     | 3.6.8  | Convolution Kernel               | 61 |

| 3.7 | Integr | ation of Streaming Memory System | 62 |

|     | and R  | GB to YUV Cluster                |    |

| 3.8 | Integr | ation of Streaming Memory System | 63 |

|     | and 2  | D Convolution Cluster            |    |

| 3.9 | Timel  | ine of Instruction Execution     | 64 |

|     |        |                                  |    |

| RES | SULTS  | AND DISCUSSIONS                  |    |

| 4.1 | Stream | ning Memory System Result        | 66 |

|     | 4.1.1  | Load Memory                      | 66 |

|     | 4.1.2  | Load SRF                         | 68 |

|     | 4.1.3  | Store SRF                        | 69 |

|     | 4.1.4  | Store Memory                     | 71 |

| 4.2 | Conve  | ersion of RGB to YUV Result      | 72 |

|     | 4.2.1  | Matlab Simulation Result         | 73 |

|     | 4.2.2  | Quartus Simulation Result        | 75 |

| 4.3 | 2D Co  | onvolution Result                | 80 |

|     | 4.3.1  | Matlab Simulation Result         | 81 |

|     | 4.3.2  | Quartus Simulation Result        | 82 |

|     |        |                                  |    |

| CO  | NCLUS  | SION                             |    |

| 5.1 | Concl  | usion                            | 90 |

| 5.1 | Conclusion  | 90 |

|-----|-------------|----|

| 5.2 | Future Work | 91 |

| REFERENCES       | 92       |

|------------------|----------|

| Appendices A - E | 94 - 131 |

# LIST OF TABLES

| FIGURE NO. | TITLE                                       | PAGE |

|------------|---------------------------------------------|------|

| 2.1        | Peak bandwidth                              | 11   |

| 2.2        | Imagine stream-level instruction set        | 12   |

| 2.3        | Stream Command                              | 14   |

| 3.1        | Comparison between Different HDL Simulators | 22   |

| 3.2        | Stream-Level ISA                            | 26   |

| 3.3        | Control Vector of Kernel ISA                | 34   |

| 3.4        | Control Vector                              | 36   |

| 3.5        | Control signal Table                        | 37   |

| 3.6        | Control Signal Table                        | 47   |

| 3.7        | Control Vector                              | 48   |

| 3.8        | Control Vector of RGB to YUV kernel         | 49   |

| 3.9        | Control Signal Table                        | 60   |

| 3.10       | Control Vector                              | 61   |

| 3.11       | Control Vector of Convolution kernel        | 61   |

| 4.1        | Load Memory Instruction                     | 67   |

| 4.2        | Load SRF Instruction                        | 69   |

| 4.3        | Store SRF Instruction                       | 70   |

| 4.4        | Store Memory Instruction                    | 72   |

| 4.5        | Execute Kernel Instruction                  | 78   |

| 4.6        | Quartus Simulation Result of Pixels         | 79   |

| 4.7        | Execute Kernel Instruction                  | 86   |

| 4.8        | Quartus Simulation Result of Convolution    | 87   |

# LIST OF FIGURES

| FIGURE NO. | TITLE                                              | PAGE |

|------------|----------------------------------------------------|------|

| 1.1        | Stream Processor Block Diagram                     | 2    |

| 1.2        | ALU Cluster                                        | 3    |

| 2.1        | Stream Processor Block Diagram                     | 7    |

| 2.2        | SRF Block Diagram                                  | 8    |

| 2.3        | Streaming Memory System                            | 9    |

| 2.4        | Bandwidth Hierarchy                                | 10   |

| 2.5        | DPU architecture                                   | 14   |

| 2.6        | Timeline of stream command execution               | 15   |

| 2.7        | Flow Chart of the SRF                              | 16   |

| 2.8        | Flow Chart of the Stream Controller                | 17   |

| 2.9        | RGB_2_YUV Kernel and Streams                       | 18   |

| 2.10       | Graphical Depiction of Kernel                      | 18   |

| 3.1        | The Project Methodology of Stream Processor Design | 20   |

| 3.2        | Design Methodology                                 | 21   |

| 3.3        | Overview of Streaming Memory System                | 24   |

| 3.4        | Top-Level Design of Streaming Memory System        | 25   |

| 3.5        | ASM-Chart of Streaming Memory System               | 28   |

| 3.6        | SDRAM                                              | 30   |

| 3.7  | Program Counter System                      | 31 |

|------|---------------------------------------------|----|

| 3.8  | SRF                                         | 32 |

| 3.9  | Stream Controller                           | 33 |

| 3.10 | SIMD Instruction Set                        | 33 |

| 3.11 | Kernel ISA module                           | 34 |

| 3.12 | Microcontroller                             | 35 |

| 3.13 | ASM-Chart of RGB to YUV Cluster             | 40 |

| 3.14 | Top Level Module of RGB to YUV Cluster      | 43 |

| 3.15 | RGB to YUV DU Block Diagram                 | 45 |

| 3.16 | RGB to YUV CU Block Diagram                 | 46 |

| 3.17 | RGB to YUV Kernel                           | 50 |

| 3.18 | Data Flow Graph of Convolution Cluster      | 52 |

| 3.19 | ASM-Chart of Convolution Cluster            | 54 |

| 3.20 | Top_Level Module of Convolution Cluster     | 56 |

| 3.21 | Convolution DU Block Diagram                | 58 |

| 3.22 | Convolution CU Block Diagram                | 59 |

| 3.23 | Convolution Kernel                          | 62 |

| 3.24 | Integration of Streaming Memory System      | 63 |

|      | and RGB to YUV Cluster                      |    |

| 3.25 | Integration of Stream Processor             | 64 |

|      | and Convolution Cluster                     |    |

| 3.26 | Timeline of Instruction Execution           | 65 |

| 4.1  | Load Memory Instruction Result              | 67 |

| 4.2  | Load SRF Instruction Result                 | 68 |

| 4.3  | Store SRF Instruction Result                | 70 |

| 4.4  | Store Memory Instruction Result             | 71 |

| 4.5  | RGB Pixels                                  | 73 |

| 4.6  | Matlab Simulation Result of YUV Pixels      | 75 |

| 4.7  | Execute Kernel Instruction                  | 78 |

| 4.8  | 3x3 image and 3x3 Gaussian Filter           | 81 |

| 4.9  | Matlab simulation result of Convolution     | 83 |

| 4.10 | Quartus Simulation Result of Execute Kernel | 85 |

|      | Instruction                                 |    |

# LIST OF ABBREVIATIONS

| ALU   | - | Arithmetic Logical Unit                            |

|-------|---|----------------------------------------------------|

| SRF   | - | Stream Register File                               |

| VLIW  | - | Very Long Instruction Word                         |

| LRF   | - | Local Register File                                |

| SP    | - | Scratch Pad                                        |

| CNN   | - | Convolution Neural Network                         |

| CPU   | - | Central Processing Unit                            |

| FPGA  | - | Field-Programmable Gate Array                      |

| HDL   | - | Hardware Description Language                      |

| RISC  | - | Reduced Instruction Set Computing                  |

| ASIC  | - | Application-Specific Integrated Circuit            |

| DRAM  | - | Dynamic Random-Access Memory                       |

| SDRAM | - | Synchronous Dynamic Random-Access Memory           |

| DPU   | - | Data Path Unit                                     |

| DSP   | - | Digital Signal Processing                          |

| MIPS  | - | Microprocessor without Interlocked Pipeline Stages |

| PE    | - | Processing Element                                 |

| FSM   | - | Finite State Machine                               |

| VCS   | - | Verilog Compiled code Simulator                    |

| ISA   | - | Instrcution Set Architecture                       |

| ASM   | - | Algorithm State Machine                            |

# LIST OF APPENDICES

| APPENDIX | TITLE                                                    | PAGE |

|----------|----------------------------------------------------------|------|

| А        | FYP Gantt Chart 1                                        | 94   |

| В        | FYP Gantt Chart 2                                        | 95   |

| С        | System Verilog Code of Streaming Memory System           | 96   |

|          | and Testbench                                            |      |

| D        | System Verilog Code of RGB to YUV Cluster and            | 109  |

|          | Testbench                                                |      |

| E        | System Verilog Code of Convolution Cluster and Testbench | 124  |

## **CHAPTER 1**

### INTRODUCTION

## 1.1 Background Study

Stream processors are fully programmable processors that exploit the compute intensity, parallelism, and producer-consumer locality in media applications to provide performance efficiencies comparable to special-purpose processors [1]. Stream processors are computing engines that perform calculations on an input stream with high efficiency, while an output stream is produced to be used by other stream processors and ALU clusters. Stream processors can be grouped in close proximity, and in large numbers, to provide immense parallel processing power.

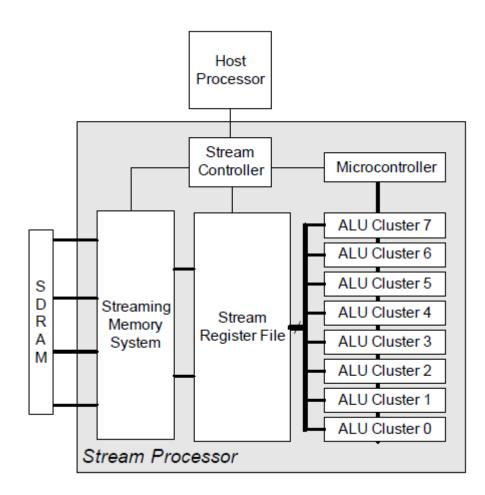

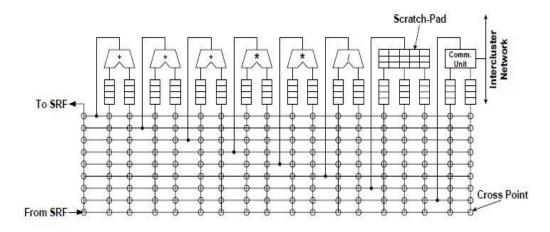

The stream processor architecture effectively exploits the preferable application characteristic exposed by the stream model. The stream processor meets the bandwidth demand and computation of image processing application by directly processing the chunk of naturally arising data streams within the application [2]. Figure 1.1 shows a block diagram of stream processor architecture. The function of stream controller is to sequence the instruction from host the stream processor. The stream register file (SRF), which is a large on-chip storage for streams effectively isolates the ALU clusters from the memory system. The microcontroller is a very long instruction words (VLIW) control engine, issues instruction to arithmetic cluster. As shown in Figure 1.2, each ALU cluster consists of 3 adders, 2 multipliers, 1 divider, 1 scratch pad, 1 communication units. The ALUs are fed by two local register files (LRFs) each, external ports for accessing the SRF. In addition, there is a scratchpad (SP) unit, used for small indexed addressing operations within a cluster, and an intercluster communication (COMM) unit, used to exchange data between clusters.

**Figure 1.1: Stream Processor Block Diagram**

Figure 1.2: ALU Cluster

#### **1.2 Problem Statement**

The motivation behind this project is driven by some reason in the previous performance on stream memory system. Most of the real-time implementation of Convolution Neural Network (CNN) application like face recognition needs a very high speed streaming memory system to fetch and write data from/to external memory. The hardware data-path with multiple arithmetic operators and the execution of multiple streaming operators impose the challenge to increase in computational capability with increase in performance.

Moreover, a conventional load/store CPU or more commonly known as general purpose CPU is also capable of processing media applications, a dedicated stream media processor offer greater performance of throughput versus cost. Other than high CPU cycle, the biggest challenge of processing media with conventional CPU is the frequent memory access and continuous cache miss which makes the cache totally useless in this application.

### 1.3 Objective

There are two main objectives in designing streaming memory system which are:

- 1. To develop a FPGA-based streaming memory system for real-time performance CNN application with large number of ALU.

- 2. To develop a streaming memory system with three-tiered storage bandwidth hierarchy.

- 3. To develop a streaming memory system which has better memory efficiency for media processing compared to a conventional load/store processor.

#### 1.4 Scope

The scope of the project is to focus on FPGA-based streaming memory system which are:

- 1. The project of streaming memory system include memory system, Stream Register File (SRF) and stream controller using System Verilog HDL in a parameterized and configurable design way, that provide flexibility to alter the parameters like bandwidth of the SRF and stream buffer.

- 2. The ALU cluster and microcontroller will not be part of the project. However, two dedicated ALU design which are RGB to YUV conversion and convolution will be used as test case in this project.

- 3. Test-bench will be created to perform functionality check for each configuration.

## 1.5 **Project Achievement**

The design of streaming memory system contribute a few achievement in the project which are:

- The design of streaming memory system is state of the art in stream processor.

This can be a new model in designing of future stream processor.

- 2. The new architecture return in the design is more efficient and configurable compare to a simple RISC processor.

- 3. The project is successfully target to FPGA design although IMAGINE return the design in ASIC. A new design methodology has been return in the project.

#### Reference

- Kapasi, U.J.; Dally, W.J.; Rixner, S.; Owens, J.D.; Khailany, B., "The Imagine Stream Processor," Computer Design: VLSI in Computers and Processors, 2002.

- 2. Scott Rixner, "Stream Processor Architecture", 2002.

- Brucek Khailany, "The VLSI Implementation and Evaluation of Area and Energy-Efficience Streaming Media Processor", June 2003.

- Vutukuru, K.; Dessai, S., "Design and Development of Stream Processor Architecture for GPU Application Using Reconfigurable Computing," International Journal of Reconfigurable and Embedded Systems, 2013.

- Kapasi, U.J.; Dally, W.J.; Rixner, S.; Owens, J.D.; Khailany, B., "The Imagine Stream Processor," Computer Design: VLSI in Computers and Processors, 2002.

- Khailany, B.; Williams, T.; Jim Lin; Peters, L.; Mark, R.; Tovey, W.; Dally, J., "A Programmable 512 GOPS Stream Processor for Signal, Image, and Video Processing", 2009.

- Ujval J. Kapasi; William J. Dally; Scott Rixner; Peter R. Mattson; John D. Owens; Brucek Khailany, "Efficient Conditional Operations for Data-parallel Architectures", In Proceedings International Symposium on Computer Architecture, 2000.

- Kapasi, U. J., Rixner, S., Dally, W. J., Khailany, B., Ahn, J. H., Mattson, P., and Owens, J. D., "Programmable Stream Processors," IEEE Computer, August 2003.

- http://cva.stanford.edu/projects/imagine/, Imagine Stanford, retrieved 8 Oct 2009.

Khailany, B., Dally, W. J., Rixner, S., Kapasi, U. J., Mattson, P., Namkoong, J., Owens, J. D., Towles, B., and Chang, A., "Imagine: Media Processing with Streams," IEEE Micro, March/April 2001.