## DESIGN OF THE STREAMING PROCESSOR ARCHITECTURE FOR MICROKERNEL CONTROLLER AND ALU

NUHAIRI BIN ANUAR

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical – Computer and Microelectronic Systems)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > JUNE 2015

Specially dedicated to my wife, Emmy, my little boy, Umar, and my mother, Azizah.

## ACKNOWLEDGEMENT

I am grateful to Allah for good health and wellbeing that were necessary in completing this project. I would like to give a special thanks to Prof. Dr. Mohamed Khalil bin Haji Mohd Hani for supervising me on this project. His input and directions since the inception greatly helped the outcome of the project. I also like to wish sincere thanks to Dr. Muhammad Nadzir Marsono, Dr. Rabia Bakhteri, and Dr. Usman Ullah Sheikh for the advised and feedback given on the project. I also would like to thank Ngo, Wai Loon for spending quality time with me discussing about the architecture of the Stream Processor. Last, but not least, I would like to thank my wife, Ermi Lihan for the support and understanding during the completion of the project.

## ABSTRACT

Media application such as 3D graphic processing, image processing, video decode and encode requires high rates of arithmetic operation per second. As an outcome of a decade long research, Stream Processor architecture, which is designed to exploit the characteristic of media processing was proposed. A few architectures of stream processor had been proposed and among the popular streaming processor architecture was Imagine Stream Processor. This project is focusing on implementing Imagine-based stream processor architecture on Altera Cyclone IV GX FPGA specifically for ALU Clusters and Microkernel Controller modules. This project report presents the literature reviews of books, theses and papers regarding stream processor architecture and its related use cases. This report also documents the complete project methodology taken in order to design a stream processor on the FPGA where the design of the Stream Processor is using RTL design methodology and System Verilog Language. This report also detailed the architectural design of the stream processor in Chapter 3. Furthermore, result and discussion of the experimental work involve in this project also reported in Chapter 4. The project report concluded that an FPGA-based stream processor is successfully designed and tested with specific image processing use cases. This project report also described possible enhancements possible on the stream processor design.

## ABSTRAK

Aplikasi media seperti pemprosesan grafik tiga dimensi, pemprosesan imej, penyahkodan dan pengkodan video memerlukan kadar operasi aritmetik persaat yang tinggi. Hasil daripada penyelidikan lebih satu dekad, Pemproses Aliran yang direka untuk mengekploitasi ciri-ciri pemprosesan media, telah dicadangkan. Antara beberapa reka bentuk Pemproses Aliran sudah dicadangkan, reka bentuk yang agak dikenali adalah Pemproses Aliran Imagine. Projek ini lebih fokus kepada mencipta Pemproses Aliran berasaskan seni reka Imagine di dalam Altera Cyclone IV GX FPGA terutamanya modul Kluster ALU dan Pengawal Mikrokernel. Laporan projek ini mempersembahkan kajian penulisan tentang buku-buku, tesis-tesis, dan kertas kerja berkenaan seni reka Pemproses Aliran dan pengunaannya. Laporan ini juga melaporkan methodologi penuh yang digunakan untuk mereka satu reka bentuk Pemproses Aliran di dalam satu FPGA, dimana rekaan RTL dan Bahasa System Verilog telah digunakan. Laporan ini juga menjelaskan reka bentuk Pemproses Aliran di dalam Bab ke-3. Juga, hasil dan perbincangan tentang kerja eksperimen yang terlibat dalam project ini dilaporkan dalam Bab ke-4. Laporan project ini membuat kesimpulan bahawa sebuah Pemprosesan Aliran berasaskan FPGA adalah berjaya direka and diuji dengan kes-kes ujian pemprosesan imej yang spesifik. Laporan projek ini juga menerangkan pembaikan yang boleh dilakukan keatas Pemproses Aliran tersebut.

# **TABLE OF CONTENTS**

| UNALIEN | CHA | PTER |

|---------|-----|------|

|---------|-----|------|

2

# TITLE

PAGE

| DECLARATION           | ii  |

|-----------------------|-----|

| DEDICATION            | iii |

| ACKNOWLEDGEMENTS      | iv  |

| ABSTRACT              | V   |

| ABSTRAK               | vi  |

| TABLE OF CONTENTS     | vii |

| LIST OF TABLES        | Х   |

| LIST OF FIGURES       | xi  |

| LIST OF ABBREVIATIONS | xiv |

| LIST OF SYMBOLS       | XV  |

| LIST OF APPENDICES    | xvi |

# 1 INTRODUCTION

| 1.1 | Background and Project Rationale | 1 |

|-----|----------------------------------|---|

| 1.2 | Project Problem Statements       | 2 |

| 1.3 | Project Objective                | 3 |

| 1.4 | Project Scope                    | 4 |

| 1.5 | Project Achievement              | 5 |

## LITERATURE REVIEW

| 2.1 | Related Works                            | 7  |

|-----|------------------------------------------|----|

| 2.2 | Stream Programming and Stream Processing | 9  |

| 2.3 | Imagine Stream Processor Architecture    | 10 |

|     | 2.3.1 Imagine Memory Architecture        | 11 |

|     | 2.3.2 Imagine Arithmetic Cluster     | 14 |

|-----|--------------------------------------|----|

|     | 2.3.2 Imagine Microcontroller        | 16 |

| 2.4 | Imagine Instruction Set Architecture | 17 |

| 2.4 | FPGA-Based Stream Processor          | 21 |

# **PROJECT METHODOLOGY**

3

4

| 3.1 | Introduction |                                      |    |  |

|-----|--------------|--------------------------------------|----|--|

| 3.2 | Litera       | Literature Review                    |    |  |

| 3.3 | Desig        | Design Requirement and Specification |    |  |

| 3.4 | Desig        | n Methodology                        | 28 |  |

| 3.5 | Desig        | n Tools                              | 29 |  |

| 3.6 | Stream       | n Processor Design                   | 30 |  |

|     | 3.6.1        | Kernel-level ISA Requirement         | 32 |  |

|     | 3.6.2        | ALU Clusters                         | 33 |  |

|     | 3.6.3        | ALU Clusters Microarchitecture       | 34 |  |

|     | 3.6.4        | ALU Clusters Behavior                | 35 |  |

|     | 3.6.5        | Microkernel Controller               | 36 |  |

|     | 3.6.6        | Microkernel Controller               |    |  |

|     |              | Microarchitecture                    | 37 |  |

|     | 3.6.7        | Microkernel Controller Behavior      | 41 |  |

# **RESULTS AND DISCUSSION**

| 4.1 | Introduction                           |    |  |

|-----|----------------------------------------|----|--|

| 4.2 | Test Case 1: RGB to YUV Conversion     |    |  |

|     | 4.2.1 Instruction Fetch                | 48 |  |

|     | 4.2.2 Data Fetch and Memory Write Back | 48 |  |

|     | 4.2.3 Parallelism in Data Processing   | 48 |  |

| 4.3 | Test Case 2: Image Difference          | 53 |  |

| 4.4 | Test Case 3: Image Negative            | 54 |  |

| 4.5 | Test Case 4: Power-law Transformation  | 57 |  |

|                    | 4.6        | Resource and Performance Analysis | 59     |

|--------------------|------------|-----------------------------------|--------|

| 5                  | CONCLUSION |                                   |        |

|                    | 5.1        | Conclusion                        | 61     |

| REFERENCES         |            |                                   | 63     |

| Appendices A1 – C4 |            |                                   | 65-120 |

# LIST OF TABLES

# TABLE NO.TITLE

## PAGE

| 2.1 | Literature Review List                             | 7  |

|-----|----------------------------------------------------|----|

| 2.2 | SRF Stream as suggested by Rixner (2001).          | 13 |

| 2.3 | Stream Level ISA (Khailany, 2003).                 | 18 |

| 2.4 | Kernel Level ISA.                                  | 19 |

| 3.1 | Shows Resource Limitation and Usage for the Stream |    |

|     | Processor on Altera Cyclone IV GX.                 | 28 |

| 3.2 | Comparison between available HDL simulators.       | 30 |

| 3.3 | Kernel-level ISA for the stream processor design.  | 32 |

| 4.1 | Image different pixel snippets.                    | 57 |

| 4.2 | Performance analysis of the Stream Processor.      | 59 |

| 4.3 | Resources allocation for Stream Processor ALU and  |    |

|     | Microkernel Controller.                            | 60 |

# LIST OF FIGURES

| FIGURE NO. | TITLE                                                   | PAGE |

|------------|---------------------------------------------------------|------|

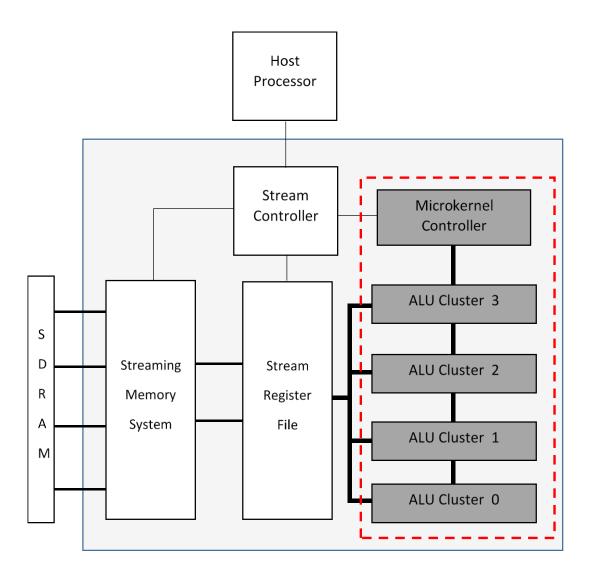

| 1.1        | Top level diagram of the stream processor. The scope of |      |

|            | this project is highlighted inside the red dashed box.  | 4    |

| 2.1        | Example of media processing involving data streams and  |      |

|            | kernels (Rixner, 2001).                                 | 10   |

| 2.2        | Imagine Processor Block Diagram. (Rixner, 2001).        | 11   |

| 2.3        | Imagine memory hierarchy.                               | 12   |

| 2.4        | Arithmetic Cluster (Rixner, 2001).                      | 14   |

| 2.5        | Functional Unit Details (Khailany, 2003).               | 15   |

| 2.6        | Microcontroller connections                             | 16   |

| 2.7        | Microcontroller micro-architecture design (Khailany,    |      |

|            | 2003).                                                  | 17   |

| 2.8        | VLIW Instruction Format (Khailany, 2003).               | 20   |

| 2.9        | Example timeline of stream command execution            |      |

|            | (Khailany et al., 2008).                                | 21   |

| 2.10       | Architecture of the ConvNet Processor proposed by       |      |

|            | Farabet et al. (2009).                                  | 22   |

| 2.11       | 2D Convolution operation as proposed by Farabet et al.  |      |

|            | The operation involve multiple units of adders and      |      |

|            | multiply-accumulate (Farabet et al., 2009).             | 23   |

| 2.12       | Alves and Diniz's (2011) organization of a custom       |      |

|            | streaming processor.                                    | 24   |

| 3.1        | Overall Project Methodology for Image Streaming         |      |

|            | Processor.                                              | 26   |

| 3.2        | Circuit Design Methodology for Image Streaming          |      |

|            | Processor.                                              | 29   |

| 3.3  | Top level diagram of Image Stream Processor, showing  |    |

|------|-------------------------------------------------------|----|

|      | the scope of this project in dashed box.              | 31 |

| 3.4  | Architecture of the arithmetic cluster unit.          | 34 |

| 3.5  | Microarchitecture of a Half Buffer Bank.              | 35 |

| 3.6  | High Level Behavior of ALU Cluster.                   | 36 |

| 3.7  | Top Block Diagram for Microkernel Controller Unit     | 38 |

| 3.8  | Block diagram for Microcode Loader and Microcode      |    |

|      | Storage.                                              | 39 |

| 3.9  | Microkernel Sequencer Block Diagram.                  | 40 |

| 3.10 | Microkernel Decoder Block Diagram.                    | 40 |

| 3.11 | State diagram of Microkernel Controller Sequencer.    | 41 |

| 3.12 | High Level Sequence of Microkernel Controller. The    | 42 |

|      | scope of this project is marked with red-dashed box.  |    |

| 3.13 | Bar diagram of the processing timeline of a stream    | 43 |

|      | processor (Khailany, 2008).                           |    |

| 4.1  | RGB to YUV conversion equation.                       | 45 |

| 4.2  | Data flow graph of RGB to YUV conversion.             | 45 |

| 4.3  | Stream-Kernel diagram form RGB to YUV conversion.     | 46 |

| 4.4  | Microkernel for RGB to YUV conversion.                | 46 |

| 4.5  | RGB888 was the input for the stream processor and the |    |

|      | resulting output was YUV888.                          | 47 |

| 4.6  | Modelsim waveform showing Instruction Fetch, follow   |    |

|      | by input with data streams.                           | 50 |

| 4.7  | Closed-up on memory fetch wave form.                  | 51 |

| 4.8  | Memory read and write back operation.                 | 51 |

| 4.9  | Data processed in parallel.                           | 52 |

| 4.10 | Image difference operation.                           | 53 |

| 4.11 | Image difference stream operation.                    | 53 |

| 4.12 | Image Difference Kernel.                              | 53 |

| 4.13 | Image Different inputs and outputs.                   | 54 |

| 4.14 | Waveform of image difference operation.               | 54 |

| 4.15 | Image negative stream operation.                      | 55 |

| 4.16 | Kernel-Stream diagram of image negative procedure.    | 55 |

| 4.17 | Image negative microkernel.                           | 55 |

|------|-------------------------------------------------------|----|

| 4.18 | Input (left) and result of Image Negative processing. | 56 |

| 4.19 | Power-law transformation equation.                    | 57 |

| 4.20 | Kernel-stream diagram for power-law transformation.   | 58 |

| 4.21 | Microkernel for power-law transformation.             | 58 |

| 4.22 | Input and output image for power-law transformation   | 59 |

|      | operation. The result were verified with Matlab.      |    |

# LIST OF ABBREVIATION

| ALU  | - | Arithmetic Logic Unit            |

|------|---|----------------------------------|

| FPGA | - | Field-Programmable Gate Array    |

| GPP  | - | General Purpose Processor        |

| ISA  | - | Instruction Set Architecture     |

| RTL  | - | Register Transfer Level          |

| SIMD | - | Single Instruction Multiple Data |

| VLIW | - | Very Long Instructions Words     |

LIST OF SYMBOLS

# LIST OF APPENDICES

| APPENDIX | TITLE                                      | PAGE |

|----------|--------------------------------------------|------|

| A1       | SystemVerilog source code for              |      |

|          | HALF_STREAM_BUFFER.sv                      | 65   |

| A2       | SystemVerilog source code for              |      |

|          | HALF_STREAM_BANK.sv                        | 66   |

| A3       | SystemVerilog source code for ALU.sv       | 68   |

| A4       | SystemVerilog source code for              |      |

|          | ALU_CLUSTERS.sv                            | 70   |

| A5       | SystemVerilog source code for              |      |

|          | MICROC_DECODER.sv                          | 72   |

| A6       | SystemVerilog source code for              |      |

|          | MICROC_STORE.sv                            | 82   |

| A7       | SystemVerilog source code for              |      |

|          | MICROC_LOADER.sv                           | 83   |

| A8       | SystemVerilog source code for              |      |

|          | MICROC_SEQUENCER.sv                        | 84   |

| A9       | SystemVerilog source code for MicroCont.sv | 87   |

| A10      | SystemVerilog source code for              |      |

|          | StreamProcessor.sv                         | 89   |

| A11      | SystemVerilog source code for              |      |

|          | StreamProcessor_TOP.sv                     | 90   |

| B1       | SystemVerilog testbench for                |      |

|          | testbench_MicroCont.sv                     | 92   |

| B2       | SystemVerilog testbench for                |      |

|          | testbench_RealRGBtoYUV100.sv               | 93   |

| B3 | SystemVerilog testbench for            | SystemVerilog testbench for |  |  |

|----|----------------------------------------|-----------------------------|--|--|

|    | testbench_RealImageNegative200.sv      | 100                         |  |  |

| B4 | SystemVerilog testbench for            |                             |  |  |

|    | testbench_RealImageDifference.sv       | 104                         |  |  |

| B5 | SystemVerilog testbench for            |                             |  |  |

|    | testbench_RealImagePowerLaw.sv         | 109                         |  |  |

| C1 | Matlab source code for Image2ByteMem.m | 115                         |  |  |

| C2 | Matlab source code for GenerateImage.m | 116                         |  |  |

| C3 | Matlab source code for ImagePower.m    | 118                         |  |  |

| C4 | Matlab source code for MakeNoise.m     | 119                         |  |  |

## **CHAPTER 1**

### INTRODUCTION

## **1.1 Background and Project Rationale**

Stream Processor is a type of *programmable processor* which exploit the *compute intensity*, *parallelism* and *producer-consumer locality* in order to process image and media efficiently (Khailany, 2003).

*Compute intensity* is defined as the number of arithmetic operation per global memory reference or I/O (Khailany et al., 2008) where media processing application such *as image processing, video compression and three-dimensional graphics* requires high rates of arithmetic compared to conventional computing application. Streaming programmable media processor which is designed to meet these demands usually contains tens to thousands arithmetic unit. This increases the challenge of providing the sufficient data bandwidth (Rixner, 2001).

On the other hand, *data parallelism* exists in stream processing because the same function is applied to many records of a stream and each record can be processed simultaneously without dependency from other records (Khailany et al., 2008). It is very common for media processing to be greatly enhance with parallelism. Parallelism in media processing can be categorized into three, which are instruction-level parallelism (ILP), data-level parallelism (DLP), and task-level Parallelism (TLP) (Khailany, 2003).

*Producer-consumer locality* is defines as specific temporal locality, where data is produced once, read once or twice later, and never read again (Khailany et al., 2008). In media processing, locality of reference for data accesses is another important

characteristic. The locality in media processing can be classified into kernel locality and producer-consumer locality (Khailany, 2003).

Other than equipped with large number of arithmetic logics, streaming processor architecture also equipped with a data bandwidth hierarchy such as the three tiered data bandwidth hierarchy in Imagine Processor, which enabled the processor to efficiently provide data bandwidth continuity for tens to hundreds of arithmetic units (Rixner, 2001).

Even though a conventional load/store CPU or more commonly known as general purpose CPU is also capable of processing media applications, a dedicated stream media processor promise greater performance given same amount of resource in term of area, gate count, and power since stream processor is design specifically to exploit the three characteristic mentioned previously.

Since streaming processor architecture is significantly important in electronic world and still actively being researched, I proposed this project to gain knowledge of inner working of a streaming processor architecture and to find out how to improve current designs with a focus on the VLIW Controller Unit and the Streaming Arithmetic clusters designs.

## **1.2 Project Problem Statement**

Recently, digital vision and imaging system have progressed greatly, but most of the algorithms such as 3D graphic, video compression, video decode and 2D image processing still requires high rates of arithmetic in the range of hundreds of billions operands per second (Rixner, 2001) making the integration with embedded system which are sensitive to power dissipation, physical size and cost very difficult. Historically, this application have been met with ASICs or ASSPS, but these solutions often lacking in flexibility. This project will propose a FPGA-based stream processor for vision and imaging purpose.

When processed on so-called conventional load-store CPU, most media processing algorithm take extremely large amount of CPU cycles and hence execution time which hindered real time media application on a digital system (Khailany et al. 2008). Due to the nature of conventional CPU memory architecture, media processing also require large amount of memory bandwidth and suffer higher rates if cache miss since the cache are not optimized to take advantage of producer-consumer locality of image processing (Khailany, 2003). The execution of multiple stream operators aggravates the processing unit-external memory bandwidth bottlenecks (Alves et al., 2011).

While fixed-function processors such as the one based on ASICs have been able to match the high performance demanded by media processing algorithm, programmability proved to be a key requirement in many digital systems which processed complex and evolving algorithm (Khailany et al., 2008). Programmable solutions also inherently have cost advantage over fixed function processor since a single programmable chip can be used in many different systems. As image resolutions, scene complexity and algorithmic complexity continue to rise, the demand for real time performance will continue to increase.

### **1.3 Project Objectives**

The objective of the project is to develop a programmable FPGA-based Stream Processor ALU and its Controller Unit for the purpose of common image processing algorithms.

The stream processor that is to be develop for the project will act as coprocessor which will offload specific image processing operation from a general purpose host CPU. The intended stream processor is expected to work in a similar manner as a Graphical Processing Unit (GPU) of a conventional PC, where common simple operation will be done by the GPP and the intended circuit will only process certain image processing algorithm.

The stream processor ALU will be developed with a set of internal buffers registers to improve stream memory efficiency and to avoid memory operation bottlenecks by eliminating register-to-memory operations for intracluster data movement.

### 1.4 Project Scope

The circuit module to be designed in this project will be part of a larger high speed FPGA-based embedded visual recognition system. This project will focus on Stream ALU (ALU Clusters) design and ALU Controller Unit. Stream memory components, except half buffer within the ALU Cluster, are out of scope of this project. Following diagram shows the scope of this project within the dashed red box.

**Figure 1.1:** Top level diagram of the stream processor. The scope of this project is highlighted inside the red dashed box.

The expected contribution of this project is a simulation model of the hardware ALU computation core and a micro kernel controller unit on Modelsim with a set of testbenches replicating the input of ALU and its controller. Items to be designed as part of the ALU Clusters consist of:

1. A set of functional units (FUs) for addition/subtract, multiply, divide, and logical shift left and right. It also support immediate operands and three input functional units.

2. ALU internal buffers or also known as Local Registers Buffers (Half Buffers) for all inputs of each functional units.

3. Interconnect between internal local buffers and FU outputs. This reduces memory bandwidth.

On the other hand, items to be designed as part of the Microkernel Controller consist of:

1. Very long instruction word (VLIW) control engines.

2. Microkernel storage to store the 'Kernels' (instructions).

3. Instruction fetch mechanism.

Signals from Stream Controller and data from SRF will be replicated within testbenches and generated with the help of Matlab code. The design for the stream processor is based on simplified Imagine Stream Processor.

## 1.5 Project Achievement

This project successfully modelled Stanford's Imagine Processor, which was a stream processor designed for custom VLSI, on a simulation with Altera Cyclone IV as the intended target. Imagine Stream processor is the state of the art stream processor that is designed for media processing application and still being actively researched and enhanced.

The design created in this project fulfil the resource limitation within Altera Cyclone IV including numbers of IO, number of LABs and dedicated memories. The design of the stream processor were successfully simplified while stream processing flow were maintained. From reviewing the existing literature on stream processor, it is found that this project could be the first project with complete documentation on the design and methodology which simulated the Imagine Processor using System Verilog on a FPGA.

The result of the image processing kernel from the stream processor were compared to the output of similar algorithm in Matlab and it is proven to be correct. Among the kernels tested are RGB to YUV conversion, image difference/subtract image inversion and power law transformation.

#### REFERENCES

- Alves, J. and Diniz, P. (2011). Custom FPGA-based micro-architecture for streaming computing. 2011 VII Southern Conference on Programmable Logic (SPL).

- Dessai, S. and Vutukuru, K. (2012). Design and Development of Stream Processor Architecture for GPU Application Using Reconfigurable Computing. *International Journal of Reconfigurable and Embedded Systems (IJRES)*, [online] 2(1). Available at: http://iaesjournal.com/online/index.php/IJRES/article/view/1309 [Accessed 17 Dec. 2014].

- Farabet, C., Poulet, C. and LeCun, Y. (2009). An FPGA-based stream processor for embedded real-time vision with Convolutional Networks. 2009 IEEE 12th International Conference on Computer Vision Workshops, ICCV Workshops.

- Gonzalez, R. and Woods, R. (2007). Digital image processing. Reading, Massachusetts: Addison-Wesley Publishing Company.

- Kapasi, U., Dally, W., Rixner, S., Mattson, P., Owens, J. and Khailany, B. (2000). Efficient conditional operations for data-parallel architectures. *Proceedings 33rd Annual IEEE/ACM International Symposium on Microarchitecture. MICRO-33* 2000.

- Kapasi, U., Dally, W., Rixner, S., Owens, J. and Khailany, B. (2002). The Imagine Stream Processor. Proceedings. IEEE International Conference on Computer Design: VLSI in Computers and Processors.

- Khailany, B. (2003). The VLSI Implementation and Evaluation of Area- And Energy-Efficient Streaming Media Processors. Ph.D. Stanford University.

Khailany, B., Williams, T., Lin, J., Long, E., Rygh, M., Tovey, D. and Dally, W.

(2008). A Programmable 512 GOPS Stream Processor for Signal, Image, and Video Processing. *IEEE J. Solid-State Circuits*, 43(1), pp.202-213.

- Kyrkou, C. (2014). Stream Processors and GPUs: Architectures for High Performance Computing. [online] Available at: http://sokryk.tripod.com/Stream\_Processors\_and\_GPUs\_-\_Architectures\_for\_High\_Performance\_Computing.pdf [Accessed 17 Dec. 2014].

- Msdn.microsoft.com, (2015). Converting Between YUV and RGB (Windows CE .NET 4.2). [online] Available at: https://msdn.microsoft.com/enus/library/ms893078.aspx [Accessed 23 May 2015].

- Rixner, S. (2001). *Stream Processor Architecture*. Boston, MA: Kluwer Academic Publishers.