## SYSTEMATIC TUNING PROCEDURE FOR ANALOG DESIGN REUSE METHODOLOGY

AHMAD FAISAL BIN ADNAN

UNIVERSITI TEKNOLOGI MALAYSIA

## SYSTEMATIC TUNING PROCEDURE FOR ANALOG DESIGN REUSE METHODOLOGY

### AHMAD FAISAL BIN ADNAN

A thesis submitted in fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > MARCH 2014

To my dearest family, friends, colleagues and Muslim brothers and sisters

#### ACKNOWLEDGEMENT

I would like to express my deepest gratitude especially to my main supervisor, Prof. Dr. Abu Khari A'ain, for his wise and continuous guidance, support and motivation throughout the research. I also want to thank to my co-supervisor, Dr. Nadzir Marsono for his technical guidance, advice and support.

Furthermore, I would like to express my heartfelt thanks to my mom and my wife for their wonderful support and motivation throughout the research. My sincere appreciation also extends to my family, friends, fellow colleagues and others who provided assistance at various occasions.

Ahmad Faisal Adnan Kepong, Kuala Lumpur - Malaysia

#### ABSTRACT

Shrinking transistor is undeniably important especially to reduce fabrication cost and to increase power efficiency of electronic devices. However, as fabrication technology progresses into deep submicron process, analog circuit design complexity grows significantly together with the increase in design time due to complex behaviour of short-channel Metal-Oxide-Semiconductor (MOS) transistor. Current scaling rules are incapable of maintaining circuit performance as design technology moves to deep submicron process. This research carries out a study on the effects of fabrication process migration on analog design reuse approach and offers a complementary design solution. In order to prove the concept, two-stage Operational Transconductance Amplifiers (OTA) have been designed using Silterra 0.18  $\mu$ m Complimentary-MOS (CMOS) fabrication process and were later migrated to Silterra 0.13  $\mu$ m. Existing scaling rules were adopted in the study in order to maintain the original circuit performance in 0.18  $\mu$ m process. The performance degradation problems due to the migration into a deep submicron process were observed. Then, a solid-state systematic transistor tuning procedure based on Direct Current (DC) output scaling rule was proposed and applied to rectify the performance degradation problem due to design migration. Result shows that it improves the accuracy of the analog design scaling and can be applied to both short-channel and long-channel designs. On a Miller amplifier test circuit, the proposed tuning stage results in an additional voltage gain up to 16 dB and twice faster settling time compared to a single-stage scaling alone, and approximately 33% less power consumption and 28% smaller silicon area when compared to the original design on 0.18  $\mu$ m process. The research is expected to contribute to current development of analog design reuse methodology.

#### ABSTRAK

Pengecutan transistor adalah perkara mustahak yang tidak dapat dinafikan terutamanya untuk mengurangkan kos fabrikasi dan untuk meningkatkan kecekapan kuasa dalam peranti elektronik. Walau bagaimanapun, seiring dengan teknologi fabrikasi yang bergerak menuju kawasan submikron mendalam, kerumitan mereka cipta litar analog dan masa yang terlibat meningkat dengan drastik disebabkan kelakuan transistor Logam-Oksida-Separa pengalir (MOS) bersaluran-pendek yang kompleks. Peraturan penskalaan analog kini tidak berupaya untuk mengekalkan prestasi litar ketika menuju proses submikron mendalam. Penyelidikan ini mengkaji kesan penghijrahan proses fabrikasi ke atas pendekatan penggunaan semula litar analog, dan menawarkan satu penyelesaian yang melengkapi. Untuk membuktikan konsep tersebut, litar Amplifier Operasi Transkonduksi (OTA) dua-peringkat direka menggunakan proses fabrikasi Pelengkap-MOS (CMOS) Silterra 0.18 µm dan kemudian dihijrahkan kepada Silterra 0.13  $\mu$ m. Peraturan penskalaan yang sedia ada digunapakai dalam kajian ini untuk mengekalkan prestasi litar asal pada proses 0.18  $\mu$ m. Masalah kemerosotan prestasi disebabkan penghijrahan kepada proses submikron mendalam diperhatikan. Kemudian, satu kaedah baru prosedur talaan transistor yang sistematik berdasarkan peraturan penskalaan output Arus Terus (DC) telah diusulkan dan digunakan bagi menyelesaikan masalah kemerosotan prestasi tersebut. Keputusan menunjukkan ia mampu meningkatkan ketepatan penskalaan rekaan analog dan boleh digunakan untuk kedua-dua rekaan saluran-pendek dan saluran-panjang. Pada litar ujian sebuah amplifier Miller, satu peringkat talaan usulan meningkatkan gandaan voltan amplifier sehingga 16 dB dan mencapai dua kali kepantasan masa penyelesaian apabila dibandingkan dengan penskalaan satu peringkat sahaja, dan dengan anggaran 33% lebih rendah penggunaan kuasa dan 28% luas silikon yang lebih kecil apabila dibandingkan dengan rekaan asal pada proses 0.18  $\mu$ m. Penyelidikan ini dijangka dapat menyumbang kepada pembangunan metodologi penggunaan-semula rekaan analog.

## TABLE OF CONTENTS

| CHAPTER |                    |          | TITLE                                | PAGE |

|---------|--------------------|----------|--------------------------------------|------|

|         | DECLARATION        |          |                                      | ii   |

|         | DEDI               | CATION   |                                      | iii  |

|         | ACK                | NOWLED   | GEMENT                               | iv   |

|         | ABST               | TRACT    |                                      | v    |

|         | ABST               | TRAK     |                                      | vi   |

|         | TABI               | LE OF CO | NTENTS                               | vii  |

|         | LIST               | OF TABL  | ES                                   | ix   |

|         | LIST               | OF FIGU  | RES                                  | xi   |

|         | LIST               | OF ABBR  | EVIATIONS                            | xiii |

|         | LIST               | OF SYME  | BOLS                                 | XV   |

|         | LIST OF APPENDICES |          |                                      | xvii |

| 1       | INTRODUCTION       |          |                                      | 1    |

|         | 1.1                | Scaling  | Rules and Design Reuse               | 1    |

|         | 1.2                | Probler  | n Statement                          | 2    |

|         | 1.3                | Objecti  | ves                                  | 3    |

|         | 1.4                | Scope of | of Work                              | 4    |

|         | 1.5                | Method   | łology                               | 4    |

|         | 1.6                | Contrib  | outions                              | 5    |

|         | 1.7                | Structu  | re of Thesis                         | 6    |

| 2       | LITE               | RATURE   | REVIEW                               | 7    |

|         | 2.1                | Challer  | nges of Analog Design Scaling        | 7    |

|         |                    | 2.1.1    | Power Supply Scaling                 | 7    |

|         |                    | 2.1.2    | Reduced Intrinsic Gain               | 9    |

|         |                    | 2.1.3    | Gate and Drain Leakages              | 10   |

|         |                    | 2.1.4    | MOSFET Short-Channel Effects         | 11   |

|         |                    | 2.1.5    | Analog Design Time in Deep Submicron |      |

|         |                    |          | Technologies                         | 12   |

| 2.2 | Analog | Analog Scaling Rules and Design Reuse |    |  |

|-----|--------|---------------------------------------|----|--|

|     | 2.2.1  | Scaling Rules by Galup-Montoro and    |    |  |

|     |        | Schneider                             | 14 |  |

|     | 2.2.2  | Scaling Rules by Savio et al.         | 17 |  |

|     | 2.2.3  | Scaling rules by Levi et al.          | 19 |  |

|     | 2.2.4  | Other Scaling Rules                   | 22 |  |

| 2.3 | Extend | ing the Scaling Rules                 | 24 |  |

## 3 IMPROVING ANALOG DESIGN REUSE METHODOLOGY

| 3.1 | Study on Alternative Scaling Parameter    | Study on Alternative Scaling Parameter 20 |  |  |

|-----|-------------------------------------------|-------------------------------------------|--|--|

| 3.2 | Scaling Stage                             | 27                                        |  |  |

| 3.3 | Proposed Transistor Tuning Procedure      | 30                                        |  |  |

| 3.4 | Multi-finger Transistor Circuits Examples | 33                                        |  |  |

|     | 3.4.1 Fabrication                         | 36                                        |  |  |

|     | 3.4.2 IC Testing                          | 38                                        |  |  |

| 3.5 | Chapter Summary                           | 39                                        |  |  |

| RESU | LTS AND | DISCUSSION                        | 40 |  |

|------|---------|-----------------------------------|----|--|

| 4.1  | Prelimi | Preliminary Result 40             |    |  |

| 4.2  | Circuit | s Performance Analyses            | 42 |  |

| 4.3  | Second  | ary Circuits Performance Analyses | 44 |  |

|      | 4.3.1   | Design Verification               | 46 |  |

|      | 4.3.2   | IC Characterization               | 51 |  |

| 4.4  | Chapte  | r Summary                         | 57 |  |

# 5CONCLUSION AND FUTURE WORK595.1Summary of the Main Findings59

5.2 Future Works 60

## REFERENCES

63

61

Appendix A

4

26

## LIST OF TABLES

| TA | BL | Æ | N | 0. |

|----|----|---|---|----|

|----|----|---|---|----|

## TITLE

| 2.1  | The scaling rules proposed by Galup-Montoro and        |    |  |  |  |

|------|--------------------------------------------------------|----|--|--|--|

|      | Schneider.                                             | 14 |  |  |  |

| 2.2  | The results of the scaling work by Galup-Montoro and   |    |  |  |  |

|      | Schneider.                                             | 15 |  |  |  |

| 2.3  | The improved scaling rules proposed by                 |    |  |  |  |

|      | Galup-Montoro et al.                                   | 16 |  |  |  |

| 2.4  | The results of improved scaling rules by               |    |  |  |  |

|      | Galup-Montoro et al.                                   | 16 |  |  |  |

| 2.5  | The scaling rules proposed by Savio et al.             | 18 |  |  |  |

| 2.6  | The results of the scaling work by Savio et al.        | 18 |  |  |  |

| 2.7  | The improved scaling rules by Savio et al.             | 19 |  |  |  |

| 2.8  | Three case studies of scaling rules by Levi at al.     | 20 |  |  |  |

| 2.9  | The scaling rules proposed by Levi et al.              | 21 |  |  |  |

| 2.10 | The results of the scaling work (Case-A).              | 21 |  |  |  |

| 2.11 | The transistor sizing for the case study (Case-A).     | 22 |  |  |  |

| 2.12 | The scaling rules proposed by Yang et al.              | 23 |  |  |  |

| 2.13 | Summary of the previous works on scaling rules.        |    |  |  |  |

| 3.1  | The preliminary test circuit variables and parameters. |    |  |  |  |

| 3.2  | Design parameters for the Miller OTA.                  | 28 |  |  |  |

| 3.3  | Scaling parameters for Silterra CMOS                   |    |  |  |  |

|      | 0.18 $\mu$ m and 0.13 $\mu$ m technologies.            | 28 |  |  |  |

| 3.4  | Simplified scaling rules for Silterra CMOS             |    |  |  |  |

|      | 0.18 $\mu$ m and 0.13 $\mu$ m technologies.            | 29 |  |  |  |

| 3.5  | Transistor sizing $(W/L)$ of the Miller OTA for long-  |    |  |  |  |

|      | channel and short-channel examples.                    | 29 |  |  |  |

| 3.6  | The output biasing voltage of the Miller OTA.          | 30 |  |  |  |

| 3.7  | Summary of test circuits Amp-A and Amp-B.              | 34 |  |  |  |

| 3.8  | The simplified scaling parameter for Silterra          |    |  |  |  |

|      | technologies.                                          | 34 |  |  |  |

| 3.9  | The transistor sizing for secondary test circuits.     | 36 |  |  |  |

| 4.1 | The average difference between $I_{DS0}$ and $I_{DS}$ from the |    |

|-----|----------------------------------------------------------------|----|

|     | simulation on Silterra 0.13 $\mu$ m process.                   | 41 |

| 4.2 | The performance of the Miller OTA before and after             |    |

|     | applying proposed tuning procedure.                            | 44 |

| 4.3 | The performance results of the secondary test circuits.        | 46 |

| 4.4 | The gain and phase margin of the amplifiers at corner          |    |

|     | process.                                                       | 48 |

| 4.5 | The amplifiers stability analysis using Z-test.                | 51 |

## LIST OF FIGURES

## FIGURE NO.

## TITLE PAGE

| 1.1  | Flowchart of the research methodology.                                |    |  |  |

|------|-----------------------------------------------------------------------|----|--|--|

| 2.1  | Power consumption with technology scaling for analog                  |    |  |  |

|      | circuits with fixed speed and accuracy requirements.                  | 8  |  |  |

| 2.2  | The effect of technology migration on power consump-                  |    |  |  |

|      | tion at a constant performance.                                       | 9  |  |  |

| 2.3  | The transistor intrinsic gain for 180 nm, 130 nm and                  |    |  |  |

|      | 90 nm technologies.                                                   | 10 |  |  |

| 2.4  | The effect of technology scaling on leakage current.                  | 11 |  |  |

| 2.5  | Velocity saturation in short-channel transistor.                      | 12 |  |  |

| 2.6  | The number of design rules for various technology                     |    |  |  |

|      | nodes.                                                                | 13 |  |  |

| 2.7  | The Miller OTA test circuit (Galup-Montoro).                          | 15 |  |  |

| 2.8  | The Miller OTA test circuit (Savio et al.).                           | 17 |  |  |

| 2.9  | The OTA test circuit (Levi et al.).                                   | 20 |  |  |

| 2.10 | Operational amplifier sizing process flow.                            | 24 |  |  |

| 3.1  | The test circuit to extract $I_{DS}$ - $V_{DS}$ relationship.         | 26 |  |  |

| 3.2  | The primary test circuit, a Miller OTA.                               | 27 |  |  |

| 3.3  | The flowchart of the scaling and proposed tuning stages               |    |  |  |

|      | and its related reference and equations.                              | 33 |  |  |

| 3.4  | The Amp-B with split-length PMOS transistors.                         | 35 |  |  |

| 3.5  | The split-length transistor idea.                                     | 35 |  |  |

| 3.6  | The top-level layout of the chip.                                     | 37 |  |  |

| 3.7  | The ESD protection circuit on the bond pads.                          | 38 |  |  |

| 3.8  | IC testing and measurement on the breadboard.                         | 39 |  |  |

| 4.1  | The NMOS transistor I-V curve for $I_{DS0}$ , $I_{DS1}$ and $I_{DS2}$ |    |  |  |

|      | at $V_{GS} = 0.7$ V.                                                  | 41 |  |  |

| 4.2  | The effect of biasing point $V_Y$ on (a) gain                         |    |  |  |

|      | (b) phase margin.                                                     | 43 |  |  |

| 4.3  | The gain-bandwidth curves of the original design and                  |    |  |  |

|      | migrated design with the proposed tuning applied.                     | 45 |  |  |

| 4.4  | The corner analyses for (a) Amp-A (b) Amp-B on                  |    |

|------|-----------------------------------------------------------------|----|

|      | Silterra 0.18 $\mu$ m process.                                  | 47 |

| 4.5  | The Monte Carlo simulation results of the phase margin          |    |

|      | of Amp-A for (a) 0.18 $\mu$ m process (b) 0.13 $\mu$ m process. | 49 |

| 4.6  | The Monte Carlo simulation results of the phase margin          |    |

|      | of Amp-B for (a) 0.18 $\mu$ m process (b) 0.13 $\mu$ m process. | 50 |

| 4.7  | Amp-A input-output signals response on-wafer test.              | 52 |

| 4.8  | Amp-B input-output signals response on-wafer test.              | 53 |

| 4.9  | The breadboard testing circuit.                                 | 54 |

| 4.10 | Amp-A input-output signal response for breadboard test.         | 56 |

| 4.11 | Amp-B input-output signal response for breadboard test.         | 57 |

|      |                                                                 |    |

## LIST OF ABBREVIATIONS

| AC       | - | Alternating Current                                    |

|----------|---|--------------------------------------------------------|

| ADC      | - | Analog-to-Digital Converter                            |

| AMS      | - | Analog Mixed Signal                                    |

| BSIM     | - | Berkeley Short-channel IGFET Model                     |

| CEDEC    | - | Collaborative Microelectronic Design Excellence Centre |

| CMOS     | - | Complementary Metal Oxide Semicodictor                 |

| COMDIAC  | - | Compilateur de Dispositifs Actifs                      |

| DC       | - | Direct Current                                         |

| DIBL     | - | Drain Induced Barrier Lowering                         |

| EDA      | - | Electronic Design Aided                                |

| ESD      | - | Electrostatic Discharge                                |

| FF       | - | Fast-PMOS Fast-NMOS                                    |

| GBW      | - | Gain-Bandwidth                                         |

| I/O      | - | Input-Output                                           |

| IC       | - | Integrated Circuit                                     |

| MOS      | - | Metal-Oxide-Semiconductor                              |

| MOSFET   | - | Metal Oxide Semiconductor Field Effect Transistor      |

| NML      | - | Non-Minimum Length                                     |

| NMOS     | - | N-type Metal Oxide Semiconductor                       |

| n-MOSFET | - | N-type MOSFET                                          |

| OTA      | - | Output Transconductance Amplifier                      |

| PMOS     | - | P-type Metal Oxide Semiconductor                       |

| p-MOSFET | - | P-type MOSFET                                          |

| SCE      | - | Short-Channel Effect                                   |

| SI       | - | Strong Inversion                                       |

| SoC      | - | System-on-Chip                                         |

| SPICE    | - | Simulation Program for Integrated Circuits Emphasis    |

| SS       | - | Slow-PMOS Slow-NMOS                                    |

| TT  | - | Typical-PMOS Typical-NMOS |

|-----|---|---------------------------|

| USM | - | Universiti Sains Malaysia |

| Vpp | - | Voltage peak-to-peak      |

| W/L | - | Width-to-Length           |

| WI  | - | Weak Inversion            |

|     |   |                           |

## LIST OF SYMBOLS

| W             | _ | Width of transistor                         |

|---------------|---|---------------------------------------------|

| L             | _ | Length of transistor                        |

| $I_D, I_{DS}$ | _ | Transistor drain-to-source current          |

| $V_{DD}$      | _ | Power supply voltage                        |

| $V_{DS}$      | _ | Transistor drain-to-source voltage          |

| $V_{GS}$      | - | Transistor gate-to-source voltage           |

| $V_{EG}$      | _ | Effective gate voltage                      |

| $V_{Th}$      | _ | Transistor threshold voltage                |

| $g_m$         | - | Transconductance of transistor              |

| P             | - | Power consumption                           |

| $t_{ox}$      | - | Transistor oxide thickness                  |

| $g_{ds}$      | - | Transistor drain-to-source transconductance |

| $A, A_V$      | _ | Voltage gain                                |

| $r_{ds}$      | _ | Transistor drain-to-source resistance       |

| $f_T$         | _ | Transition frequency                        |

| $C_{gs}$      | - | Transistor gate-to-source capacitance       |

| $C_{ox}$      | _ | Transistor oxide capacitance                |

| $C_C$         | - | Compensation capacitor                      |

| $C_L$         | - | Load capacitor                              |

| $V_E$         | - | Early voltage                               |

| $\mu$         | - | Electron mobility                           |

| $K_L$         | - | Gate length scaling parameter               |

| $K_W$         | _ | Width scaling parameter                     |

| $K_{wN}$      | _ | Width scaling parameter for n-MOSFET        |

| $K_{wP}$      | _ | Width scaling parameter for p-MOSFET        |

| $K_V$         | _ | Power supply scaling parameter              |

| $K_{ox}$      | _ | Oxide capacitance scaling parameter         |

|               |   |                                             |

| $K_{oxN}$       | _ | Oxide capacitance scaling parameter for n-MOSFET |

|-----------------|---|--------------------------------------------------|

| $K_{oxP}$       | — | Oxide capacitance scaling parameter for p-MOSFET |

| $K_E$           | — | Early voltage scaling parameter                  |

| $K_{\mu}$       | _ | Electron mobility scaling parameter              |

| $K_{\mu N}$     | _ | Electron mobility scaling parameter for n-MOSFET |

| $K_{\mu P}$     | _ | Electron mobility scaling parameter for p-MOSFET |

| $K_n$           | _ | Slope scaling parameter                          |

| $K_C$           | _ | Load capacitance scaling parameter               |

| $K_I$           | — | Current scaling parameter                        |

| $i_f$           | _ | Forward inversion level                          |

| $i_r$           | _ | Reverse inversion level                          |

| $\epsilon_{ox}$ | _ | Oxide relative permittivity                      |

| $W_f$           | _ | Finger width of transistor                       |

| $n_f$           | _ | Number of finger of transistor                   |

| $\lambda$       | _ | Channel modulation parameter                     |

| σ               | _ | Standard deviation                               |

## LIST OF APPENDICES

| APPENDIX | TITLE                | PAGE |

|----------|----------------------|------|

| А        | LIST OF PUBLICATIONS | 63   |

#### **CHAPTER 1**

#### INTRODUCTION

This research work studies the issues and challenges of analog CMOS design reuse methodology. The main objective is to formulate an analog design reuse methodology which is compatible with short-channel CMOS design. This work proposes a second-stage tuning methodology for analog design reuse to increase the accuracy in maintaining the original analog circuit performance for short-channel device. Silterra CMOS 0.18  $\mu$ m and 0.13  $\mu$ m fabrication processes are used in the study. The study is divided into two parts. The first part is to study the impact of process scaling on analog and mixed-signal designs. The second part is to formulate an extension of existing analog design reuse methodology for short-channel analog design application, and to rectify gain degradation problem which is usually associated with short-channel transistor.

#### 1.1 Scaling Rules and Design Reuse

Scaling rules are used to provide new transistor sizing while maintaining the original circuit performance during process migration. The performance of an analog circuit is highly dependent on process parameters. Therefore, it is important to study the relationship between process parameters and circuit performance to facilitate analog design reusability in various fabrication processes. The significant advantage of having systematic analog design reuse methodology is the shorter time needed for circuit rescaling compared to complete circuit redesign to meet the original specification.

Systematic analog design reuse methodology can assist designer in maintaining analog circuit performance in different processes. Digital circuits are easier to scale and usually can be done by automation, thus much less complex migration process involved compared to analog circuits. As the analog design complexity keep growing, systematic reuse methodology for analog circuits can help to reduce the design time. Existing scaling rules for analog design reuse have to sacrifice some performance matrics in order to maintain the more important matrics [1, 2, 3, 4, 5]. Furthermore, the scaling rules were tested to MOS field effect transistors (MOSFETs) with the gatelength equal to few micrometers [2, 4]. Therefore, this research proposes a tuning procedure to increase the accuracy of the design scaling, and it is compatible with short-channel design.

Emerging short-channel effects and leakage current contribute to the latest analog design challenges in deep submicron process [6]. Moreover, power supply scaling is the biggest challenge [7]. These design issues also contribute to the problems of the analog circuit performance when migrating into deep submicron process such as:

- Reduction in transistor intrinsic gain due to velocity saturation [8, 6]

- Reduction in signal to noise ratio as a result of using low supply voltage and ultra thin gate oxide [6]

- Higher signal distortion for transistor operating in weak inversion [8]

Due to high design sensitivity in deep submicron process, designer is now relying even more on simulator program and accurate device modeling [8]. Hundreds of parameters are defined to describe short-channel transistor behaviour in various biasing points, making hand calculation even more complex, time consuming and less reliable. The growing design complexity reflects growing analog design time which affect the timeto-market.

#### **1.2** Problem Statement

When one design migrates to a smaller process compared to its original size, it is expected that the performance of the design will be preserved if not better. However, previous works have proven that preserving all design specifications in a migrated design is not a straightforward process. Many reports [2, 3, 4, 5, 9, 10, 11] have highlighted that one may be able to preserve some of the specifications but not all. This issue is further aggravates when it involves migration to the deep submicron region.

Scaling rules can maintain gain-bandwidth and dynamic range of an operational amplifier during migration [1, 2]. However, the power consumption may doubled or the silicon area can be much larger compared to the original design [1, 2]. Another work with modified scaling rules and a follow-on automatic tuning stage result in significant power reduction but at a cost of few times bigger silicon area compared to the original design [3, 4].

Channel-scaling rules derived from the MOSFET level-1 current equation [5, 11] resulted in lower power consumption and smaller area while maintaining the gain, bandwidth and phase margin. However, in the smallest fabrication process tested (0.12 micron), the amplifier gain is degraded [5]. Besides, all earlier works [1, 2, 5, 11] were tested on considerable long-channel MOSFET. As technology progresses into the deep submicron technology, consideration of short-channel MOSFET in analog design migration must be taken into account.

The degradation of transistor intrinsic gain is one of the prominent design problems in short-channel analog design [8]. Amplifier gain which is widely considered as the most important performance in any analog amplifier is directly related to the intrinsic gain. This research aims to rectify the amplifier gain degradation problem in analog design migration which becomes more significance for migration into deep submicron process. Hence, the design reuse methodology is further enhanced by extending the compatibility of the scaling process with the short-channel analog design.

#### 1.3 Objectives

Based on the problem statement, this research work aims to achieve the following objectives:

- i. To propose a tuning procedure for analog design reuse which can be applied to both short-channel and long-channel MOSFETs. The tuning procedure can compliment existing scaling works which are more suitable for long-channel transistors.

- To preserve the operational amplifier performance (gain, bandwidth and phase margin) during process migration at reduced power consumption and silicon area.

#### 1.4 Scope of Work

This research aims to upgrade existing scaling rules with the proposed tuning procedure. The proposed tuning procedure is compatible with both long-channel and short-channel analog designs and able to maintain circuit performance during the process migration. Operational transconductance amplifier (OTA) circuits are used as the test circuits. The circuits are designed and characterized by using Cadence electronic design automation (EDA) on Silterra 0.18  $\mu$ m process. Using scaling rules proposed in [5], the designs are migrated to 0.13  $\mu$ m Silterra process. The proposed tuning procedure is then applied to the migrated designs. The significant of the tuning procedure is presented by tables and graphs generated by Matlab software. Selected designs are sent for fabrication at Silterra Malaysia and the IC is characterized using on-wafer test by Collaborative Microelectronic Design Excellence Centre (CEDEC) of Universiti Sains Malaysia (USM). Next, the IC is packaged, a test circuit is constructed using off-chip components and characterized using Agilent test and measurement instruments.

#### 1.5 Methodology

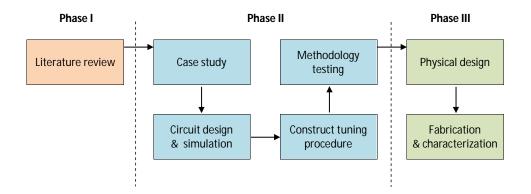

This research is divided into three phases as shown in Figure 1.1. The first phase is the background study of scaling rules and analog scaling challenges. Then, problem statement is constructed based on the study.

The second phase started with a case study to formulate the design reuse methodology. Based on preliminary results from a case study, this research decided to propose a tuning procedure to achieve the objectives. The idea of preserving the output swing during design migration is translated into equations which guide the entire tuning process. This phase involves the circuit design and design migration stages. During these stages, operational amplifier circuits are designed on 0.18  $\mu$ m and then characterized. Then the same designs are migrated to 0.13  $\mu$ m process and characterized. Performance degradation of the migrated design in the 0.13  $\mu$ m especially on short-channel design leads to the construction of tuning methodology stage. In this stage, a DC output voltage scaling is proposed and related equations are derived to adjust the output voltage of the two-stage analog amplifier. The last stage is testing the methodology on another amplifier designs to evaluate the performance of the proposed tuning procedure. Corner analysis and Monte Carlo simulation are used

to measure the reliability of the designs.

In the second phase, similar OTA circuits used in previous literature [1, 2, 3, 4, 5, 11] are adopted as the test circuits. They are constructed using short-channel or long-channel MOSFETs to represent two cases along with Miller compensation circuit to realize high output gain. Five key performance indicators are considered to be maintained during the design migration: voltage gain, bandwidth, phase margin, power consumption, and silicon area. The proposed tuning procedure aims to maintain the key performance during the process migration from 0.18  $\mu$ m to 0.13  $\mu$ m processes at a minimal trade-off. In addition, amplifier circuits with multi-finger and split-length transistors are used to verify the methodology.

The third phase of the research is to fabricate the design and characterized the physical IC. The layout from the selected design is prepared for fabrication by Silterra Malaysia using 0.18  $\mu$ m CMOS process. The physical design is then characterized using on-wafer test and breadboard test. The related problems and limitations are discussed and analyzed in Chapter 4.

Figure 1.1: Flowchart of the research methodology.

#### **1.6** Contributions

This research work contributes on an improved design reuse methodology that is suitable for both long- and short-channels transistors. Specifically, the contribution of the research are as follow:

- i. The preservation of the output swing is taken into consideration which leads to the tuning procedure based on the scaled value of DC output voltage. This helps maintain the voltage gain and phase margin.

- ii. Instead of tuning both width and length of the transistor, this thesis proposes the tuning of the width to adjust the DC output voltage. This is to ensure the transistor threshold voltage is maintained. Another advantage of scaling the width is to avoid short-channel effects (SCE) and drain-induced barrier lowering (DIBL) from being significantly modified.

#### **1.7** Structure of Thesis

The thesis is organized into five chapters. The rest of the chapters are as follow.

Chapter 2 discusses the analog design migration challenges into deep submicron technology and existing scaling rules and its theories, advantages and limitations.

Chapter 3 presents the design scaling and the proposed tuning procedure based on DC output scaling. It is divided into four sections: the preliminary experiment, the design scaling, the proposed tuning procedure and the proposed tuning for multi-finger transistors.

Chapter 4 presents the performance analysis of the proposed tuning procedure for all circuit examples and the result of the physical design characterization.

Finally, conclusion and suggestions for future works are presented in Chapter 5.

#### REFERENCES

- Galup-Montoro, C. and Schneider, M. Resizing Rules for The Reuse of MOS Analog Designs. Manaus: *Proceedings of the 13th Symposium on Integrated Circuits and Systems Design.* 2000. 89–93.

- 2. Galup-Montoro, C., Schneider, M. and Coitinho, R. Resizing Rules for MOS Analog-Design Reuse. *IEEE Design & Test of Computers*, 2002. 19(2): 50–58.

- Savio, A., Colalongo, L., Kovacs-Vajna, Z. and Quarantelli, M. Scaling Rules and Parameter Tuning Procedure for Analog Design Reuse in Technology Migration. *Proceedings of the International Symposium on Circuits and Systems*. 2004. V–117–V–120 Vol. 5.

- 4. Savio, A., Colalongo, L., Quarantelli, M. and Kovacs-Vajna, Z. Automatic Scaling Procedures for Analog Design Reuse. *IEEE Transactions on Circuits and Systems I*, 2006. 53(12): 2539–2547.

- 5. Levi, T., Tomas, J., Lewis, N. and Fouillat, P. A CMOS Resizing Methodology for Analog Circuits. *IEEE Design & Test of Computers*, 2009. 26(1): 78–87.

- 6. Sansen, W. Analog Design Challenges in Nanometer CMOS Technologies. *IEEE Asian Solid-State Circuits Conference*. 2007. 5–9.

- Annema, A., Nauta, B., van Langevelde, R. and Tuinhout, H. Analog Circuits in Ultra-Deep-Submicron CMOS. *IEEE Journal of Solid-State Circuits*, 2005. 40(1): 132–143.

- Murmann, B., Nikaeen, P., Connelly, D. J. and Dutton, R. W. Impact of Scaling on Analog Performance and Associated Modeling Needs. *IEEE Transactions on Electron Devices*, 2006. 53(9): 2160–2167.

- Yang, T., Gao, M., Wu, S. and Guo, D. A New Reuse Method of Analog Circuit Design for CMOS Technology Migration. *International Conference on Anti-Counterfeiting Security & Identification in Communication*. 2010. 112–115.

- Acosta, R., Silveira, F. and Aguirre, P. Experiences on Analog Circuit Technology Migration and Reuse. *Proceedings of the 15th Symposium on Integrated Circuits and Systems Design*. 2002. 169–174.

- Levi, T., Lewis, N., Tomas, J. and Fouillat, P. Scaling Rules for MOS Analog Design Reuse. *Proceedings of the International Conference of Mixed Design* of Integrated Circuits and System. 2006. 378–382.

- Gielen, G. and Dehaene, W. Analog and Digital Circuit Design in 65 nm CMOS: End of The Road? *Proceedings in Europe on Design, Automation and Test.* 2005. 37–42 Vol. 1.

- Garg, M., Suryagandh, S. and Woo, J. Scaling Impact on Analog Performance of Sub-100nm MOSFETs for Mixed Mode Applications. *European Conference on Solid-State Device Research*. 2003. 371–374.

- 14. Borkar, S. Design Challenges of Technology Scaling. *IEEE Micro*, 1999. 19(4): 23–29.

- 15. Gray, P., Hurst, P., Meyer, R. and Lewis, S. *Analysis and Design of Analog Integrated Circuits.* 5th ed. John Wiley & Sons. 2010.

- 16. Lewyn, L. and Williams, N. Is A New Paradigm for Nanoscale Analog CMOS Design Needed? *Proceedings of the IEEE*, 2011. 99(1): 3–6.

- Saleh, R., Wilton, S., Mirabbasi, S., Hu, A., Greenstreet, M., Lemieux, G., Pande, P. P., Grecu, C. and Ivanov, A. System-on-Chip: Reuse and Integration. *Proceedings of the IEEE*, 2006. 94(6): 1050–1069.

- 18. Vittoz, E. Future of Analog in The VLSI Environment. *IEEE International Symposium on Circuits and Systems*. 1990. 1372–1375.

- Cunha, A., Schneider, M. and Galup-Montoro, C. An MOS Transistor Model for Analog Circuit Design. *IEEE Journal of Solid-State Circuits*, 1998. 33(10): 1510–1519.

- 20. Press, W., Teukolsky, S., Vetterling, W. and Flannery, B. *Numerical Recipes in C++: The Art of Scientific Computing*. Cambridge University Press. 2002.

- 21. Dessouky, M., Kaiser, A., Lou, M. and Greiner, A. Analog Design for Reuse

Case Study: Very Low-Voltage Sigma-Delta Modulator. Proceedings on Design, Automation and Test. 2001. ISBN 0-7695-0993-2. 353–360.

- 22. Porte, J. COMDIAC: Compilateur de Dispositifs Actifs, reference manual. *Ecole Nationale Supérieure des Télécommunications, Paris, France*, 1997.

- 23. Morshed, T. *et al. BSIM4.6.4 MOSFET Model-User's Manual*. University of California, Berkeley. 2009.

- Taherzadeh, S. and Hamoui, A. A 1-V Process-Insensitive Current-Scalable Two-Stage Opamp With Enhanced DC Gain and Settling Behavior in 65-nm Digital CMOS. *IEEE Journal of Solid-State Circuits*, 2011. 46(3): 660–668.