## NETWORK-ON-CHIP FAULT DETECTION AND ROUTER SELF-TEST

WAN MOHD AMIR HARIS BIN WAN SALLEHUDDIN

UNIVERSITI TEKNOLOGI MALAYSIA

Replace this page with form PSZ 19:16 (Pind. 1/07), which can be obtained from SPS or your faculty.

Replace this page with the Cooperation Declaration form, which can be obtained from SPS or your faculty.

## NETWORK-ON-CHIP FAULT DETECTION AND ROUTER SELF-TEST

## WAN MOHD AMIR HARIS BIN WAN SALLEHUDDIN

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical - Computer & Microelectronic System)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > DECEMBER 2014

Dedicated, in thankful appreciation for support and encouragement to my beloved wife Nabilah, my daughter Aleesya, my parents, families and friends.

#### ACKNOWLEDGEMENT

During the preparation of this thesis, I had met with many people, researchers and academicians who had provided me lots of advice and guidance. In particular, I would like to express my deepest appreciation to my main thesis supervisor, Associate Professor Dr. Muhammad Nadzir Marsono for his continuous support, guidance, critics and motivations throughout the entire project. I truly appreciate all the support, guidance and critics provided as this help me to become a better researcher in Electrical and Electronics Engineering field. Also, I would like to thank to the members of the examination committee. I also would like to express my gratitude to all my family members who have been supporting and motivating me throughout my academic years. This academic year was not easy to complete especially need to handle both work and academic workload at the same time. Hence, I am grateful to all my family members who support me all the ways. My sincere appreciation also extends to all my colleagues and friends who have provided me the advantageous suggestions, cooperation and technical support. Unfortunately, it is not possible to list all of them in this limited space. However, their assistances are highly appreciated.

#### ABSTRACT

Network-on-Chip (NoC) router is an entity that facilitates communication between subsystem or IP cores on an integrated circuit. Faults such as permanent fault, transient fault and random fault are commonly observed on a NoC router. They may severely impact the functionality of an NoC router if not handled appropriately. This project proposes a mechanism to identify error and perform self-testing in NOC router by enhancing the Register Transfer Level (RTL) design of CONNECT NoC Baseline Router with error detection mechanism, as well as devising a built in selftest mode for NOC router. Both proposed error detection mechanism and built in self-test mode have been successfully implemented using System Verilog. The work presented in this project shows possible enhancement to NoC router architecture to detect erroneous packets. NoC router is able to detect faults through proposed error dection tecchniques. This allows router self-test in order to sustain the functionality of a system in the presence of faults. Simulation results show that additional logics do not affect NoC router performance.

#### ABSTRAK

Rangkaian-pada-Chip (NoC) router adalah entiti yang memudahkan komunikasi antara subsistem atau IP teras pada litar bersepadu. Kerosakan seperti kerosakan kekal, sementara dan rawak biasanya terjadinya pada router NoC. Kerosakan ini boleh memberi kesan teruk kepada fungsi sesuatu router NOC jika tidak ditangani dengan sewajarnya. Projek ini mencadangkan satu mekanisme untuk mengenal pasti kesilapan dan melakukan ujian diri dalam NoC router dengan meningkatkan Tahap Daftar Pemindahan (RTL) reka bentuk NoC Router dengan mekanisme pengesanan ralat, serta merangka terbina dalam mod ujian diri untuk NoC router. Keduadua mekanisme pengesanan ralat dicadangkan dan dibina dalam mod ujian diri telah berjaya dilaksanakan dengan menggunakan Sistem Verilog. Kerja-kerja yang dibentangkan dalam projek ini menunjukkan peningkatan mungkin untuk seni bina router NoC untuk mengesan paket salah. NoC router mampu mengesan kesalahan melalui dicadangkan tecchniques ralat dection. Ini membolehkan router sendiri ujian-bagi mengekalkan fungsi sistem yang di hadapan-dosa. Keputusan simulasi menunjukkan bahawa Logika tambahan tidak menjejaskan prestasi router NoC.

# TABLE OF CONTENTS

| CHAPTER | TITLE                |                                             | PAGE |  |

|---------|----------------------|---------------------------------------------|------|--|

|         | DECLARATION          |                                             |      |  |

|         | DED                  | ICATION                                     | iii  |  |

|         | ACK                  | NOWLEDGEMENT                                | iv   |  |

|         | ABST                 | TRACT                                       | v    |  |

|         | ABST                 | TRAK                                        | vi   |  |

|         | TABI                 | LE OF CONTENTS                              | vii  |  |

|         | LIST                 | OF TABLES                                   | ix   |  |

|         | LIST                 | OF FIGURES                                  | Х    |  |

|         | LIST                 | OF ABBREVIATIONS                            | xii  |  |

| 1       | INTRODUCTION         |                                             | 1    |  |

|         | 1.1                  | Overview                                    | 1    |  |

|         | 1.2                  | Faults on Network on Chip Router            | 2    |  |

|         | 1.3                  | Problem Statement                           | 2    |  |

|         | 1.4                  | Objective and Scope                         | 4    |  |

|         | 1.5                  | Report Organization                         | 4    |  |

| 2       | LITE                 | RATURE REVIEW                               | 6    |  |

|         | 2.1                  | Network-On-Chip (NoC) Architecture          | 6    |  |

|         | 2.2                  | NoC Error Detection                         | 8    |  |

|         | 2.3                  | Self-testing Solution on NoC                | 10   |  |

|         | 2.4                  | Chapter Summary                             | 12   |  |

| 3       | RESEARCH METHODOLOGY |                                             | 13   |  |

|         | 3.1                  | Research Framework                          | 13   |  |

|         | 3.2                  | RTL Design Methodology                      | 15   |  |

|         | 3.3                  | Verilog Design using Quartus II Web Edition |      |  |

|         |                      | Software                                    | 16   |  |

|        | 3.4  | Verification using Modelsim-Altera Web Edition Software | 17 |

|--------|------|---------------------------------------------------------|----|

|        | 3.5  | CONfigurable NEtwork Creation Tool (CON-                |    |

|        |      | NECT)                                                   | 17 |

|        | 3.6  | Chapter Summary                                         | 19 |

| 4      | NETV | WORK-ON-CHIP FAULT DETECTION AND                        | I  |

|        | ROUT | FER SELF-TEST                                           | 20 |

|        | 4.1  | Network-on-Chip Fault Detection and Router Self-        |    |

|        |      | Test Overview                                           | 20 |

|        | 4.2  | Errorneous Packet Detection Mechanism                   | 21 |

|        |      | 4.2.1 Error Detection                                   | 22 |

|        |      | 4.2.2 Packet Counter & Logging Counter                  | 22 |

|        |      | 4.2.3 Overall Error Detection Mechanism                 | L  |

|        |      | Arithmetic State Machine (ASM) chart                    | 23 |

|        | 4.3  | Propose Router Self-test Mechanism                      | 24 |

|        |      | 4.3.1 Built-in-self Test                                | 24 |

|        |      | 4.3.2 Stop and Go Automated Repeat Request              |    |

|        |      | (ARQ)                                                   | 24 |

|        |      | 4.3.3 Router Under Test mode ASM Chart                  | 25 |

|        | 4.4  | Chapter Summary                                         | 26 |

| 5      | HARI | DWARE DESIGN, SYNTHESIS AND VERIFICA-                   |    |

|        | TION |                                                         | 27 |

|        | 5.1  | Normal NoC Router Design                                | 27 |

|        |      | 5.1.1 Packet Transmission                               | 28 |

|        |      | 5.1.2 Packet Receiving                                  | 28 |

|        | 5.2  | Packet Logging Mechanism Simulation                     | 29 |

|        | 5.3  | Built-in-Self Test Simulation                           | 32 |

|        | 5.4  | Circuit Timing and Resources                            | 36 |

|        | 5.5  | Chapter Summary                                         | 38 |

| 6      | CON  | CLUSION                                                 | 39 |

|        | 6.1  | Research Outcomes                                       | 39 |

|        | 6.2  | Future Works                                            | 39 |

| REFERE | NCES |                                                         | 41 |

| REFERENCES |  |  |

|------------|--|--|

| Appendix A |  |  |

# LIST OF TABLES

## TABLE NO.

## TITLE

## PAGE

| 2.1 | Synthesis Results for CONNECT and SOTA Mesh Network.                  | 7  |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Summary of error detection related works                              | 10 |

| 2.3 | Summary of router self-test related works                             | 12 |

| 5.1 | 13 bit flit with 8 bit data packet on every router                    | 27 |

| 5.2 | Simulation operation table                                            | 28 |

| 5.3 | Packet Logging and CRC fault free test-case operation table           | 30 |

| 5.4 | Packet Logging and CRC with fault injection test-case operation table | 31 |

| 5.5 | Analysis & Synthesis Resource usage Summary for Basic                 | -  |

| 5.6 | NoC router.<br>Analysis & Synthesis Resource usage Summary for NoC    | 37 |

|     | router with Packet Logging and BIST mechanism.                        | 37 |

| 5.7 | Comparison table between basic NoC and NoC with Packet                |    |

|     | logging and BIST mechanism                                            | 38 |

# LIST OF FIGURES

## FIGURE NO.

## TITLE

## PAGE

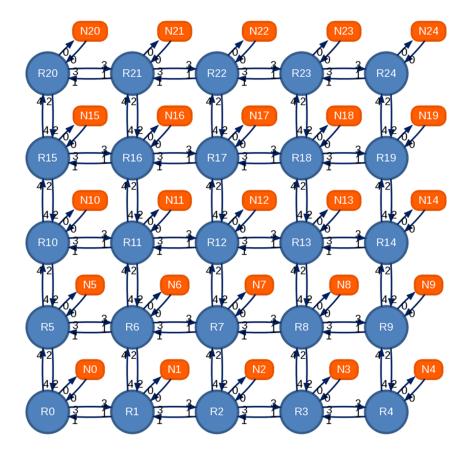

| 1.1 | Example of NoC network with $5 \times 5$ mesh topology.      | 2  |

|-----|--------------------------------------------------------------|----|

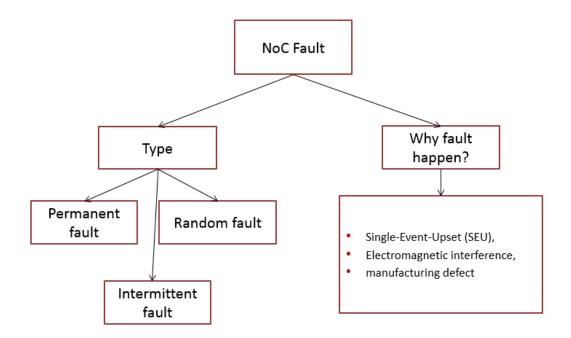

| 1.2 | Types of NoC fault and factors.                              | 3  |

| 2.1 | XY Modulo Routing                                            | 8  |

| 2.2 | Code Disjoint Detection                                      | 9  |

| 2.3 | Packet Logging based on NACK counter                         | 10 |

| 2.4 | Example Built In Self-Test in NoC, External test source      |    |

|     | injected to Source and destination router                    | 11 |

| 3.1 | Research Framework                                           | 14 |

| 3.2 | RTL Design Methodology                                       | 15 |

| 3.3 | Details on project methodology based on objective            | 16 |

| 3.4 | Quartus II Altera Design Tool                                | 17 |

| 3.5 | CONNECT Web Tool                                             | 18 |

| 4.1 | NOC 'x' and 'y' Adaptive routing                             | 21 |

| 4.2 | Packet Logging                                               | 21 |

| 4.3 | CRC location in NoC                                          | 22 |

| 4.4 | Packet logging mechanism ASM chart                           | 23 |

| 4.5 | Router Under Test block diagram                              | 24 |

| 4.6 | Stop and Go Automated Repeat Request (ARQ) block             |    |

|     | diagram                                                      | 25 |

| 4.7 | RUT ASM chart                                                | 25 |

| 5.1 | Send flit from source router output waveform                 | 28 |

| 5.2 | Receive flit at destination router waveform                  | 29 |

| 5.3 | Overall simulation output waveform for both send and receive |    |

|     | flit operation.                                              | 29 |

| 5.4 | Packet Logging ALU and CRC Block Diagram                     | 30 |

| 5.5 | Packet Logging and CRC fault free simulation waveform        | 31 |

| 5.6 | Packet Logging and CRC with fault injection simulation       |    |

|     | waveform                                                     | 32 |

| 5.7 | BIST Block Diagram                                           | 33 |

| 5.8 | BIST mechanism flow                                          | 34 |

|     |                                                              |    |

| 5.9  | BIST simulation waveform                          | 34 |

|------|---------------------------------------------------|----|

| 5.10 | Simulation result on Router 0 (Fault Free Router) | 35 |

| 5.11 | Simulation result on Router 1 (Faulty Router)     | 35 |

| 5.12 | FIFO Memory Block Diagram.                        | 36 |

| A.1  | NoC router block diagram.                         | 60 |

# LIST OF ABBREVIATIONS

| ASM     | - | Arithmetic State Machine           |

|---------|---|------------------------------------|

| ASM     | - | Automated Repeat Request           |

| BIST    | - | Built-In-Self-Test                 |

| CDD     | - | Code Disjoint Detection            |

| cpd     | - | critical path delay                |

| CONNECT | - | Configurable Network Creation Tool |

| CRC     | - | Cyclic Redundancy Clock            |

| NoC     | - | Networks-on-Chip                   |

| PL      | - | Packet Logging                     |

| RTL     | - | Register Transfer Level            |

| SOTA    | - | state-of-the-art                   |

### **CHAPTER 1**

### **INTRODUCTION**

#### 1.1 Overview

Network-on-Chip (NoC) router is an entity that facilitates communication between subsystem or IP cores on an integrated circuit. Faults such as permanent fault, transient fault and random fault are commonly observed on a NoC router. NoC and interconnection networks have been subjects of research since early days of computing. Since the year 2005 [1], the field of NoC has begun due to the beginning of multi-core CPUs and the foreseeable tendency towards massively integrated manycore architectures. Networks-on-Chip (NoC) by far constitute the largest subsystem in many core architectures. Compared to bus subsystems, they offer reduced hardware overhead, better scalability, and higher data throughput. By adjusting design parameters, such as NoC network topology, IP allocation algorithm and flow control mechanism, NoCs can be flexibly adapted to application requirements.

Within the next 10 years, continued scaling will enable thousands of cores to be integrated with NoCs as the central backbone. As NoCs provide inherently redundant communication pathways, they are potentially robust against partial failure [2]. To exploit this property, adequate choices of fault models, error detection, diagnosis procedures, fault tolerance and reconfiguration have to be investigated on all layers of the network. Error detection and faults tolerance in NoC can be consider as a good field to study in order to optimize the performance and functionality of NoC network. Since current NoC does not have capailities of fault tolerance, NoC performance cannot achieved 100% accuracy.

**Figure 1.1**: Example of NoC network with  $5 \times 5$  mesh topology.

### **1.2** Faults on Network on Chip Router

Faults in NoC router can be classified as permanent fault, transient fault and random fault [3]. Permanent fault in router means that some of faults that cannot be recover or permanently there after continous packets had been injected on the same router. Based on researched, there are few factors that can be lead faults in NoC. Figure 1.2 shows the summary on faulty in Network On Chip Router.

### **1.3 Problem Statement**

Baseline NoC design such as CONNECT cannot detect errorneous in NoC such as permanent fault, transient fault and random fault. In order to overcome this, error detection, fault tolerance and router reconfiguration have to be investigated on all layer of the network in order to come out a solution to handle faults and error in NOC router.

Figure 1.2: Types of NoC fault and factors.

By enhancing basic NoC design with error detection in order mitigate errors and faults. Actions can be taken to maintain NoC operation in order to keep the functionality of the router, enhancement on router self-test also need to be focus in this research.

Several works had been proposed for these two enhancements, but some techniques uses high logic resources and this lowers the performance of the NoC routers itself. Code Disjoint Detection (CDD) [4] by Grecu and Wrapper for router scan-chains attached to each router by Abady [5] were proposed in order to handle the fault tolerance in NoC router. These techniques require external circuits to perform error detection and router testing which can reduce the performance of NoC router itself.

By improving these ideas, a solution that can perform error detection mechanism by comparing Cyclic Redundancy Cycle (CRC) on input and output packet of each router and enabling router self-testing mode can be used to detect errorneous and faulty packets in NoC.

#### **1.4 Objective and Scope**

The goal of this research is to enhance basline CONNECT NoC router with enabling mechanism for online fault detection on NoC. Specifically the objectives of this project report are:

- 1. To enhance the RTL Design of CONNECT NoC Router with packet detection mechanism by comparing Cyclic Redundancy Cycle (CRC) on input and output packets of the First In First Out (FIFO) of every router memory to allow errorneous packets detection.

- 2. To propose a built in self-test mode mechanism on NoC router by implement pre-identify test vector that had been hardcoded in logic register in the router design hence to clarify the faulty router.

Network On Chip Router designed by using CONNECT router network RTL system as a baseline router architecture on  $4 \times 4$  Mesh topology router network with x-y adaptive routing mechanism. First enhancement is enable packet logging mechanism into every NoC router by modifying CONNECT Router design. This is done by creating subs module in the RTL by adding error detection and error counter into the design. Next is to enable Router self-test mode with enabling pre-identify tests pattern into every single router in the system. This scope is more focus on adding extra state in network system which is called "*Router under test mode*". For this project, the system is totally designed in software and a test bench is use to validate both mechanism and mode on Network-on-Chip router design as discussed. Both RTL design and test bench are in Verilog and System Verilog using Altera Quartus II and Modelsim-Altera CAD tool as logic synthesizing tool and hardware simulation tool.

### **1.5** Report Organization

This project report consists of six chapters. The rest of this report are organized as follows.

Chapter 2 covers the literature review and discuss about the research of the fault tolerance and self-test for existing NoC router.

Chapter 3 covers the system overview of this project. It describes the various modules development and basic operation of each module. Two modules enhancement will be described briefly in this chapter.

The elaboration of the system development and methodology will be discussed in Chapter 4. All method and option used for this project will be described briefly in this chapter. The result system effectiveness is also discussed in this chapter.

Chapter 5 explains the testing and result of each module. The result system effectiveness is also discussed in this chapter.

Chapter 6 summarizes the project outcome. A few suggestions are proposed to enhance the design in the future.

#### REFERENCES

- 1. A. Amory, E. Briao, E. Cota, M. Lubaszewski, and F. Moraes, "A scalable test strategy for network-on-chip routers," 2005.

- 2. R. Marculescu and UmitY.Ogras, "Outstanding research problems in noc design: System, microarchitecture, and circuit perspectives," 2009.

- 3. M. Radetzki and C. Feng, "Methods for fault tolerance in networks-on-chip," 2013.

- C. Grecu, A. Ivanov, E. S. R. Saleh, and P. Pande, "Online fault detection and location for noc interconnects," 2013 IEEE 31st VLSI Test Symposium (VTS), 2006.

- 5. M. Hosseinabady, A. Banaiyan, M. Bojnordi, , and Z. Navabi, "A concurrent testing method for noc switches," 2006.

- 6. D. Park, C. Nicopoulos, N. V. J. Kim, and C. Das, "Exploring fault-tolerant network-on-chip architectures," 2006.

- 7. C. Grecu, P. Pande, A. Ivanov, and R. Saleh, "Bist for network-on-chip interconnect infrastructures," no. 5, 2006.

- 8. M. K. Papamichael and J. C. Hoe, "Connect: Re-examining conventional wisdom for designing nocs in the context of fpgas," 2012.

- 9. R. Marculescu, "Outstanding research problems in noc design: System, microarchitecture, and circuit perspectives," 2009.

- 10. P. Pande, C. Grecu, A. Ivanov, R. Saleh, and G. D. Micheli, "Design, synthesis and test of networks on chip," 2004.

- 11. A. Kumar, "Toward ideal on-chip communication using express virtual channels," 2008.

- 12. S. Murali, T. Theocharides, N. Vijaykrishnan, L. B. M. Irwin, and G. D. Micheli, "Analysis of error recovery schemes for networks on chips," 2005.

- 13. C. M. Concatto, "Coping with permanent faults in nocs by using adaptive strategies based on router design-level and routing algorithm-level," 2004.

- L. K. Loo, C. Y. Ooi, V. Y. Liew, Y. W. Hau, and M. N. Marsono, "Packet logging mechanism for adaptive online fault detection on network-on-chip," 2014.

- 15. K. Petersen and J. Oberg, "Toward a scalable test methodology for 2d-mesh network-on-chips," pp. 30–35, 2007.

- 16. A. K, "Logic bist and scan test techniques for multiple identical blocks," 2002.

- 17. C. Aktouf, "A complete strategy for testing an on-chip multiprocessor architecture," 2002.

- 18. "Utm thesis manual," 2007.

- 19. "Connect tool," 2007.