# DIGITAL MODELLING TEST TECHNIQUE FOR MIXED MODE CIRCUITS

LEONG MUN HON

UNIVERSITI TEKNOLOGI MALAYSIA

# DIGITAL MODELLING TEST TECHNIQUE FOR MIXED MODE CIRCUITS

LEONG MUN HON

A thesis submitted in fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > JUNE 2005

Specially dedicated to

My beloved parents and sisters My Xiao Tian Xin, Yen Nee

### ACKNOWLEDGEMENT

I would like to express my deepest gratitude to Assoc. Prof. Dr. Abu Khari b. A'ain (my supervisor) and Dr. Soloman Max who gave me the guidance and supports I needed. Without their continued motivation and interest, this thesis would not have been the same as presented here.

Besides, I am extremely grateful to all the seniors, especially Mr. Ting Hua Nong and Miss Ooi Chia Yee. There are also indebted to technicians such as Kak Nurul, Kak Shuki, Kak Seri and others, whichever playing important roles on the thesis completion; especially to Kak Mas, who represents FKE for SPS to deal with all postgraduate matters.

Finally, I would also like to thank my fellow friends such as Ober, Tai Kuan, Zem Peng, Hwee Ling, Jon Fea and others who have provided me with their helps and views, and make this project a success.

### ABSTRACT

Recent demands in mobile communications, process control, automotive ASICs and smart sensors has accelerated the mixed-signal market and escalated the importance of mixed-signal test development. Mixed-signal circuit or mixed mode circuit is normally tested separately based on their core function. However, there is no guarantee that such testing approach would ensure that the system would function perfectly as a single entity. The main objective of this research is to investigate the application of digital modelling testing technique on mixed mode circuits. Digital modelling test technique is a method in which the test vector is simplified as a digital test vector. The investigation examined the suitable defect models as well as test procedures. The research also investigates the effectiveness of employing power supply voltage control (PSVC) testing technique together with the digital modelling. The reason of this test approach is due to independent reports of the effectiveness of these two test techniques. The circuit under test in this work includes a second order Butterworth low pass filter, an ADC and an op-amp. These circuits were chosen to represents a family of mixed – analogue and digital circuits. For comparison purpose, the ADC was tested using code density or histogram test technique. An analysis at bias point is presented to highlight why certain defects are exposed while others are not. The overall results showed that digital modelling test technique is able to model and expose unified analogue and mixed-signal faults. This is supported by the results from testing on discrete and CMOS circuitries. PSVC test coupled with digital model and pulse sampling can increase fault coverage for digital modelling test technique. The main advantages of digital model are it can reduce test time and eliminate circuit partitioning test.

### ABSTRAK

Keperluan kini dalam bidang telekomunikasi mudah-alih, kawalan proses, ASICs untuk automotif dan penggesan pintar telah mempercepatkan pasaran isyarat bercampur dan merangsangkan kepentingan bidang perkembangan pengujian isyarat bercampur. Litar isyarat bercampur atau litar mod bercampur adalah diuji secara berasingan mengikut kepada fungsi dasarnya. Bagaimanapun, kaedah pengujian ini tidak dapat memastikan bahawa sistem yang diuji akan berfungsi dengan baik seperti dalam satu unit. Objektif utama dalam penyelidikan ini adalah untuk menyiasat aplikasi teknik pengujian permodelan digit bagi litar isyarat bercampur. Teknik pengujian permodelan digit adalah satu penyelesaian dimana vektor-vektor pengujian disimpifikasi kepada vektor-vektor digit. Kajian ini memeriksa kesesuaian model kecacatan dan prosedur pengujian. Penyelidikan ini juga menyiasat keberkesanan dalam penggunaan teknik pengujian pengawalan voltan bekalan kuasa (PSVC) berserta dengan teknik pengujian permodelan digit. Ini adalah berdasarkan kepada laporan berasingan tentang keberkesanan kedua-dua teknik pengujian. Litar-litar dalam pengujian untuk kerja ini adalah termasuk penapis laluan rendah Butterworth peringkat kedua, penukar analog kepada digit dan penguat operasian. Litar-litar ini dipilih untuk mewakili keluarga litar bercampur – litar-litar analog dan digit. Untuk tujuan perbandingan, penukar analog kepada digit diuji menggunakan densiti kod atau teknik pengujian histogram. Analisis kepada titik bias dipersembahkan untuk menunjukkan kenapa sesetengah kecacatan dapat dikesan dan yang lainnya tidak. Keseluruhan keputusan menunjukkan bahawa teknik pengujian permodelan digit adalah berkebolehan untuk memodel dan mengesan kecacatan kesatuan litar analog dan isyarat bercampur. Ini disokong dengan keputusan pengujian litar diskrit dan CMOS. Teknik PSVC bersama-sama dengan permodelan digit dan persampelan dedenyut dapat meninggikan liputan kecacatan teknik pengujian permodelan digit. Kebaikan utama teknik pengujian permodelan digit adalah ia dapat menggurangkan masa pengujian dan menggelakan pengujian litar secara pengagihan.

# **TABLE OF CONTENTS**

### CHAPTER

1

# TITLE

### PAGE

| TITLE                | i    |

|----------------------|------|

| DECLARATION          | ii   |

| DEDICATION           | iii  |

| ACKNOWLEDGEMENT      | iv   |

| ABSTRACT             | V    |

| ABSTRAK              | vi   |

| CONTENTS             | vii  |

| LIST OF TABLES       | xii  |

| LIST OF FIGURES      | XV   |

| LIST OF SYMBOLS      | xvii |

| LIST OF APPENDICES   | XX   |

| LIST OF PUBLICATIONS | xxi  |

# INTRODUCTION11.1Background and motivation11.2Problem statement41.3Objective51.4Goal51.5Scope51.6Thesis layout6

# LITERATURE REVIEW

| 2.1 | Analogue and mixed mode IC test          | 8  |

|-----|------------------------------------------|----|

|     | 2.1.1 Importance of IC test              | 8  |

|     | 2.1.2 Functional test versus parametric  | 9  |

|     | test                                     |    |

| 2.2 | Specification-based analogue and         | 10 |

|     | mixed-signal IC test                     |    |

|     | 2.2.1 DC parametric test (analogue       | 11 |

|     | portion)                                 |    |

|     | 2.2.1.1 Leakage test                     | 11 |

|     | 2.2.1.2 Impedance measurement            | 11 |

|     | 2.2.1.3 Offset measurement               | 12 |

|     | 2.2.1.4 Gain measurement                 | 13 |

|     | 2.2.1.5 Power supply rejection           | 13 |

|     | ratio                                    |    |

|     | 2.2.1.6 Common-mode rejection            | 14 |

|     | ratio                                    |    |

|     | 2.2.2 DC parametric test (Digital        | 14 |

|     | portion)                                 |    |

|     | 2.2.2.1 $I_{IH}/I_{IL}$ measurement      | 14 |

|     | $2.2.2.2 V_{IH}/V_{IL}$ measurement      | 14 |

|     | $2.2.2.3 V_{OH}/V_{OL}$ measurement      | 15 |

|     | $2.2.2.4 I_{OH}/I_{OL}$ measurement      | 15 |

|     | $2.2.2.5 I_{OSH}/I_{OSL}$ (short circuit | 15 |

|     | current) measurement                     |    |

|     | 2.2.3 AC parametric test (analogue       | 16 |

|     | portion)                                 |    |

|     | 2.2.3.1 Gain and level tests             | 16 |

|     | 2.2.3.2 Phase tests                      | 17 |

|     | 2.2.3.3 Distortion tests                 | 18 |

|     | 2.2.3.4 Signal rejection test            | 19 |

8

|     | 2.2.3.5 Crosstalk                       | 20 |

|-----|-----------------------------------------|----|

|     | 2.2.3.6 Noise tests                     | 21 |

| 2.3 | Defect-oriented testing technique       | 21 |

|     | 2.3.1 Supply current monitoring test    | 22 |

|     | technique                               |    |

|     | 2.3.1.1 Quiescent supply current        | 22 |

|     | test (I <sub>DDQ</sub> test)            |    |

|     | 2.3.1.2 Dynamic/ Transient power        | 23 |

|     | supply current test (I <sub>DDT</sub>   |    |

|     | test)                                   |    |

|     | 2.3.2 Power supply voltage control test | 23 |

|     | technique                               |    |

|     | 2.3.3 Transient response testing (TRT)  | 24 |

|     | Technique                               |    |

|     | 2.3.4 Digital modelling test technique  | 26 |

| 2.4 | Conventional ADC test technique (using  | 26 |

|     | statistical data processing method)     |    |

|     | 2.4.1 Histogram/ code density test      | 27 |

|     | 2.4.1.1 Linear ramp histogram           | 27 |

|     | approach                                |    |

|     | 2.4.1.2 Sinusoidal histogram            | 28 |

|     | approach                                |    |

|     | 2.4.2 Other conventional ADC testing    | 28 |

|     | techniques                              |    |

|     | 2.4.2.1 Sine wave curve-fitting test    | 28 |

|     | 2.4.2.2 ADC spectral test               | 29 |

|     | 2.4.2.3 Output response                 | 30 |

|     | transformation                          |    |

|     | 2.4.3 Static ADC measurements           | 30 |

|     | 2.4.3.1 DC gain error                   | 30 |

|     | 2.4.3.2 DC offset error                 | 31 |

|     | 2.4.3.3 Differential Nonlinearity       | 32 |

|     | (DNL) error                             |    |

|     | 2.4.3.4 Integral Nonlinearity (INL) |  | 32 |

|-----|-------------------------------------|--|----|

|     | error                               |  |    |

| 2.5 | Fault model                         |  | 34 |

| 3 | 3.1 | Project introduction               | 36 |

|---|-----|------------------------------------|----|

| 3 | 3.2 | Project approach                   | 37 |

|   |     | 3.2.1 Project flow                 | 37 |

|   |     | 3.2.2 Fault model                  | 39 |

|   |     | 3.2.3 Faulty and fault free        | 42 |

|   |     | 3.2.4 Test frequency               | 42 |

| 3 | 3.3 | Circuit under test (CUT)           | 43 |

|   |     | 3.3.1 Second-order low pass filter | 43 |

|   |     | 3.3.2 3-bit flash ADC              | 46 |

|   |     | 3.3.2.1 Digital modelling test     | 48 |

**RESEARCH METHODOLOGY**

|     | 3.3.2.1 Digital modelling test       | 48 |

|-----|--------------------------------------|----|

|     | technique                            |    |

|     | 3.3.2.2 Code density/ histogram      | 49 |

|     | test                                 |    |

|     | 3.3.2.3 Power supply voltage         | 50 |

|     | control test coupling with           |    |

|     | digital modelling test               |    |

|     | technique                            |    |

|     | 3.2.3.4 Pulse transition sampling    | 50 |

|     | 3.3.3 Operational Amplifier (Op-Amp) | 51 |

| 3.4 | Mathematical calculation and applied | 52 |

|     | tools                                |    |

|     | 3.4.1 Sallen-key low pass filter     | 52 |

|     | 3.4.2 Histogram test technique (ramp | 53 |

|     | input)                               |    |

analysis

| 4 | <b>RESULT AND DISCUSSION</b>                  | 59  |

|---|-----------------------------------------------|-----|

|   | 4.1 Active analogue filter                    | 59  |

|   | 4.1.1 CUT with unity gain                     | 59  |

|   | 4.1.2 CUT with non-unity gain                 | 65  |

|   | 4.2 3-bit Flash Analogue-to-digital converter | 70  |

|   | 4.3 Differential Op-Amp                       | 79  |

| 5 | CONCLUSION, FUTURE WORK AND                   | 88  |

| 5 | SUGGESTION                                    | 00  |

|   | 5.1 Conclusion                                | 88  |

|   | 5.2 Future Work and suggestion                | 89  |

|   | REFERENCES                                    | 91  |

|   | APPENDIX A                                    | 96  |

|   | APPENDIX B                                    | 105 |

|   | APPENDIX C                                    | 106 |

|   | APPENDIX D                                    | 107 |

|   | APPENDIX E                                    | 108 |

|   | APPENDIX F                                    | 109 |

|   | APPENDIX G                                    | 117 |

|   | APPENDIX H                                    | 129 |

# LIST OF TABLES

| <b>TABLE</b> | NO. |

|--------------|-----|

|--------------|-----|

# TITLE

# PAGE

| Characteristics comparison between functional                                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| and parametric test                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Various signal to noise and distortion formula                                              | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| The tradeoffs for different ADC functional testing                                          | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| techniques                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Configurations of PSVC test coupling with                                                   | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Digital modelling test technique                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Experimental result for low pass filter testing                                             | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Fault coverage for hard short and open faulty                                               | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| component (experimental)                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fault coverage for CUT with $gain = 11$                                                     | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Fault coverage for undetected faults in 2 <sup>nd</sup> , 3 <sup>rd</sup> , 5 <sup>th</sup> | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| and 7 <sup>th</sup> cutoff harmonics                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fault coverage for large resistive short fault in                                           | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| resistor string module                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fault coverage for large resistive short fault in                                           | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| comparator module                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fault coverage for large resistive short fault in                                           | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| encoder module                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fault coverage for narrow open fault in resistor                                            | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| string module                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Fault coverage for narrow open fault in                                                     | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| comparator module                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                             | <ul> <li>and parametric test</li> <li>Various signal to noise and distortion formula</li> <li>The tradeoffs for different ADC functional testing techniques</li> <li>Configurations of PSVC test coupling with</li> <li>Digital modelling test technique</li> <li>Experimental result for low pass filter testing</li> <li>Fault coverage for hard short and open faulty component (experimental)</li> <li>Fault coverage for CUT with gain = 11</li> <li>Fault coverage for undetected faults in 2<sup>nd</sup>, 3<sup>rd</sup>, 5<sup>th</sup> and 7<sup>th</sup> cutoff harmonics</li> <li>Fault coverage for large resistive short fault in resistor string module</li> <li>Fault coverage for large resistive short fault in encoder module</li> <li>Fault coverage for narrow open fault in resistor string module</li> <li>Fault coverage for narrow open fault in</li> </ul> |

| 4.10 | Fault coverage for short-to- $V_{GND}$ fault in resistor | 73 |

|------|----------------------------------------------------------|----|

|      | string module                                            |    |

| 4.11 | Fault coverage for short-to- $V_{GND}$ fault in          | 73 |

|      | comparator module                                        |    |

| 4.12 | Fault coverage for short-to- $V_{GND}$ fault in encoder  | 73 |

|      | module                                                   |    |

| 4.13 | Fault coverage for short-to- $V_{DD}$ fault in resistor  | 73 |

|      | string module                                            |    |

| 4.14 | Fault coverage for short-to- $V_{DD}$ fault in           | 73 |

|      | comparator module                                        |    |

| 4.15 | Fault coverage for short-to- $V_{DD}$ fault in encoder   | 73 |

|      | module                                                   |    |

| 4.16 | Change in the operating region of faulty transistor      | 75 |

|      | when fault is introduced                                 |    |

| 4.17 | Fault coverage for each defect at different              | 78 |

|      | observing points                                         |    |

| 4.18 | The change of the CUT's operating points for             | 79 |

|      | exposed defects                                          |    |

| 4.19 | Result of faulty device/node (with large resistive       | 80 |

|      | short) and their characteristics                         |    |

| 4.20 | Result of faulty device/node (with narrow open)          | 81 |

|      | and their characteristics                                |    |

| 4.21 | Result of faulty device/node (with short-to- $V_{DD}$ )  | 82 |

|      | and their characteristics                                |    |

| 4.22 | Result of faulty device/node (with short-to- $V_{GND}$ ) | 82 |

|      | and their characteristics                                |    |

| 4.23 | Faults which do not change the CUT operating             | 83 |

|      | points at all                                            |    |

| 4.24 | Faults unable to propagate to the output                 | 83 |

| 4.25 | Result of faulty device/node (with large resistive       | 84 |

|      | short) and their characteristics                         |    |

| 4.26 | Result of faulty device/node (with narrow open)          | 84 |

|      | and their characteristics                                |    |

| 4.27 | Result of faulty device/node (with short-to- $V_{DD}$ )  | 85 |

|------|----------------------------------------------------------|----|

|      | and their characteristics                                |    |

| 4.28 | Result of faulty device/node (with short-to- $V_{GND}$ ) | 85 |

|      | and their characteristics                                |    |

| 4.29 | Output level versus minimum applied load                 | 86 |

# LIST OF FIGURES

FIGURE NO.

# TITLE

# PAGE

| 1.1  | ABM of an output pin                           | 2  |

|------|------------------------------------------------|----|

| 1.2  | Chip structure                                 | 2  |

| 2.1  | Basic PSR and PSRR setup                       | 20 |

| 2.2  | Channel to channel crosstalk                   | 20 |

| 2.3  | Comparator and its Karnaugh map                | 26 |

| 2.4  | Gain error for a linear 3-bit ADC after offset | 31 |

|      | error correction                               |    |

| 2.5  | Offset error for a bipolar ADC                 | 31 |

| 2.6  | Transfer function for DNL error                | 32 |

| 2.7  | Transfer function for INL error                | 33 |

| 2.8  | Analogue and mixed mode circuit catastrophic   | 35 |

|      | fault model                                    |    |

| 3.1  | Project Flowchart                              | 38 |

| 3.2  | Applied fault models                           | 39 |

| 3.3  | Hard fault introduces to a discrete CUT        | 40 |

| 3.4  | Resistive fault introduces to a CMOS CUT       | 41 |

| 3.5  | Experiment setup for low pass filter           | 44 |

| 3.6  | Low Pass Filter schematic for experiment       | 44 |

| 3.7  | LPF with $A_V = 11$ and $f_{cutoff} = 10$ -kHz | 46 |

| 3.8  | 3-bit ADC (Netlist and full schematic show in  | 47 |

|      | Appendix A and B)                              |    |

| 3.9  | 3-bit ADC block diagram                        | 47 |

| 3.10 | Fault free signatures for ADC with different   | 49 |

initial logic

|      | lilitiai logic                                          |    |

|------|---------------------------------------------------------|----|

| 3.11 | Open-loop Op-Amp tests by Digital modelling             | 51 |

| 3.12 | General Sallen-Key low pass filter                      | 52 |

| 3.13 | GUI for bias point analysis                             | 56 |

| 3.14 | Bias point analysis flow chart                          | 57 |

| 4.1  | Faulty and fault free response for Node 2 (at 1         | 60 |

|      | kHz test frequency)                                     |    |

| 4.2  | Transient response for faulty R2 (at 1 kHz test         | 63 |

|      | frequency)                                              |    |

| 4.3  | The output responses of R <sub>2</sub> open circuit     | 65 |

| 4.4  | Faulty responses (R3-hard short and R4-hard             | 66 |

|      | open) in transient time                                 |    |

| 4.5  | Faulty responses (R3-hard short and R4-hard             | 67 |

|      | open) in frequency domain for low pass filter           |    |

|      | with fault free gain, $Av = 11$                         |    |

| 4.6  | Undetected output response for low pass filter          | 68 |

|      | with gain, $Av = 11$                                    |    |

| 4.7  | Output signature of M <sub>278</sub> for fault free and | 74 |

|      | faulty transistor                                       |    |

| 4.8  | Distribution of $V_{GS}$ and $V_{DS}$ for Digital       | 77 |

|      | modelling test (with initial stimuli logic 0) for       |    |

|      | faulty transistors                                      |    |

| 4.9  | Op-Amp fault free response                              | 80 |

| 4.10 | Undetected Op-Amp faulty response                       | 87 |

| 5.1  | Microcontroller based digital tester                    | 90 |

|      |                                                         |    |

# LIST OF SYMBOLS

| ASIC                        | - | Application Specified Integrated Circuit            |  |

|-----------------------------|---|-----------------------------------------------------|--|

| PGA                         | - | Programmable Gain Amplifier                         |  |

| GUI                         | - | Graphic User Interface                              |  |

| LPF                         | - | Low Pass Filter                                     |  |

| ADC                         | - | Analogue to Digital Converter                       |  |

| DAC                         | - | Digital to Analogue Converter                       |  |

| PLL                         | - | Phase locked Loop Circuit                           |  |

| SoC                         | - | System on Chip                                      |  |

| MCM                         | - | Multi Chip Module                                   |  |

| DfT                         | - | Design for Test                                     |  |

| BisT                        | - | Build in self Test                                  |  |

| IEEE                        | - | Institute of Electrical and Electronics Engineer    |  |

| SPICE                       | - | Simulation Program with Integrated Circuit Emphasis |  |

| VHDL                        | - | Verilog High Description Language                   |  |

| V <sub>o-cm</sub>           | - | Common-mode offset                                  |  |

| V <sub>os</sub>             | - | Input offset voltage                                |  |

| PSS                         | - | Power supply sensitivity                            |  |

| $\Delta V_{O}$              | - | Rate of change output voltage                       |  |

| $\Delta PS^+$               | - | Rate of change positive power supply                |  |

| $\Delta PS^{-}$             | - | Rate of change negative power supply                |  |

| PSRR                        | - | Power supply rejection ratio                        |  |

| CMRR                        | - | Common-mode rejection ratio                         |  |

| $G_{\scriptscriptstyle CM}$ | - | Common-mode gain (DC)                               |  |

| $G_{\scriptscriptstyle D}$  | - | Differential gain (DC)                              |  |

| $V_{\text{CM}}$             | - | Common-mode signal                                  |  |

| $\mathbf{I}_{\mathrm{IH}}$  | - | Input leakage current, logic high                   |  |

| $I_{IL}$                   | - | Input leakage current, logic low       |

|----------------------------|---|----------------------------------------|

| $\mathbf{V}_{\mathrm{IH}}$ | - | Input high voltage                     |

| $\mathbf{V}_{\mathrm{IL}}$ | - | Input low voltage                      |

| V <sub>OH</sub>            | - | Output high voltage                    |

| $V_{OL}$                   | - | Output low voltage                     |

| I <sub>OH</sub>            | - | Output high current                    |

| I <sub>OL</sub>            | - | Output low current                     |

| I <sub>OSL</sub>           | - | Current flowing into the pin           |

| I <sub>OSH</sub>           | - | Current flowing out of the pin         |

| Re                         | - | Real part                              |

| Im                         | - | Imaginary part                         |

| <b>τ</b> (f)               | - | Group delay                            |

| $G_{cm}(f)$                | - | Common-mode gain (AC)                  |

| $G_{diff}(f)$              | - | Differential gain (AC)                 |

| X <sub>rl</sub>            | - | Channel's input                        |

| $X_{lr}$                   | - | Channel's output                       |

| ICN                        | - | Idle channel noise                     |

| INL                        | - | Integral Nonlinearity                  |

| DNL                        | - | Differential Nonlinearity              |

| ω <sub>o</sub>             | - | Angular applied frequency              |

| FFT                        | - | Fast Fourier Transform                 |

| I <sub>DDQ</sub>           | - | Quiescent current                      |

| I <sub>DDT</sub>           | - | Dynamic/Transient power supply current |

| PSVC                       | - | Power Supply Voltage Control           |

| TRT                        | - | Transient Response Test                |

| CV                         | - | Coefficient Variation                  |

| PRBS                       | - | Pseudorandom Binary Sequence           |

| LFSR                       | - | Linear Feedback Shift Register         |

| DM                         | - | Digital modeling                       |

| Op-Amp                     | - | Operational Amplifier                  |

| H(s)                       | - | Transfer function                      |

| K                          | - | Filter gain                            |

| $\omega_{\pi}$             | - | Natural frequency                      |

|                            |   |                                        |

| Q                                                                                | - | Quality factor                             |

|----------------------------------------------------------------------------------|---|--------------------------------------------|

| ξ                                                                                | - | Damping ratio                              |

| Y                                                                                | - | Detectable                                 |

| Ν                                                                                | - | Not detectable                             |

| D                                                                                | - | Drain open                                 |

| S                                                                                | - | Source open                                |

| G                                                                                | - | Gate open                                  |

| **                                                                               | - | No repetition                              |

| D-S                                                                              | - | Drain and Source terminal short            |

| G-D                                                                              | - | Gate and Drain terminal short              |

| G-S                                                                              | - | Gate and Source terminal short             |

| ^                                                                                | - | Fault detected at (500.06-500.24) us       |

| Θ                                                                                | - | Fault detected at (1.00002-1.00015) ms     |

| @#                                                                               | - | Analogue modules (resistor and comparator) |

| &#</td><td>-</td><td>Digital module (priority encoder)</td></tr></tbody></table> |   |                                            |

# LIST OF APPENDICES

# APPENDIX

# TITLE

# PAGE

| А | 3-bit ADC Schematic Netlist                        | 96  |

|---|----------------------------------------------------|-----|

| В | 3-bit ADC Full Circuitry                           | 105 |

| С | Op-Amp Schematic Netlist                           | 106 |

| D | Op-Amp Full Circuitry                              | 107 |

| E | Histogram Test                                     | 108 |

| F | MATLAB Scripts for Bias Point Analysis             | 109 |

| G | Filter: short-to- $V_{DD}$ and short-to- $V_{GND}$ | 117 |

| Н | Filter: hard open and hard short                   | 129 |

### LIST OF PUBLICATIONS

### NO. TITLE

Leong Mun Hon and Abu Khari bin A'ain. Simple Analogue Active Filter Testing Using Digital Modelling. *Proceeding of the 2003 Third Student Conference on Research and Development (SCOReD 2003).* August 25-26, 2003. UPM, Malaysia: IEEE. 2003. ELE-5/6.

Leong Mun Hon and Abu Khari bin A'ain. An Investigation on ADC Testing Using Digital Modelling. *Proceedings of the 2004 IEEE Region-10 Conference (TENCON 2004).* November 21-24, 2004. Ching Mai, Thailand: IEEE. 2004. 245-249.

Leong Mun Hon and Abu Khari bin A'ain. Digital Modelling for Op-Amp Circuit Testing. *Proceeding of the 2004 International Conference on Semiconductor Electronics (ICSE 2004).* December 7-9, 2004. UKM, Malaysia: IEEE. 2004. 538-541.

### **CHAPTER 1**

## INTRODUCTION

### **1.1 Background and Motivation**

The trend towards the implementation of entire systems on chip and growing markets in mobile communications, process control, automotive ASICs and smart sensors has accelerated the mixed-signal market and escalated the importance of mixed-signal test development.

A mixed-signal circuit, or in generally mixed mode circuit, is defined as a circuit consisting of both digital and analogue elements in a single entity. Examples of basic mixed mode realm are CMOS analogue switch, programmable gain amplifier (PGA), analogue-to-digital converter (ADC), digital-to-analogue converter (DAC), phase-locked-loop (PLL), and other complex mixed mode circuits such as System-on-Chip (SoC), Application Specific Integrated Circuit (ASIC) and Multi-chip Module (MCM).

For the current IC trend - increase in the number of circuit nodes and circuit complexity, Design-for-Test (DfT) becomes the mainstream of mixed-signal test development in order to reduce test cost due to test pin limited. There are a variety of DfT and BisT techniques proposed for different mixed mode circuits. One of the current issues is to provide a consistent and structured framework for system-level and board-level test development, and for DfT approaches. Hence, IEEE 1149.4-1999 was born.

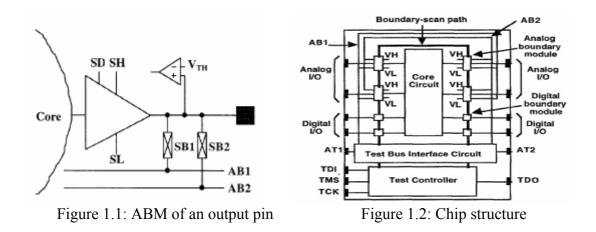

Nowadays, many high density and complex mixed mode circuits, for example SoC and MCM, come out with built-in boundary scan path as defined by IEEE 1149.4-1999 (Mixed Signal Test Bus Standard). Under this standardization, digital and analogue circuits are separately in testable modules, called Digital Boundary Module (DBM) and Analogue Boundary Module (ABM). All of these modules enclosed by internal and external test path, and external access by separate test pin. Actually, this standard is a complementary of IEEE 1149.1-1990, and gains extra features (such as ABM, the analogue test bus, an extended Test Access Port (ETAP) and controller, and various register for analogue test bus operation). Figure 1.1 shows the ABM for an analogue pin [1], and Figure 1.2 shows IEEE P1149.4 basic chip structure [2].

However, for those basic cores of mixed mode circuit, such as ADC, DAC, PLL and PGA, each realm has its own test technique differently implemented to and seldom compliance with 1149.4 cells. For example ADC, the conventional test technique used commonly at industry is Code Density test technique or simply Histogram test. Besides, there is still a lot of mixed-signal ASICs that do not facilitate with boundary scan due to trade off with area overhead.

Although analogue circuits such as filter and Op-Amp are widely used in the market and possessed with their own separated conventional functional test (specification-oriented testing), it is much more complex for test development with

the same implementation when the input and output share the same signal transmission in mixed mode environment.

In today's highly competitive semiconductor world, it is critical to reduce the actual test time on expensive automatic test equipment (ATE). Test time on highend mixed-signal tester costs about three to five cents per second [3]. Due to this, most commercial mixed mode ICs are tested by separate testers (digital tester and analogue tester). Mixed-signal tester generally comes in variety of architectures and test routines depend on vendors due to competitive advantage in the market. However, many of these testers consist of useful features that are common among each other.

Test simulation and defect-oriented testing are the two among other cost saving test methodology emerging trends for mixed-signal IC [4]. Test simulation promises the ability to simulate and debug the test program for tester and CUT developed by SPICE, VHDL or others software-modelling languages before actual silicon CUT is received. Defect-oriented testing is based on the mathematical analysis and software modelling of a circuit major failure mechanism that expose the failures in a limited set of measured parameters [4]. Both of these methods not only cut down the production test cost, but also accelerate the time to market for certain product.

Because of a lot of information can be abstracted directly from transient response of a CUT, test researchers work with transient response almost for a decade [5–10], they proposed that analogue and mixed mode CUTs could be unified test by Transient Response analysis with Pseudo Random Binary Sequence (PRBS). The output data are then analyzed and processed using mathematical calculation, such as Sample values, Rate of change, Auto-correlation and Cross-correlation and Response Digitisation. Further studies and researches on Transient Response analysis can be found in [11–22]. They proposed a DfT method - Interface Scan bus in CUT in order to increase fault coverage especially for particular fault. Besides, they categorized any detectable fault using generated Index Functionality from cross-correlation function for the CUT.

### **1.2 Problem Statement**

The number of mixed-signal circuit blocks of an IC is getting more and more. High-density CMOS transistors and limited pin count in mixed-signal chips become a test challenge to semiconductor industry. This will either increase time-to-market or face the risk of decrease quality during early production.

DfT and BisT approach are getting popular in many testing arena. However, with the extra pin overhead and add in extra register, for example DfT approach, cost development increase and die space become limited for application. Besides, for example in BisT approach, extra bus and block partitioning is needed. Then, analogue block and digital block have to be tested separately, and this includes also block interface testing. All of these increases production cost if production volume is in medium or lower scale. According to [23] and [24], the IC designs with a 200  $\mu$ m pad-pitch, pad limited layout and no boundary scan, adding IEEE P1149.4 test bus and controller will increase the cost by 15-30%, especially for low cost mixed mode ICs (< \$2) and low pin count (< 60 pins) ICs will increase the design cost dramatically.

In semiconductor industries, cost for a mixed-signal tester in the market is very expensive compared to digital tester or analogue tester alone. Test time increases if customer tests their product using both analogue and digital testers concurrently. Normally, this ATE is in giant size and not portable. This lead to profit losing if opponent can reach to market earlier. However, most IC industries are accommodated with digital tester. A defect-oriented testing technique, which facilitate the mixed-signal test with minimum modification or make use of digital tester, will be welcomed.

Therefore, the main questions being addressed in this research work are:

- a) Is it possible to integrate analogue and digital test as a single entity?

- b) Would digitally modelled analogue test help to ease mixed mode test?

### 1.3 Objective

The objectives of this project are:

- a) To facilitate mixed mode circuit test using digital modelling of analogue circuits.

- b) To study the feasibility of introducing digital modelling coupled with other test techniques to ease mixed mode test.

### 1.4 Goal

The goals of the project are:

- a) To investigate the effectiveness of digital modelling.

- b) To detect faults in mixed mode circuit in transient domain.

- c) To unify tests of mixed mode circuit.

### 1.5 Scope

The scope of the project is as listed below:

- a) To study the idea of digital modelling for analogue circuit.

- b) To study the idea of Power Supply Voltage Control test technique.

- c) To study and analyse characteristics of analogue active filter in discrete level.

- d) To test a second order Butterworth low pass filter based on experimental and simulation using digital modelling coupled with Power Supply Voltage Control test technique.

- e) To test a flash ADC using digital modelling and Power Supply Voltage Control test techniques, and compare the result to Code Density or Histogram test technique.

- f) To test a CMOS Op-Amp at transient level and AC Sweep by digital modelling coupled with Power Supply Voltage Control test technique.

### **1.6** Thesis Layout

Basically, this thesis can be divided into five chapters as stated below

- a) Introduction

- b) Literature review

- c) Research methodology

- d) Results and discussion

- e) Conclusion, future work and suggestion

The first chapter gives a brief description of the work and thesis. It includes explanation on mixed-signal background and motivation, as well as the project objectives, goals and scopes.

In the second chapter, the importance of mixed-signal testing and digital modelling test technique is described as well as the different between functional test and parametric test. Literature review on defect oriented tests and, some conventional analogue and mixed-signal parametric tests are also discussed in this chapter. Histogram test, which special to ADC- mixed mode circuit, is also briefly described in this section.

The methodology of the overall project is explained in detail in chapter three. The project approach as well as simulation using PSpice<sup>TM</sup> is described. Three CUTs as sample study are presented in this chapter. For discrete analogue filter test, explanation is given on how to set up the experimental work that include setting up the equipment, as well as simulation work. Simulation an Op-amp and 3-bit flash ADC are carried at CMOS transient level. Explanation on how to conduct the test in simulation is discussed.

In chapter four, result as well as discussion for the CUT are discussed and analysed. Selected transient and frequency response for discrete analogue filter will be looked in detail. For flash ADC, transient response and bias point analysis as well as Histogram test will be discussed. CMOS bias point for Op-amp as well as transient and frequency response will be collected and analyse. The bias point analysis is based as MATLAB<sup>TM</sup> test program. All the results, which digital model coupled with PSVC technique, are also collected and will be analysed in this chapter.

Finally, in the last chapter, Chapter five, a conclusion will be drawn along with the suggestion for future development in this subject.

### REFERENCES

- Mani Soma and IEEE P1149.4 WG. Review of IEEE P1149.4 Mixed-Signal\_Test Bus Standard. *Proceeding of the Northcon 96*. November 4-6, 1996. Seattle, WA, USA: IEEE. 1996. 320-323.

- Adam Cron. IEEE P1149.4 Almost a Standard. *Proceedings of the 1997 International Test Conference*, November 1-6, 1997. Washington, DC, USA: IEEE. 1997. 174-182.

- Ananta K.Majhi and Vishwani D. Agrawal. Mixed-Signal Test. Proceeding of the Eleventh International Conference on VLSI Design. January 4-7, 1998. Chennai, India: IEEE. 1998. 285 –288.

- 4. Mark Burns and Gordon W. Roberts. *An Introduction to Mixed-Signal IC Test and Measurement*. New York, U.S.: Oxford University Press, 2001.

- M.A. Al-Qutayri. System Level Testing of Analog Functions in a Mixed-Signal Circuit. Proceeding of the 7th IEEE International Conference on Electronics, Circuits and Systems, ICECS 2000. December 17-20, 2000. Jounieh, Lebanon: IEEE. 2000. 1026-1029.

- P.R. Shepherd, A. Bertin and M.A. Al-Qutayri. Implementation of the Transient Response Measurement of Mixed-Signal Circuits. *Proceeding of the third European Test Conference, ETC 93*. April 19-22, 1993. Rotterdam, Netherlands: IEEE, 1993. 66-73.

- M.A. Al-Qutayri and P.R. Shepherd. PRBS Testing of Analogue Circuits. *IEE Colloquium on Testing Mixed Signal Circuits*. May 15, 1992. London, UK: IEEE. 1992. 4/1 4/5.

- M.A. Al-Qutayri and P.R. Shepherd. Go/No-Go Testing of Analogue Macros. *IEE Proceedings-G of Circuits, Devices and Systems*. 1992. Volume (139): 534-540.

- P.R. Shepherd, M.A. Al-Qutayri and P.S.A. Evans. Testing Mixed Signal Integrated Circuits. *IEE Colloquium on Design and Test of Mixed Analogue and Digital Circuits*. November 15, 1990. London, UK: IEEE. 1990. 4/1-4/4.

- M. Al-Qutayri. Comparison of Voltage and Current Testing of Analogue and Mixed-Signal Circuits. *Sixth Annual IEEE International ASIC Conference and Exhibition*. September 27 - October 1, 1993. Rochester, NY, USA: IEEE. 1993. 156-159.

- D. Taylor and A. Platts. Transient Response Testing of Nonlinear Analogue Circuits Using Optimised Fault Sets. *IEE Proceedings-G of Circuits, Devices and Systems*. 2003. Volume (150): 104- 112.

- T.I. Pritchard, P.S.A. Evans and D. Taylor. Development of generic testing strategies for mixed-signal integrated circuits. Circuits, Devices and Systems, IEE Proceedings-G. 1992. Volume (139): 231-233.

- I.C. Butler, D. Taylor and P.S.A. Evans. Developments in Transient Response Analysis. *IEE Colloquium on Mixed Signal VLSI Test*. December 13, 1993. London, UK: IEEE. 1993. 5/1-5/6.

- D. Taylor, P.S.A. Evans and D. Marland. Functional Testing of Linear Circuits Using Transient Response Analysis. *Proceeding of the IEEE International Workshop on Defect and Fault Tolerance in VLSI Systems*. October 27-29, 1993. Venice, Italy: IEEE. 1993. 295-302.

- D. Taylor, P.S.A. Evans and T.I. Pritchard. Testing of Mixed-Signal Systems Using Dynamic Stimuli. *Electronics Letters*. 1993. Volume (29): 811-813.

- P.S.A. Evans, T.I. Pritchard and D. Taylor. Transient Response Tests for Mixed-Signal Analogue Circuit Cells. *IEE Colloquium on Testing Mixed Signal Circuits*. May 15, 1992. London, UK: IEEE. 1992. 1/1-1/3.

- A. Milne, D. Taylor, J. Saunders and A.D. Talbot. Generation of Optimised Fault Lists for Simulation of Analogue Circuits and Test Programs. *IEE Proceedings-G of Circuits, Devices and Systems*. 1999. Volume (146): 355-360.

- D. Taylor, P.S.A. Evans and T.I. Pritchard. Transient Response Testing of Mixed-Signal ASICs. *Fifth Annual IEEE International ASIC Conference and Exhibition*. September 21-25, 1992. Rochester, NY, USA: IEEE. 1992. 359-362.

- D. Taylor. Transient Response Testing of Analogue Components in Mixed-Signal Systems: A Review. *IEE Proceedings-G of Circuits, Devices and Systems*. 1998. Volume (145): 314-318.

- 20. A. Milne, D. Taylor and K. Naylor. Assessing and Comparing Fault Coverage When Testing Analogue Circuits. *IEE Proceedings-G of Circuits, Devices and Systems*. 1997. Volume (144): 1-4.

- 21. I.C. Butler, D. Taylor and T.I. Pritchard. Effects of Response Quantisation on the Accuracy of Transient Response Test Results. *IEE Proceedings-G of Circuits, Devices and Systems*. 1995. Volume (142): 334-338.

- R.J. Binns, D. Taylor and T.I. Pritchard. Testing Linear Macros in Mixed-Signal Systems Using Transient Response Testing and Dynamic Supply Current Monitoring. *Electronics Letters*. 1994. Volume (30): 1216-1217.

- 23. Stephen Sunter. The P1149.4 Mixed Signal Test Bus: Costs and Benefits.

Proceedings of the 1995 International Test Conference. October 21-25, 1995.

Washington, DC, USA: IEEE. 1995. 444-450.

- 24. S. K. Sunter. Cost/Benefits of The P1149.4 Mixed-Signal Test Bus. *IEE* Proceedings-G of Circuits, Devices and Systems. 1996. Volume (143), Issue (6): 393-398.

- 25. L. B. Michael and D. A. Vishwani. Essentials of Electronic Testing: For Digital, Memory and Mixed-signal VLSI Circuits. London, UK: Kluwer Academic Publishers. 2000.

- I.M. Bell, S.J. Spinks and J. Machado da Silva. Supply Current Test of Analogue and Mixed Signal Circuits. *IEE Proceedings-G of Circuits, Devices and Systems*. 1996. Volume (143), Issue (6): 399 407.

- B.S. Suparjo and B.R. Wilkins. Testing Analogue and Mixed-Signal Modules by Steady-State Response Monitoring. *IEE Colloquium on Testing-the Gordian Knot of VLSI Design*. May 28, 1993. London, UK: IEEE. 1993. 8/1 - 8/7.

- 28. K.R. Eckersall, P.L. Wrighton, I.M. Bell, B.R. Bannister and G.E. Taylor. Testing Mixed Signal Asics Through The Use Of Supply Current Monitoring. *Proceeding of the third European Test, ETC 93*. April 19-22, 1993. Rotterdam, Netherlands: IEEE. 1993. 385 – 391.

- I. Pecuh, M. Margala and V. Stopjakova. 1.5 Volts Iddq/Iddt Current Monitor. *Proceeding of the 1999 IEEE Canadian Conference on Electrical and Computer Engineering*. May 9-12, 1999. Edmonton, Alta, Canada: IEEE. 1999. 472-476.

- 30. A. Chehab, R. Makki, M. Spica and D. Wu. I<sub>DDT</sub> Test Methodologies for Very Deep Sub-Micron CMOS Circuits. *Proceeding of the first IEEE International Workshop on Electronic Design, Test and Applications*. January 29-31, 2002. Critchurch, New Zealand: IEEE. 2002. 403-407.

- 31. S. Dragic and M. Margala. A 1.2 V Built-In Architecture for High Frequency On-Line Iddq/Delta Iddq Test. *Proceeding of the IEEE Computer Society Annual Symposium on VLSI*. April 25-26, 2002. Pittsburgh, PA, USA: IEEE. 2002. 148-153.

- 32. A.K. B A'ain, A. H Bratt and A. P Dorey. On the Development of Power Supply Voltage Control Testing Technique for Analogue Circuits. *Proceeding of the fourth Asian Test Symposium*. November 23-24, 1995. Bangalore, India: IEEE. 1995. 133-139.

- 33. A. P. Dorey, P. J. Silvester and R. J. Ball. The Testing of Integrated Circuits Incorporating Analogue Sections. In: M. Miller, Ed. *Development in Integrated Circuit Testing*. UK: Academic Press Limited. 391–405; 1987.

- 34. P.N. Variyam, A. Chatterjeee and N. Nagi. Low–Cost And Efficient Digital-Compatible BIST for Analog and Circuits Using Pulse Response Sampling. *Proceeding of the 15th IEEE VLSI Test Symposium*. April 27- May 1, 1997. Monterey, CA, USA: IEEE. 1997. 261-266.

- 35. IEEE. *IEEE Standard for Terminology and Test Methods for Analog to Digital Converters*. New York, IEEE Standard 1241. 2001.

- Joey Doernberg and Hae-Seung Lee. Full Speed Testing of A/D Converters. Journal of Solid-State Circuits. 1984. Volume (19): 820-826.

- 37. M.F. Wagdy and S.S. Awad. Determine ADC Effective Number of Bits Via Histogram. *IEEE Transactions on Instrumentation and Measurement*. 1991. Volume (40), Issue (4): 770 – 772.

- 38. S. Max. IEEE Std. 1241: The Benefit and Risks of ADC Histogram Testing. Proceeding of the 18th IEEE Instrumentation and Measurement Technology Conference. May 21-23, 2001. Budapest, Hungary: IEEE. 2001. 704–709.

- 39. V. Liberali, F. Maloberti, and M. Stramesi. ADC Characterisation Using the Code Density Test Method with Deterministic Sampling. *Proceeding of the 2nd International Mixed Signal Testing Workshop*. May 15-18, 1996. Quebec City, Canada: IEEE. 1996. 113-118.

- 40. F. Adamo, F. Attivissimo, N. Giaquinto and M. Savino. FFT Test of A/D Converters to Determine the Integral Nonlinearity. *Proceeding of the 18th IEEE Instrumentation and Measurement Technology Conference*. 21-23 May, 2001. Budapest, Hungary: IEEE. 2001. 710 – 714.

- N. Nagi and J. A. Abraham. Test Trade-Offs for Different Dynamic Testing Techniques for Analog and Mixed-Signal Circuits. *Proceeding of the third International Conference on the Economics of Design, Test, and Manufacturing*. 16-17 May, 1994. Austin, TX, USA: IEEE. 1994. 142-146.

- 42. H.S. Mendonca, J.M. Silva and J.S. Matos. Differential Gain and Phase Testing Using Joint Time-Frequency Analysis. *Proceeding of the 18th IEEE Instrumentation and Measurement Technology Conference*. 21-23 May, 2001. Budapest, Hungary: IEEE. 2001. 2027–2030.

- 43. A. Gandelli, A. Brandolini and E. Carminati. A New Approach for A/D Converters Testing. *Proceeding of the 5th IEEE Instrumentation and Measurement Technology Conference*. April 20-22, 1988. San Diego, CA, USA: IEEE. 1988. 187–191.

- 44. T. Yamaguchi and M. Soma. Dynamic Testing of ADCs Using Wavelet Transforms. *Proceeding of the 1997 International Test Conference*. November 1-6, 1997. Washington, DC, USA: IEEE. 1997. 379–388.

- 45. Texas Instruments. *Understanding Data Converters*. USA: Texas Instruments Application Report. 1995.

- 46. R. Kondagunturi, E. Bradley, K. Maggard and C. Stroud. Benchmark Circuits for Analog and Mixed-Signal Testing. *Proceeding of the IEEE Southeastcon '99*. March 25-28, 1999. Lexington, KY, USA: IEEE. 1999. 217-220.

- 47. K. Saab, N.B. Hamida and B.Kaminska. Closing the Gap between Analog and Digital Testing. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*. 2001. Volume (20), Issue (2): 307-314.