# LOW POWER LOW-DROPOUT VOLTAGE REGULATOR (LDO) WITH FAST LOAD TRANSIENT RESPONSE

LIM LAY LENG

UNIVERSITI TEKNOLOGI MALAYSIA

# LOW POWER LOW-DROPOUT VOLTAGE REGULATOR (LDO) WITH FAST LOAD TRANSIENT RESPONSE

LIM LAY LENG

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical - Computer and Microelectronic System)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > JANUARY 2013

Specially dedicated to my family, lecturers, fellow friends and those who have guided and inspired me throughout my journey of education

### ACKNOWLEDGEMENT

I would like to take this opportunity to express my deepest gratitude to my project supervisor, Dr.Shaikh Nasir Bin Shaikh Husin for his encouragement, guidance and sharing of knowledge throughout the process of completing this project.

I would like to extend the appreciation to Intel Microelectronics (M) Sdn. Bhd. for funding my studies. I would like to thank my manager as well as my colleagues who had provided me with help and support throughout the duration of my studies.

Last but not least, I would like to thank my family for giving me the support and encouragement as well as for being understanding throughout my studies.

### ABSTRACT

With the recent explosion of devices driving "smart technologies" such as tablets, phones, all the portable and hand-held electronic devices such as cellular phones, PDA, MP3 players, GPS and other multi-media entertainments. The target for the portable battery operated product is towards reducing the number of battery cells, in order to decrease the cost and size. All these battery operated devices need power management circuits to work efficiently and extend the battery life, thus power regulation and power management have become one of the fastest growing sectors in the industry. The goal of this project is to design and implement a low power fully integrated CMOS low-dropout voltage regulator (LDO) based on quick response (QR) circuit to improve the load transient response. A 2.5V, 150mA with proposed high speed response circuit has been implemented in 0.25µm TSMC CMOS technology. The low-voltage operation ability, high current efficiency and low-voltage transient response performance can be achieved. With the small on-chip decoupling capacitor, the LDO with proposed QR circuit can achieve a fast load transient response with less transient overshoot or undershoot when instantaneous load fluctuation. By using the PMOS pass gate in the output stage we achieved a small regulator area and minimum dropout voltage for 100~150mA of output current. The proposed high speed response circuit included Memory circuit, PD\_Charge and PD\_Discharge circuit, Comparator and Vout\_Discharge circuit.

### ABSTRAK

Dengan perkembangan peranti-peranti baru yang digelar "teknologi pintar" seperti tablet, telefon, semaua peranti muday alih dan tangan elektronik seperti telefon bimbit, PDA, pemain MP3, GPS dan lain-lain hiburan multi-media. Sasaran untuk produk bateri mudah alih yang dikendalikan adalah tujuan untuk menuju ke arah mengurangkan bilangan sel-sel bateri, kos dan saiz. Semua alat-alat ini dikendalikan bateri perlu mengadakan pengurusan kuasa yang baik untuk memanjangkan hayat bateri. Pengurusan kuasa hayat bateri telah menjadi salah satu sektor yang paling pesat berkembang dalam industri. Objektif utama projek ini adalah untuk merekabentuk dan membina kuasa yang rendah bersepadu CMOS rendah keciciran pengatur voltan (LDO) berdasarkan maklum balas yang cepat (QR) litar untuk meningkatkan sambutan beban fana sepenuhnya. A 2.5V, 150mA dengan cadangan kelajuan tinggi respons litar telah dilaksanakan di 0.25µm TSMC CMOS teknologi. Keupayaan voltan rendah operasi, kecekapan tinggi semasa dan voltan rendah prestasi sambutan fana boleh dicapai.Dengan kapacitor yang kecil dalam kawasan silikon, LDO dengan litar QR yang dicadangkan boleh mencapai sambutan fana beban dengan cepat terlajak serta-merta apabila beban turun naik sertamerta.Dengan menggunakan pintu PMOS pas di peringkat keluaran kami mencapai kawasan pengatur kecil dan voltan keciciran minimum untuk 100 ~ 150mA output semasa.Litar yang digunakan dalam projeck ini termasuk litar Memori, PD\_Charge dan litar PD\_Discharge, Comparator dan litar Vout\_Discharge.

## TABLE OF CONTENTS

CHAPTER

TITLE

PAGE

| DECLARATION           | ii  |

|-----------------------|-----|

| DEDICATION            | iii |

| ACKNOWLEDGEMENT       | iv  |

| ABSTRACT              | v   |

| ABSTRAK               | vi  |

| TABLE OF CONTENTS     | vii |

| LIST OF TABLES        | Х   |

| LIST OF FIGURES       | xi  |

| LIST OF ABBREVIATIONS | xii |

| 1 | INTRODUCTION |                                  |   |

|---|--------------|----------------------------------|---|

|   | 1.1          | Background                       | 1 |

|   | 1.2          | Motivation and Problem Statement | 3 |

|   | 1.3          | Objectives                       | 4 |

|   | 1.4          | Scope of Work                    | 4 |

|   | 1.5          | Report Outline                   | 7 |

| 2 | LITI | LITERATURE REVIEW AND THEORY |              |         |            |          |    |

|---|------|------------------------------|--------------|---------|------------|----------|----|

|   | 2.1  | Litera                       | ature Review | ,       |            |          | 8  |

|   |      | 2.1.1                        | Low Dropo    | ut regu | lator topo | ology    | 9  |

|   | 2.2  | Previ                        | ous work on  | Linear  | Regulato   | r        | 11 |

|   |      | 2.2.1                        | Regulator    | with    | Source     | Follower | 12 |

vii

|   |               | 2.2.3            | Common-S                             | ource O  | Outp | out Stage |          | 12 |

|---|---------------|------------------|--------------------------------------|----------|------|-----------|----------|----|

|   |               | 2.2.4<br>Driver  | Regulator                            | with a   | a V  | Voltage   | Buffer   | 13 |

| 3 | MET           | HODOI            | LOGY                                 |          |      |           |          | 14 |

|   | 3.1           | Metho            | dology Ove                           | rview    |      |           |          | 14 |

|   | 3.2<br>L-edit | Propos<br>Tanner | sed Topolog<br>tools                 | y Desig  | gn ι | ising S-e | edit and | 16 |

| 4 | RESU          | JLT AN           | D DESIGN                             | VERI     | FIC  | CATION    | 1        | 19 |

|   | 4.1           | Compa            | arator Circui                        | it       |      |           |          | 19 |

|   | 4.2           | Memo             | ry Circuit                           |          |      |           |          | 22 |

|   | 4.3           | Charge           | e and Discha                         | arge Cir | rcui | t         |          | 24 |

|   | 4.4           | Post L           | ayout Verifi                         | cation   |      |           |          | 27 |

|   | 4.5           | Post L           | ayout Verifi                         | cation   |      |           |          | 27 |

|   |               | 4.5.1            | Comparator                           | Circuit  | t    |           |          | 29 |

|   |               | 4.5.2            | Memory Ci                            | rcuit    |      |           |          | 32 |

|   |               | 4.5.3            | PD_Charge                            | and Di   | sch  | arge Cire | cuit     | 34 |

|   |               | regulate         | Low Powe<br>or (LDO) v<br>se Circuit |          |      | -         | 0        | 36 |

|   | 4.6           | -                | arison of pre                        | evious V | Vs t | he Resul  | t        | 40 |

| 5 | CON           | CLUSI            | ON AND FU                            | UTURE    | E W  | ORK       |          | 41 |

|   | 5.1           | Conclu           | usion                                |          |      |           |          | 41 |

|   | 5.2           | Future           | Work                                 |          |      |           |          | 42 |

|   |               |                  |                                      |          |      |           |          |    |

## LIST OF TABLES

| TABLE NO. | TITLE | PAGE |

|-----------|-------|------|

|           |       |      |

|           |       |      |

4.1 The performance comparison with previous reported LDOs 40

## LIST OF FIGURES

| FIGURE NO | TITLE                                                           | PAGE |

|-----------|-----------------------------------------------------------------|------|

| 1.1       | Brief overview the steps of methodology and implementation plan | 5    |

| 2.1       | Basic Low Dropout Regulator Topology [3]                        | 10   |

| 2.2       | Linear Regulator [4]                                            | 11   |

|           | 2.2 (a) Source Follower                                         |      |

|           | 2.2 (b) A Replica Biased Source Follower                        |      |

|           | 2.3 (c) A Common Source Driver                                  |      |

|           | 2.4 (d) A Voltage Buffer Driver                                 |      |

| 3.1       | Completed Circuit of the Proposed Circuit [1]                   | 16   |

| 3.2       | (a) Completed Circuit of the High-speed Low-Dropout voltage     | 17   |

|           | regulator (HSLDO) with Fast Load Transient response using       |      |

|           | Tanner tools S-edit                                             |      |

| 3.2       | (b) Layout of the High-speed Low-Dropout voltage regulator      | 18   |

|           | (HSLDO) with Fast Load Transient response using Tanner tool     | s    |

|           | L-edit.                                                         |      |

| 4.1       | The Comparator used in the Proposed Circuit.                    | 20   |

| 4.2       | Comparator circuit in flatten mode layout                       | 20   |

| 4.3       | The memory circuit used in the Proposed Circuit                 | 23   |

| 4.4       | Layout of the memory Circuit                                    | 23   |

| 4.5       | (a) And (b) The charge and Discharge circuit used in proposed   | 25   |

|           | QR circuit.                                                     |      |

| 4.6       | (a) And (b) Layout of the charge and Discharge circuit used in  | 26   |

|           | proposed QR circuit                                             |      |

| 4.7       | Layout and Schematic netlists (LVS) is clean                    | 27   |

| 4.8  | DRC and Density are clean and meet TSMC 0.25 Micron         | 28 |

|------|-------------------------------------------------------------|----|

|      | Technology                                                  |    |

| 4.9  | (a) And (b) Comparator Circuit and Test-Bench.              | 30 |

| 4.10 | Post-layout waveform/output diagram for comparator circuit. | 31 |

| 4.11 | Memory circuit and Test-Bench                               | 33 |

| 4.12 | Post-layout waveform/output diagram for memory circuit      | 33 |

| 4.13 | PD_Charge and PD_Discharge circuit and Test-Bench           | 36 |

| 4.14 | Post-layout waveform/output diagram for PD_Charge and       | 36 |

|      | PD_Discharge circuit                                        |    |

| 4.15 | High-speed Low-Dropout voltage regulator (HSLDO) with Fast  | 38 |

|      | Load Transient response circuit and Test-Bench              |    |

| 4.16 | Load regulation Post-layout waveform/output diagram for     | 39 |

|      | HSLDO circuit                                               |    |

## LIST OF ABBREVIATIONS

| BJT    |   | Bipolar Junction Transistor                       |

|--------|---|---------------------------------------------------|

| CMP    | - | Comparator                                        |

| CMOS   |   | Complementary Metal Oxide Semiconductor           |

| HSLDO  |   | High-Speed Low Dropout Voltage Regulator          |

| LDO    | - | Low Dropout Voltage Regulator                     |

| MOS    |   | Metal Oxide Semiconductor                         |

| MOSFET |   | Metal Oxide Semiconductor Field Effect Transistor |

| PMOS   |   | P-type metal-oxide-semiconductor                  |

| QR     | - | Quick Response                                    |

| SPICE  | - | General-Purpose Circuit Simulation Program        |

| TST    | - | Test                                              |

| VO     |   | Output Voltage                                    |

| VI     |   | Input Voltage                                     |

### **CHAPTER 1**

#### **INTRODUCTION**

This project is about the low power low-dropout voltage regulator (LDO) with fast load transient response. The low-dropout voltage regulator is implemented on 0.25µm TSMC CMOS technology using Tanner tools S-edit and L-edit v13.00. This chapter gives an overview of the whole project, starts with a brief introduction to the background, followed by the problem statement, project objectives, scope of work and report outline.

## 1.1 Background

In the new technology era, the technology is developing and growing everyday. Due to their portability and easy of handling, battery operated product become important in the Electronics market including industrial and automotive applications. The increasing demand for the portable battery operated products has driven power supply design towards low voltage and low quiescent current flow, for example all the portable and hand-held electronic devices such as cellular phones, PDA, MP3 players, GPS and other multi-media entertainments is evolving day by day. The target for the portable battery operated product is towards reducing the number of battery cells, in order to decrease the cost and size. All these battery operated devices need power management circuits to work efficiently and extend the battery life, thus power regulation and power management have become one of the fastest growing sectors in the industry.

Due to high fast transient in battery voltage, all battery operated applications demand a stable output voltage with the changing loading. Thus LDO become important in electronic industrial market. Low power regulator can provide more battery life, which makes it even more attractive for the consumer market. The demand for the low-voltage, low drop-out (LDO) regulator is increasing. Meanwhile low-dropout regulator has demonstrated its low noise high-accuracy and fast-response performance, and thereby is widely utilized to power up advanced analogue and radio-frequency integrated circuits. LDO required having a small active area and a small dip at the output voltage in order to reduce the cost development. Low dropout voltage regulators (LDOs) with fast load transient response are a critical power management module in modem portable devices

Now a day, the LDO design has become more and more challenging. This is due to increasing demand of the high-performance LDOs with low-voltage fast-transient. In this project the methods to improve the classical LDO structure have been proposed. However, the structural limitation, which is the main obstacle to simultaneously achieving stability, high output-voltage accuracy and short response time, still cannot be overcome.

For the sake of good understanding theoretical knowledge, gaining hand-on experience for whole processes of analog IC custom design and academic interests, the LDO regulator has been chosen as the final project for the course of Analog and Mixed – Signal IC Design. The design is based on variety of the state-of-the-art published structures, and designed experimental result can achieve proposed specifications.

In this project, I will present the design method of low power LDO with high-speed load transient response. It can catch instantaneous load fluctuation even though from low-power operating condition. Furthermore, on matter how fast the load changes, safe mechanism is proposed to prevent the LDO from falling into unstable state.

## **1.2** Motivation and Problem Statement

Increasing demand for portable battery operated products has driven power supply design towards low voltage and fast load transient response. The demand for high speed and processing power with efficient power consumption of IC or SOC leads to much more complex design for power supply. Low-dropout (LDO) voltage regulator are one of the most critical power management modules, as its can provide low-noise and precision supply voltages with the load changes instantaneously from un-load to full loaded states.

The heart of this project is to design and implemented a low power fully integrated CMOS low-dropout voltage regulator (LDO) based on quick response (QR) circuit to improve the load transient response.

An almost infinite variety exists of LDO implementations but nearly all of them comprise a power transistor, feedback network and error amplifier where the complexity of the amplifier varies depending on the performance requirements. Those LDO circuits described in the literature are typically optimized for a specific application with either challenging requirements for dropout, efficiency, power supply rejection or transient response time.

However a great need exists also for regulators with high-speed load transient response but smallest possible die area and power consumption. Especially in highly complex system-on chip designs, a large number of those simple regulators are required along the interfaces of the various sub-circuits. In spite of this wide demand, no literature exists on how to implement and optimize such a low cost, low complexity regulator circuit. This project will address this by presenting a low power, low dropout (LDO) voltage regulator with the proposed quick response (QR) circuit to improve the load transient response to achieve low transient overshoot and undershoot when driving a large load current.

## 1.3 Objectives

The objective of this project is to design Low-Dropout Voltage (LDO) Regulator and its application. This chapter will present the design methodology of the low power LDO with high-speed load transient response. The main objective of this project would be to design and develop a low power fully CMOS LDO based on quick response (QR) circuit to improve the load transient response which can catch instantaneous load fluctuation from low-power operating condition. Furthermore, this proposed circuitry will provide a stable output voltage no matter how fast the load changes. In this work, a 2.5V, 150mA LDO with the proposed quick response circuit has been designed and implemented in a 0.25µm TSMC CMOS technology using Tanner tools S-Edit for schematic capture and Layout the schematic in L-Edit. In the project, several design options and architectures are explored for performance trade-off analysis.

#### **1.4** Scope of Work

The purpose of this project is to achieve a low dropout voltage, small output droop, fast load regulation and small silicon area LDO without utilizing a big capacitor. The proposed circuit consists of voltage reference circuit, Error amplifier circuit, memory circuit, comparator circuit, charge and discharge circuit, and pass element.

In major objective of this project is to study and understand Low-Dropout Voltage (LDO) Regulator and its application. There are few key considerations which would define the scope of work.

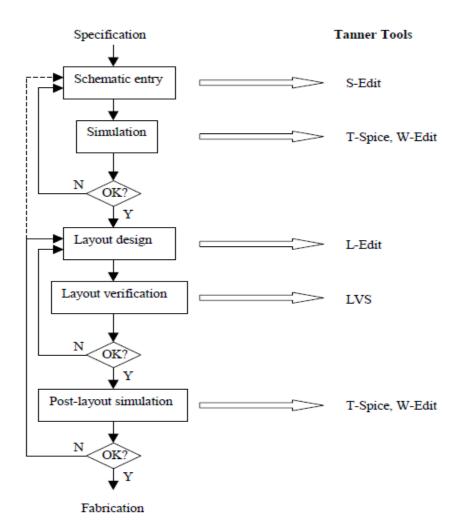

- a) Conceptual design on systems level (top down design of block diagrams).

- b) Breakdown of the system into smaller subsystems.

c) Schematic capture of the subsystem design, using devices realizable in the foundry technology, following a hierarchical approach (bottom up design).

d) Netlist extraction of the schematic design to generate a SPICE netlist.

e) SPICE simulation of the individual subsystems, applicable interfaces and then the system as a whole.

f) Creation of layout cells (hierarchical)

g) Layout-vs-schematic (LVS) check.

h) Post-layout simulation is then done by extracting device information from the layout file.

i) Assessment of the results, and further refinements if required.

a 2D convolution algorithm is

Figure 1.1 : Brief overview the steps of methodology and implementation plan.

## • Tanner Tools S-Edit v13.00

- > Tanner tools S-edit is used for schematic capture and netlist generation.

- > Spice uses **model definitions** to obtain information on device parameters.

- The module *schematic* designed will result in SPICE netlist which will be used in T-Spice in the design process.

## • T-Spice and W-Edit

- With a well created netlist, T-Spice serves as a very powerful SPICE engine. It is based on the industry standard Berkeley SPICE, with some added features.

- > The netlists created will now be simulated and the results will be viewed using W-Edit.

## • Tanner Tools L-Edit Pro v13.00

- L-Edit is a powerful layout program used to "paint" or define the devices as physical geometric features that is used to define the IC in terms of the foundry's process layers.

- > Running DRC on the drawn transistor to verify that all of the design rules are met.

- Layout-vs-schematic (LVS) is a layout versus schematic program, to compare a schematic netlist to a netlist extracted from a layout file.

- To test and verify the validity of the design, a layout extraction is necessary. This netlist can be used for post-layout simulations.

## **1.5 Report Outline**

The report is organized into 5 chapters namely the introduction, literature review and theory, methodology and design tool, 1D convolution modeling and design, 2D convolution modeling and design, design verification and performance analysis, and lastly the conclusion and future work.

Chapter 1 gives an overview of the project. It starts with a brief introduction to the background, followed by the problem statement, project objectives, scope of work and report outline.

Chapter 2 gives an overview on the prior work and literature review. Next, it introduces the theory of low dropout voltage regulator and the best topologies is chosen that offers low dropout voltage, small output droop, fast load regulation, and small silicon area in this project.

Chapter 3 describes the chosen circuitry and topologies and the project specification and methodology used.

Chapter 4 is the core chapter for this project report which discusses the architecture and design implementation. Simulation waveforms, testbench and design performance analysis are presented in this chapter as well. In this chapter, it will also show how the layout is done and post layout simulation results of the circuit.

Chapter 5 concludes what have the project achieve the fast load transient in terms of lowpower design with power supply only 2.5V and lastly of the chapter are proposes the future works for further improvement and enhancement of the project.

#### REFERENCES

1. Liang-GuoShen, Zu-ShuYan, Xing Zhang, Yuan-Fu Zhao and Ming Gao, "A Fast-Response Low-Dropout Regulator Based on Power-Efficient Low-Voltage Buffer," *IEEE J. Solid-State Circuits*, 2008

2. G. A. Rincon-Mora and P. E. Allen, "A low-voltage, low quiescent current, low drop-out regulator," *IEEE J. Solid-State Circuits*, vol. 33, no.1, pp. 36–44, Jan. 1998.

3. C. W. Lin and Y. J. Liu, "A power efficient and fast transient response low drop-out regulator in standard CMOS process " *VLSI Design, International Symposium on Automation and Test*, pp.1-4, April 2006

4. S. K. Hoon , S. Chen , F. Maloberti , J. Chen , B. Aravind, "A low noise, high power supply rejection low dropout regulator for wireless systemon-chip applications" *Proceedings of the IEEE 2005 Custom Integrated Circuits Conference*, pp. 759-762, Sept. 2005

5. P. Y. Kuo, D. Zhou, Z. M. Lin, "A low-dropout regulator with low ESR, low line regulation and high currency efficiency using low output resistance voltage buffer" *IEEE Conference on Electron Devices and Solid-State Circuits*, EDSSC 2007, pp.473 – 476, Dec. 2007

6. Socheat Heng, Weichun Tung, Cong-kha Pham "Low Power LDO with Fast Load Transient Response Based on Quick Response Circuit," *IEEE J. Solid-State Circuits*, 2008

7. MohammadAl-Shyoukh, Raul A. Perez and Hoi Lee, "ATransient-Enhanced 20LA-Quiescent 200mA-Load Low-Dropout Regulator With Buffer Impedance Attenuation," IEEE 2006 Custom Intergrated Circuits Conference (CICC), pp.1731-1734, Jul. 2006.

8. P. Hazucha, T. Karnik, B. A. Bloechel, C. Parsons, D. Finan and S.Borkar, "Areaefficient linear regulator with ultra-fast load regulation," IEEE J. Solid-State Circuits, Vol.40, No.4, pp.933-940, Apr. 2005.

9. Hoi Lee, T.Karnik, Philip K. T. Mok and Ka Nang Leung, "A Design of Low-Power Analog Drivers Based on Slew-Rate Enhancement Circuits for CMOS Low-Dropout Regulators," IEEE J. Solid-State Circuit, Vol.52, No.9, pp.563-567, Sep. 2005.

P.Hazucha, T.Karnik, A. Bloechel, C.Parsons, D.Finan, S.Borkar, "Area-Efficient Linear Regulator With Ultra-Fast Load Regulation," IEEE J.Solid-State Circuit, Vol.40, No.4, pp.933-940, Apr. 2005.

11. Socheat HENG and Cong-Kha PHAM "Quick Response Circuit for Low-Power LDO Voltage Regulators to improve Load Transient Response ," The University of Electro-Communications, Chofu-shi, 182-8585, Japan. IEEE J.Solid-State Circuit, 1-4244-0977-2/07/\$25.00\_c 2007 IEEE