# HARDWARE IMPLEMENTATION OF COORDINATE ROTATION DIGITAL COMPUTER IN FIELD PROGRAMMABLE GATE ARRAY

MOHD ILYAS SOBIRIN BIN MOHD SAZALI

UNIVERSITI TEKNOLOGI MALAYSIA

# HARDWARE IMPLEMENTATION OF COORDINATE ROTATION DIGITAL COMPUTER IN FIELD PROGRAMMABLE GATE ARRAY

# MOHD ILYAS SOBIRIN BIN MOHD SAZALI

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical – Microelectronic and Computer System)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > JANUARY 2012

To the next batch of students, Lillaahi Ta'ala.

#### ACKNOWLEDGEMENT

All Praise is to Allah through His Mercy and Favour the completion of this project among all good things is accomplished. In the past, people seek for respected scholars in the name of knowledge. Pursuing a Master's degree at Universiti Teknologi Malaysia (UTM) and in particular undertaking this project under the supervision of Professor Dr Mohamed Khalil Hani have been among the greatest decisions of my life. My sincere acknowledgement goes to my supervisor for his productive guidance and constructive criticisms in completing this project, as well as for his invaluable knowledge sharing, brilliant thoughts, wonderful experiences, wise words, and continuous support throughout my postgraduate time in UTM.

My gratitude is extended to Dr Muhammad Nadzir Marsono and Dr Usman Ullah Sheikh Izzat Ullah Sheikh for their valuable inputs as the panels during the project presentation. I am also grateful to my lab mates, Moganeshwaran, Annuar, Andy, Pei Chee, and Dr Rabia Bakhteri for their technical advices during the course of this project. Special thanks to Dr Hau Yuan Wen and Vishnu P. Nambiar for their technical tutorials that have aided to the success of this project, as well as to Sia, Shafiza, Sathy and Yee Hui for their assistance.

My genuine appreciation is dedicated to my parents, Dr Haji Mohd Sazali and Hajjah Shamsinar, along with my siblings for their incessant encouragement and prayers. Most of all, I am deeply indebted to my wife, Siti Nazmin, without whose kind understandings and tolerances neither this project nor my study would be successful. To our beloved sons, Iman Shahdan and Irshad Shahidin, for having to spend a part of their childhood time without their father, I owe them so much.

I also wish to express my gratitude to Universiti Sains Malaysia (USM) and Ministry of Higher Education (MoHE) for funding my study. Even though far from being perfect, it is hoped that this project report will be beneficial in one way or another to the reader.

#### ABSTRACT

Trigonometry is of great importance in mathematics as well as in physics, engineering, and chemistry. Astronomy, geography, navigation, study of optics and acoustics, oceanography, architecture, calculus, etc. are just several examples where trigonometry is significantly practiced. Historical figures like Pythagoras and Columbus used trigonometric tables in their careers. The birth of software has empowered relatively faster trigonometric functions performed by processors. In real-time applications though, such as trajectory calculations in military or space exploration, or in biomedical authentication system for fast access or rejection decision, trigonometric computation by software is a considerably time-consuming process. Coordinate Rotation Digital Computer (CORDIC) is an algorithm developed for hardware implementation as a real-time solution to trigonometric computation. This report presents a design approach to realize the CORDIC algorithm, prototyped as an embedded system in an Altera Field Programmable Gate Array (FPGA) development board running at 100 MHz clock frequency. The design flow applies the systematic Register Transfer Level (RTL) methodology, partitioning the design into a Datapath Unit (DU) for computation tasks, and a Control Unit (CU) for controlling the operation flow. Experimental results show that a high accuracy was obtained, with mean computation errors between 0.0014% and 0.0023% with respect to a software implementation on the same platform. The speed up in the execution time is about 89 times for the computation of cosine and sine functions, and 69 times for the arctangent. The work demonstrates the power of the CORDIC algorithm, and presents a methodology for an efficient complex hardware design.

#### ABSTRAK

Trigonometri amat penting dalam matematik serta fizik, kejuruteraan dan kimia. Astronomi, geografi, navigasi, kajian optik dan akustik, oseanografi, seni bina, kalkulus, dan lain-lain hanyalah beberapa contoh di mana trigonometri dipraktikkan dengan mendalam. Tokoh-tokoh sejarah seperti Pythagoras dan Columbus menggunakan jadual trigonometri dalam kerjaya mereka. Kelahiran perisian telah mempercepat pengiraan fungsi trigonometri oleh pemproses. Namun dalam aplikasi masa benar, seperti pengiraan trajektori dalam ketenteraan atau penerokaan angkasa lepas, atau dalam sistem pengesahan biometrik untuk akses atau penafian yang cepat, pengiraan trigonometri oleh perisian adalah suatu proses yang memakan masa terlalu lama. Komputer Putaran Koordinat Digital (CORDIC) adalah suatu algoritma dibangunkan khusus untuk implementasi perkakasan sebagai penyelesaian kepada pengiraan trigonometri dalam masa benar. Laporan ini membentangkan suatu pendekatan reka bentuk dalam merealisasikan algoritma CORDIC, diprototaipkan sebagai sebuah sistem terbenam dalam papan pembangunan Field Programmable Gate Array (FPGA) yang berfungsi pada frekuensi 100 MHz. Pendekatan ini menggunakan kaedah sistematik Register Transfer Level (RTL) dengan membahagikan reka bentuk kepada sebuah Unit Laluan Data (DU) untuk tugasan pengiraan, dan sebuah Unit Kawalan (CU) bagi mengawal perjalanan operasi. Keputusan uji kaji menunjukkan bahawa ketepatan tinggi telah diperolehi, dengan min ralat pengiraan antara 0.0014% dan 0.0023% berbanding dengan implementasi perisian dalam platform yang sama. Masa pelaksanaan adalah kira-kira 89 kali lebih pantas untuk pengiraan fungsi sinus dan kosinus, dan 69 kali untuk lengkuk tangen. Kerja ini menunjukkan kelebihan algoritma CORDIC, dan membentangkan suatu kaedah ke arah reka bentuk perkakasan kompleks yang efisien.

# **TABLE OF CONTENTS**

**CHAPTER**

1

1.8

# TITLE

PAGE

8

vii

| DECLARATION           | ii  |

|-----------------------|-----|

| DEDICATION            | iii |

| ACKNOWLEDGMENT        | iv  |

| ABSTRACT              | v   |

| ABSTRAK               | vi  |

| TABLE OF CONTENTS     | vii |

| LIST OF TABLES        | х   |

| LIST OF FIGURES       | xii |

| LIST OF ABBREVIATIONS | xiv |

| LIST OF APPENDICES    | xvi |

#### **INTRODUCTION** 1 Design Abstraction Level 1 1.1 Field Programmable Gate Array (FPGA) 1.2 4 Coordinate Rotation Digital Computer (CORDIC) 1.3 5 1.4 Problem Statement 6 Objectives 1.5 6 1.6 Scope of Work 7 **Project Contributions** 1.7 8

**Report Organization**

| BACH | KGROU  | JND AND LITERATURE REVIEW           | 10    |

|------|--------|-------------------------------------|-------|

| 2.1  | Overv  | iew of Iterative CORDIC Algorithm   | 10    |

| 2.2  | IEEE ′ | 754-2008 Floating-Point Format      | 12    |

| 2.3  | Previo | us Related Works on CORDIC          | 14    |

|      |        |                                     |       |

| MET  | HODO   | LOGY AND ALGORITHM DESCRIPTIO       | NS 18 |

| 3.1  | Projec | t Work Flow                         | 18    |

| 3.2  | Regist | er Transfer Level (RTL) Methodology | 21    |

|      | 3.2.1  | Algorithmic Modeling                | 22    |

|      | 3.2.2  | RTL Modeling                        | 26    |

|      | 3.2.3  | RTL Design of Datapath Unit (DU)    |       |

|      |        | and Control Unit (CU)               | 28    |

2

3

|       |                                   | 20 |

|-------|-----------------------------------|----|

| 3.2.4 | Design of Avalon Interface Module | 30 |

| 3.2.5 | Design of CORDIC Coprocessor      | 30 |

| 3.2.6 | Application Software Development  | 30 |

# 4 SYSTEM DESIGN AND IMPLEMENTATION –

| HAR | DWAR   | E AND INTERFACE                   | 32 |  |  |

|-----|--------|-----------------------------------|----|--|--|

| 4.1 | System | System Architecture32             |    |  |  |

| 4.2 | Hardv  | ware Design of CORDIC Coprocessor | 33 |  |  |

|     | 4.2.1  | CORDIC Core                       | 34 |  |  |

|     |        | 4.2.1.1 Design of DU              | 37 |  |  |

|     |        | 4.2.1.2 Design of CU              | 41 |  |  |

|     | 4.2.2  | Design of Avalon Interface Module | 42 |  |  |

|     |        |                                   |    |  |  |

| 5 | RESU | ULTS AND DISCUSSIONS    | 45 |

|---|------|-------------------------|----|

|   | 5.1  | Timing Simulation       | 45 |

|   | 5.2  | Physical Implementation | 59 |

|   | 5.3  | Accuracy                | 63 |

|   | 5.4  | Execution Time          | 64 |

|              | 5.5   | Resource Utilization   | 67       |

|--------------|-------|------------------------|----------|

| 6            | CON   | CLUSIONS               | 69       |

|              | 6.1   | Concluding Remarks     | 69       |

|              | 6.2   | Future Recommendations | 71       |

| REFERENC     | CES   |                        | 73       |

| Appendices A | 4 – D |                        | 75 – 107 |

ix

# LIST OF TABLES

TABLE NO.

# TITLE

# PAGE

| 1.1 | Design Abstraction Level                                                   | 3    |

|-----|----------------------------------------------------------------------------|------|

| 2.1 | Parameter Configurations and Outputs of Unified CORDIC Algorith            | m 12 |

| 2.2 | Summary of Literature Review                                               | 17   |

| 3.1 | Determination of s <sub>i</sub> for Trigonometric Function of CORDIC       |      |

|     | Algorithm                                                                  | 22   |

| 3.2 | RTL-CS Table derived from the ASM Chart                                    | 29   |

| 4.1 | Pre-calculated Constants Stored as a Look Up Table (LUT)                   | 38   |

| 4.2 | Addressing Mode of the Avalon Interface Module of the CORDIC               |      |

|     | Coprocessor                                                                | 43   |

| 5.1 | Simulation Table for Verification Purpose of                               |      |

|     | <pre>shiftfp_reg_Nbit_by_Mbit Module</pre>                                 | 49   |

| 5.2 | Simulation Table for Verification Purpose of <i>altfp_add_sub</i> Module   | 50   |

| 5.3 | Simulation Table for Verification Purpose of DU (Mode 1, cos/sin           |      |

|     | Function)                                                                  | 53   |

| 5.4 | Simulation Table for Verification Purpose of DU (Mode 2, tan <sup>-1</sup> |      |

|     | Function)                                                                  | 54   |

| 5.5 | Benchmarking of Accuracy with Previous Works                               | 64   |

| 5.6 | Execution Time (clock cycles, cc) of CORDIC Coprocessor against            | 2    |

|     | Library Functions                                                          | 65   |

| 5.7 | Speed up of CORDIC Coprocessor against C Library Functions                 | 65   |

| 5.8 | Benchmarking of Latency with Previous Works                                | 66   |

| 5.9  | Benchmarking of Execution Time (clock cycles, cc) with Previous |    |  |  |

|------|-----------------------------------------------------------------|----|--|--|

|      | Works                                                           | 67 |  |  |

| 5.10 | Benchmarking of Hardware Cost with Previous Works               | 68 |  |  |

# LIST OF FIGURES

FIGURE NO.

# TITLE

# PAGE

| 1.1 | The architecture of a Field Programmable Gate Array                | 4  |

|-----|--------------------------------------------------------------------|----|

| 3.1 | Project work flow                                                  | 20 |

| 3.2 | Applied RTL methodology                                            | 21 |

| 3.3 | A pseudo code representing Equation 3.1 and Table 3.1              | 23 |

| 3.4 | A single assignment form representing the CB in Figure 3.3         | 24 |

| 3.5 | A Data Flow Graph (DFG) resulted from Figure 3.4                   | 25 |

| 3.6 | Operators Scheduling and Resource Allocation diagram corresponding | g  |

|     | to the DFG                                                         | 26 |

| 3.7 | ASM Chart derived from Figure 3.3 and 3.4                          | 27 |

| 3.8 | A simplified flow chart of the developed application software      | 31 |

| 4.1 | Top-Level Block Diagram of the designed CORDIC module              | 33 |

| 4.2 | FBD of the CORDIC Coprocessor                                      | 34 |

| 4.3 | IOBD of the CORDIC Core                                            | 35 |

| 4.4 | FBD of the CORDIC Core                                             | 36 |

| 4.5 | FBD of the custom module to divide by powers-of-two                | 39 |

| 4.6 | FBD of the DU of the CORDIC Core                                   | 40 |

| 4.7 | FBD of the CU of the CORDIC Core                                   | 41 |

| 4.8 | IOBD of the Avalon Interface Module of the CORDIC Coprocessor      | 44 |

| 5.1 | Timing simulation of <i>regNbit</i> and <i>regNbit_v3</i> modules  | 45 |

| 5.2 | Timing simulation of register file LPM_RAM16x32                    | 46 |

| 5.3 | Timing simulation of <i>counter</i> and <i>counter_v2</i> modules  | 47 |

|     |                                                                    |    |

| 5.4  | Timing simulation of concatenate module, <i>concatenate32x</i>            | 47 |

|------|---------------------------------------------------------------------------|----|

| 5.5  | Timing simulation of subtract/add module, <i>sub_add_Nbit_by_Mbit</i>     | 48 |

| 5.6  | Timing simulation of powers-of-two divider,                               |    |

|      | shiftfp_reg_Nbit_by_Mbit                                                  | 48 |

| 5.7  | Timing simulation of floating point subtract/add unit of Library          |    |

|      | of Parameterized Module (LPM), altfp_add_sub                              | 49 |

| 5.8  | Timing simulation of 2-to-1 multiplexer (MUX), mux2to1                    | 50 |

| 5.9  | Timing simulation of DU (Mode 1, cos/sin function)                        | 51 |

| 5.10 | Timing simulation of DU (Mode 2, tan <sup>-1</sup> function)              | 52 |

| 5.11 | Timing simulation of CU                                                   | 55 |

| 5.12 | Timing simulation of CORDIC Core                                          | 56 |

| 5.13 | Timing simulation of the Avalon interface module                          | 57 |

| 5.14 | Timing simulation of CORDIC Coprocessor                                   | 58 |

| 5.15 | Physical implementation in Auto mode, Mode 1 (cos/sin function)           | 60 |

| 5.16 | Physical implementation in Auto mode, Mode 2 (tan <sup>-1</sup> function) | 61 |

| 5.17 | Physical implementation in User mode, Mode 1 (cos/sin function)           | 62 |

| 5.18 | Physical implementation in User mode, Mode 2 (tan <sup>-1</sup> function) | 63 |

|      |                                                                           |    |

# LIST OF ABBREVIATIONS

| ALU    | - | Arithmetic Logic Unit                   |

|--------|---|-----------------------------------------|

| ASIC   | - | Application Specific Integrated Circuit |

| ASM    | - | Algorithmic State Machine               |

| CB     | - | Computation Block                       |

| CC     | - | Clock Cycles                            |

| CLB    | - | Configurable Logic Block                |

| СМ     | - | Concatenate Module                      |

| CMOS   | - | Complementary MOSFET                    |

| CORDIC | - | Coordinate Rotation Digital Computer    |

| CPU    | - | Central Processing Unit                 |

| CS     | - | Chip Select                             |

| CU     | - | Control Unit                            |

| CV     | - | Control Vectors                         |

| DFG    | - | Data Flow Graph                         |

| DU     | - | Datapath Unit                           |

| FBD    | - | Functional Block Diagram                |

| FPGA   | - | Field Programmable Gate Array           |

| FSM    | - | Finite State Machine                    |

| HDL    | - | Hardware Description Language           |

| HLL    | - | High Level Programming Language         |

| HW     | - | Hardware                                |

| IC     | - | Integrated Circuit                      |

| IDE    | - | Integrated Design Environment           |

|        |   |                                         |

| IEEE   | - | Institute of Electrical and Electronics Engineers |

|--------|---|---------------------------------------------------|

| I/O    | - | Input Output                                      |

| IOB    | - | Input Output Block                                |

| IOBD   | - | Input Output Block Diagram                        |

| LCD    | - | Liquid Crystal Display                            |

| LE     | - | Logic Element                                     |

| LHS    | - | Left Hand Shift                                   |

| LPM    | - | Library of Parameterized Modules                  |

| LUT    | - | Look Up Table                                     |

| MCU    | - | Microcontroller Unit                              |

| MHz    | - | Mega Hertz                                        |

| MOSFET | - | Metal Oxide Semiconductor Field Effect Transistor |

| MSB    | - | Most Significant Bit                              |

| MUX    | - | Multiplexer                                       |

| NS     | - | Next State                                        |

| OS     | - | Operating System                                  |

| PCA    | - | Pipelined CORDIC Array                            |

| PFM    | - | Pipelined Filter Module                           |

| PLL    | - | Phase Locked Loop                                 |

| PS     | - | Present State                                     |

| RHS    | - | Right Hand Shift                                  |

| RTL    | - | Register Transfer Level                           |

| RTL-CS | - | RTL Control Sequence                              |

| SRAM   | - | Static Random Access Memory                       |

| SDRAM  | - | Synchronous Dynamic Random Access Memory          |

| SoC    | - | System-on-Chip                                    |

| SW     | - | Software                                          |

| USB    | - | Universal Serial Bus                              |

| UTM    | - | University of Technology Malaysia                 |

| VLSI   | - | Very Large Scale Integration                      |

| VHDL   | - | Very High Scale Integrated Circuit HDL            |

# LIST OF APPENDICES

| APPENDIX | TITLE                                  | PAGE |

|----------|----------------------------------------|------|

|          |                                        |      |

| А        | IEEE 754-2008 FLOATING-POINT TO BINARY |      |

|          | CONVERSION                             | 75   |

| В        | PHYSICAL IMPLEMENTATION TEST DATA      | 77   |

| С        | C HIGH LEVEL LANGUAGE SOURCE CODE      | 89   |

| D | VERILOG HARDWARE DESIGN LANGUAGE SOURCE CODE | 102 |

|---|----------------------------------------------|-----|

|   |                                              |     |

## **CHAPTER 1**

### **INTRODUCTION**

This project report documents a prototype hardware design of Coordinate Rotation Digital Computer (CORDIC) algorithm implemented as part of a System-on-Chip (SoC) implemented in Field Programmable Gate Array (FPGA). This chapter provides an overview of the design abstraction level and the FPGA technology, followed by an introduction to CORDIC, problem statement, project objectives, scope of work, project contribution, and finally the thesis organization.

## **1.1 Design Abstraction Level**

In order to handle different complexities in designing and fabricating an integrated circuit (IC), one of the techniques that electronic designers adopted is design abstraction [1]. A typical design abstraction can be arranged in a decreasing abstraction order as illustrated in Table 1.1, i.e. starting from the system or architectural level, moving down to the register transfer level (RTL), logic level, circuit level, layout level, device level, and finally the technology level. In a typical semiconductor company, each design level is managed by different engineering teams which may be situated at different parts of the world. At each level, the in-charged team models the design with a

black box view suitable for the complexity of that particular level, without having to worry for the internal details beyond their responsibilities or expertise. The information contained in the model is however adequate for the specialized team at the lower level of the design hierarchy.

One of the criteria which determine the design complexity is the number of gate counts. This project applies the RTL design level. The first reason is that the complexity of the proposed design is expected not to exceed 100,000 gates. For a larger system with a gate count of up to 500,000 gates, the system level would have been adopted. Else if the design is even simpler that it is expected to use 10,000 gates or lower, the logic or circuit level could be considered. Secondly, the RTL level is suitable for fast prototyping digital circuits into a Field Programmable Gate Array (FPGA) platform prior to transferring to more costly design stages. When a design has been successfully prototyped with relevant analysis carried out, then only it can be assigned to the succeeding levels, which are targeted for fabrication in an Application Specific IC (ASIC). As additional information, Table 1.1 also includes the courses offered at Masters Level by the body of knowledge, University of Technology Malaysia (UTM) under the Faculty of Electrical for each design abstraction level.

| Graphical view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Level         | Primitive   | Concerned       | Courses         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-----------------|-----------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | units       | parameters      | offered in      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |             |                 | UTM             |

| RAM ALU PLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | System /      | Behavioral  | Silicon area    | Adv. Computer   |

| ROM IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Architectural | modules     |                 | Architecture    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Level         |             |                 | (MEL1183)       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Register      | Functional  | Timing          | Adv. Digital    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transfer      | modules     |                 | System Design   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Level (RTL)   |             |                 | (MEL1173)       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Logic Level   | Gates, Bits | Delays          | Integrated      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |             | (propagation /  | Circuit Testing |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |             | transition)     | (MEL1133)       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Circuit Level | Transistors | Voltage,        | Analog CMOS     |

| │ <u>⟨</u> •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |             | Currents        | Design          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |             |                 | (MEL1193)       |

| Polysilicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Layout /      | Layout      | Topology,       | VLSI Circuits   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Physical      | layers      | Dimensions      | & Design        |

| Contact Metal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Level         |             |                 | (MEL1163)       |

| Source Gate Drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Device Level  | MOSFET      | Current-        | Nanoelectronic  |

| n-type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               | models      | Voltage         | Devices         |

| p-type SiO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |             | Characteristics | (MEL1113)       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Technology    | Process     | Impurity        | -               |

| C(s)<br>C(s) = C <sub>3</sub><br>Background<br>concentration, C <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Level         | models      | Profiles        |                 |

| A state of the sta |               |             |                 |                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |             |                 |                 |

Table 1.1 : Design Abstraction Level [1]

## **1.2** Field Programmable Gate Array (FPGA)

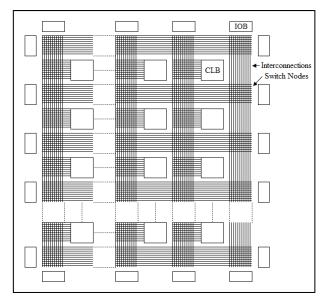

The Field Programmable Gate Array (FPGA) technology was pioneered by Xilinx in 1985 [2] as a prototyping platform for ICs. The function of an FPGA is userconfigurable, i.e. defined by a user's program rather than the device manufacturer. An FPGA in principle is made up of three major configurable elements which are Configurable Logic Blocks (CLBs) or also called as Logic Elements (LEs), Input/Output Blocks (IOBs), and interconnections as illustrated in Figure 1.1. The CLBs supply the functional element for constructing a user's logic. The interface between external package pins and internal signal lines is provided by the IOBs. The programmable interconnection links the CLBs and IOBs into the relevant network. Among programmable switching technologies driving an FPGA are SRAM-driven pass transistors [2, 3], anti-fuses [4], and EPROM-driven pass transistors [5, 6]. The first generation of FPGA implements 4-input Boolean functions and has a single storage element [2]. Successive generations enabled wider Boolean functions and incorporated additional storage elements, with more powerful and flexible CLBs, as well as improved IOBs and interconnections, allowing the FPGA technology to dramatically reduce the design turn-around time and manufacturing costs [7].

**Figure 1.1** The architecture of a Field Programmable Gate Array [8]

## **1.3** Coordinate Rotation Digital Computer (CORDIC)

Trigonometry is one of the fundamental mathematical functions that are vigorously taught at high schools. Students initially learnt to use trigonometry book which contains look-up tables for all trigonometric functions. This method was later replaced by scientific calculators which university students and engineers are obligatory to own one, be it in the physical form or in the software form. Most people have no knowledge or little appreciation on how these calculators are capable to compute such mathematical functions in just a blink of an eye, or to what extent can the accuracy be. The underlying secret of this capability may lie in an algorithm named as Coordinate Rotation Digital Computer (CORDIC).

CORDIC is an iterative algorithm involving only additions, subtractions, simple bit shifts, and constants look-ups, developed for fast computation of trigonometric functions such as cos, sin, and tan<sup>-1</sup>, their hyperbolic counterparts i.e. cosh, sinh, and tanh<sup>-1</sup>, as well as elementary operations like square root, division, and multiplication. Even though it is an approximation approach, the results of a CORDIC operator do not compromise accuracy, with a higher number of iterations provides a higher precision with respect to the actual calculation. The design of a CORDIC module involves division by powers of two, which can be exploited in a hardware implementation by applying right-hand shift (RHS) operation. In a compute-intensive application, CORDIC is one of the preferred alternatives to compute the previously mentioned mathematical functions.