### DESIGN OF AN OFDM TRANSMITTER AND RECEIVER USING FPGA

## LOO KAH CHENG

A project report submitted in partial fulfillment of the requirements for the award of the degree of Master of Engineering (Electrical - Electronics and Telecommunications)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > **NOVEMBER 2004**

#### ABSTRACT

Orthogonal Frequency Division Multiplexing (OFDM) is a multi carrier modulation technique. OFDM provides high bandwidth efficiency because the carriers are orthogonal to each others and multiple carriers share the data among themselves. The main advantage of this transmission technique is their robustness to channel fading in wireless communication environment. The main objective of this project is to design and implement a base band OFDM transmitter and receiver using FPGA. This project focuses on the core processing block of an OFDM system, which are the Fast Fourier Transform (FFT) block and the Inverse Fast Fourier Transform (IFFT). The 8 points IFFT / FFT decimation-in-frequency (DIF) with radix-2 algorithm is analyzed in detail to produce a solution that is suitable for FPGA implementation. The FPGA implementation of the project is performed using Very High Speed Integrated Circuit (VHSIC) Hardware Descriptive Language (VHDL). This performance of the coding is analyzed from the result of timing simulation using Altera Max Plus II.

#### ABSTRAK

Orthogonal Frequency Division Multiplexing (OFDM) atau Pemultipleksan Pembahagian Frekuensi Orthogonal adalah sejenis pemodulation pelbagai pembawa. OFDM menyediakan kecekapan lebar jalur yang lebih tinggi kerana pemodulatan pelbagai pembawa mempunyai ciri-ciri dimana setiap pembawa aalah ortoganal sesama sendiri dan data di kongsi bersama setiap pembawa. Kebaikan utama jenis pemodulatan pelbagai pembawa ini adalah ia tidak terjejas kepada channel fading dalam komunikasi tanpa wayar. Tujuan utama projek ini adalah merekebentuk dan melaksanakan satu penghantar (transmitter) and penerima (receiver) OFDM. menggunakan FPGA. Projek ini tertumpu kepada struktur pemprosesan utama dalam satu OFDM system, iaitu, blok Jelmaan Fourier Pantas atau Fast Fourier Transform (FFT) dan block Songsangan Jelmaan Fourier Pantas atau Inverse Fast Fourier Transform (IFFT). 8 sampel blok Jelmaan Fourier Pantas dan Blok Songsangan Jelmaan Fourier Pantas (IFFT) menggunakan pembahagian dalam frekuensi (DIF) dengan pembahagian 2 atau radix-2 dikaji dengan teliti untuk menghasilkan satu kaedah yang sesuai untuk pelaksanaan rekebentuk menggunakan FPGA. Komputer program ditulis menggunakan Very-High-Speed-Integrated-Circuit (VHSIC) Hardware Descriptive Language (VHDL). Kod ini diuji dan dianalisis dengan menggunakan keputusan daripada simulasi masa yang dilaksanakan dengan menggunakan Altera Max Plus II.

# **TABLE OF CONTENTS**

| DEDICATIONiiiACKNOWLEDGEMENTivABSTRACTvABSTRAKviTABLE OF CONTENTSviiLIST OF TABLExi | TITLE PAGE        | i   |

|-------------------------------------------------------------------------------------|-------------------|-----|

| ACKNOWLEDGEMENTivABSTRACTvABSTRAKviTABLE OF CONTENTSviiLIST OF TABLExi              | DECLARATION       | ii  |

| ABSTRACTvABSTRAKviTABLE OF CONTENTSviiLIST OF TABLExi                               | DEDICATION        | iii |

| ABSTRAKviTABLE OF CONTENTSviiLIST OF TABLExi                                        | ACKNOWLEDGEMENT   | iv  |

| TABLE OF CONTENTSviiLIST OF TABLExi                                                 | ABSTRACT          | V   |

| LIST OF TABLE xi                                                                    | ABSTRAK           | vi  |

|                                                                                     | TABLE OF CONTENTS | vii |

| LIST OF FIGURE xii                                                                  | LIST OF TABLE     | xi  |

|                                                                                     | LIST OF FIGURE    | xii |

| CHAPTER | TITLE                                      | PAGE |

|---------|--------------------------------------------|------|

| 1       | INTRODUCTION                               | 1    |

|         | 1.1 Digital Communication System Structure | 1    |

|         | 1.2 Project Background                     | 2    |

|         | 1.3 Project Objective                      | 5    |

|         | 1.4 Project Scope                          | 6    |

|         | 1.5 Project Outline                        | 6    |

|         |                                            |      |

# CHAPTER

| 2 | LITERATURE REVIEW                               | 8  |

|---|-------------------------------------------------|----|

|   | 2.1 Orthogonal Frequency Division Multiplexing  | 8  |

|   | 2.2 History of OFDM                             | 8  |

|   | 2.3 Basic Mathematical Principle of OFDM System | 10 |

|   | 2.4 Basic OFDM Implementation                   | 12 |

|   |                                                 |    |

| 2.5 OFDM Advantages and Disadvantages                   | 14 |

|---------------------------------------------------------|----|

| 2.6 OFDM Applications                                   | 15 |

| 2.7 VHSIC Hardware Description Language                 | 16 |

| 2.7.1 Synthesis Process in VHDL                         | 17 |

| 2.8 Field Programmable Gate Arrays (FPGA)               | 18 |

| 2.9 Fast Fourier Transform (FFT) / Inverse Fast Fourier | 20 |

| Transform                                               |    |

| 2.10 Decimation-in-frequency (DIF) FFT algorithm        | 22 |

# CHAPTER

| 1  |

|----|

| .) |

| •  |

| AND RECEIVER BASED ON 8-POINTS INVERSE FAST                |    |

|------------------------------------------------------------|----|

| FOURIER TRANSFORM (IFFT) AND FAST FOURIER                  |    |

| TRANSFORM (FFT)                                            | 26 |

| 3.1 Introduction                                           | 26 |

| 3.2 Algorithm of an 8-point Inverse Fast Fourier Transform |    |

| (IFFT)                                                     | 26 |

| 3.2.1 Structural method of an 8-point IFFT                 | 27 |

| 3.2.2 Direct Method of an 8-point IFFT                     | 28 |

| 3.3 Implementation of an 8-point IFFT processor            | 33 |

| 3.3.1 Pass module of 8 point IFFT processor                | 34 |

| 3.3.2 Path 0 and Path 4 module of an 8 point IFFT          |    |

| processor                                                  | 35 |

| 3.3.3 Path 1, Path 3, Path 5, Path 7 modules of an 8 point |    |

| IFFT processor                                             | 36 |

| 3.4 Algorithm of an 8-point Fast Fourier Transform (FFT)   | 38 |

# CHAPTER

| 4 | <b>RESUL OF VHDL SIMULATION</b> | 44 |

|---|---------------------------------|----|

|   | 4.1 Introduction                | 44 |

|   | 4.2 FFT Processor Result        | 44 |

| 4.2.1 Pass Module Simulation Result for FFT Processor     | 45 |

|-----------------------------------------------------------|----|

| 4.2.2 Path 0 and Path 4 Module Simulation Result for FFT  |    |

| Processor                                                 | 47 |

| 4.2.3 Path 2 and Path 6 Module Simulation Result for FFT  |    |

| Processor                                                 | 50 |

| 4.2.4 Path 1, Path 3, Path 5 and Path 7 Module Simulation |    |

| Result for FFT Processor                                  | 53 |

| 4.2.5 8-points FFT Simulation Result                      | 58 |

| 4.3 IFFT Processor Result                                 | 60 |

| 4.3.1 Pass Module Simulation Result for IFFT Processor    | 60 |

| 4.3.2 Path 0 and Path 4 Module Simulation Result for IFFT |    |

| Processor                                                 | 62 |

| 4.3.3 Path 2 and Path 6 Module Simulation Result for IFFT |    |

| Processor                                                 | 65 |

| 4.3.4 Path 1, Path 3, Path 5 and Path 7 Module Simulation |    |

| Result for IFFT Processor                                 | 68 |

| 4.3.5 8-points IFFT Simulation Result                     | 73 |

| 4.4 8-points FFT Simulation Result                        | 75 |

### CHAPTER

| 5       | CONCLUSTION          |                                   | 78  |

|---------|----------------------|-----------------------------------|-----|

|         | 5.1Conclustion       |                                   | 78  |

|         | 5.2 Challenges and   | Issues                            | 79  |

|         | 5.3 Suggestion for I | mprovement                        | 80  |

|         |                      |                                   |     |

| REFEREN | CE                   |                                   | 81  |

| APPENDI | X A FFT              | VHDL IMPLEMENTATION FLOW          | 83  |

|         | СН                   | ART                               |     |

| APPENDI | <b>X B</b> IFF       | <b>F VHDL IMPLEMENTATION FLOW</b> | 92  |

|         | СН                   | ART                               |     |

| APPENDI | XC VH                | DL SYNTHESIS CODE FOR FFT AND     | 101 |

ix

# IFFT PROCESSOR

# LIST OF TABLE

| TABLE | TITLE                                         | PAGE |

|-------|-----------------------------------------------|------|

| NO.   |                                               |      |

| 2.1   | Symmetry properties of $W_8^m$                | 22   |

| 2.2   | Computation of DFT in direct method and       | 25   |

|       | decimation-in-frequency algorithm             |      |

| 3.1   | Final equations for an 8-point IFFT processor | 32   |

| 3.2   | Symmetry properties of $W_8^{-m}$             | 39   |

| 3.3   | Final equations for an 8-point IFFT processor | 43   |

| 4.1   | Matlab FFT Simulation Output                  | 76   |

| 4.2   | Matlab IFFT Simulation Output                 | 77   |

## LIST OF FIGURES

| FIGURE | TITLE                                             | PAGE |

|--------|---------------------------------------------------|------|

| NO.    |                                                   |      |

| 1.1    | Digital Communication Systems                     | 1    |

| 1.2    | OFDM Transmitter                                  | 2    |

| 1.3    | OFDM Receiver                                     | 4    |

| 2.1    | OFDM Structure                                    | 10   |

| 2.2    | OFDM Transmission System                          | 12   |

| 2.3    | Synthesis Process in VHDL Environment             | 18   |

| 2.4    | 8-point DIF FFT flow chart                        | 24   |

| 3.1    | Single Butterfly Flow Chart in IFFT               | 27   |

| 3.2    | Structural Implementation of IFFT                 | 28   |

| 3.3    | Stage 1 Computation Flow Chart of an 8-point IFFT | 29   |

|        | Computation                                       |      |

| 3.4    | Stage 2 Computation Flow Chart of an 8-point IFFT | 30   |

|        | Computation                                       |      |

| 3.5    | Stage 3 Computation Flow Chart of an 8-point IFFT | 31   |

|        | Computation                                       |      |

| 3.6    | Block diagram of an 8 point IFFT processor        | 33   |

| 3.7    | 8-point FFT flow chart                            | 39   |

| 3.8    | Stage 1 Computation Flow Chart of an 8-point FFT  | 40   |

|        | Computation                                       |      |

| 3.9    | Stage 2 Computation Flow Chart of an 8-point FFT  | 41   |

|        | Computation                                       |      |

| 3.10   | Stage 3 computation flow chart of an 8-point IFFT | 42   |

xii

Computation

|      | 1                                                  |    |

|------|----------------------------------------------------|----|

| 4.1  | Pass Module Simulation Output for FFT Processor    | 46 |

| 4.2  | Path 0 Module Simulation Output for FFT Processor  | 48 |

| 4.3  | Path 4 Module Simulation Output for FFT Processor  | 49 |

| 4.4  | Path 2 Module Simulation Output for FFT Processor  | 51 |

| 4.5  | Path 6 Module Simulation Output for FFT Processor  | 52 |

| 4.6  | Path 1 Module Simulation Output for FFT Processor  | 54 |

| 4.7  | Path 3 Module Simulation Output for FFT Processor  | 55 |

| 4.8  | Path 5 Module Simulation Output for FFT Processor  | 56 |

| 4.9  | Path 7 Module Simulation Output for FFT Processor  | 57 |

| 4.10 | FFT Processor Output                               | 59 |

| 4.11 | Pass Module Simulation Output for IFFT Processor   | 61 |

| 4.12 | Path 0 Module Simulation Output for IFFT Processor | 63 |

| 4.13 | Path 4 Module Simulation Output for IFFT Processor | 64 |

| 4.14 | Path 2 Module Simulation Output for IFFT Processor | 66 |

| 4.15 | Path 6 Module Simulation Output for IFFT Processor | 67 |

| 4.16 | Path 1 Module Simulation Output for IFFT Processor | 69 |

| 4.17 | Path 3 Module Simulation Output for IFFT Processor | 70 |

| 4.18 | Path 5 Module Simulation Output for IFFT Processor | 71 |

| 4.19 | Path 7 Module Simulation Output for IFFT Processor | 72 |

| 4.20 | IFFT Processor Output                              | 74 |

|      |                                                    |    |

### **CHAPTER 1**

### **INTRODUCTION**

### 1.1 Digital Communication System Structure

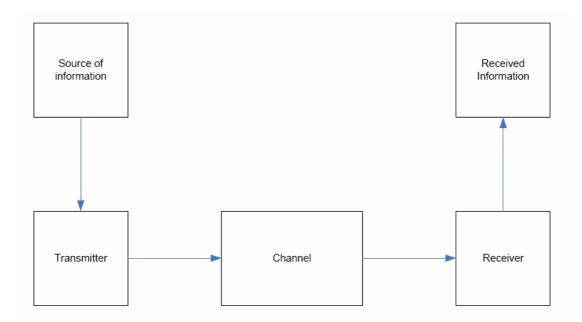

A digital communication system involves the transmission of information in digital form from one point to another point as shown in Figure 1.1

Figure 1.1 Digital Communication Systems

Regardless of the form of communication method, the three basic elements in a communication system consist of transmitter, channel and receiver.

The source of information is the messages that are to be transmitted to the other end in the receiver. A transmitter can consist of source encoder, channel encoder and modulation. Source encoder employed an efficient representation of the information such that resources can be conserved. A channel encoder may include error detection and correction code. The aim is to increase the redundancy in the data to improve the reliability of transmission. A modulation process convert the base band signal into band pass signal before transmission.

During transmission, the signal experiences impairment which attenuates the signals amplitude and distort signals phase. Also, the signals transmitting through a channel also impaired by noise, which is assumed to be Gaussian distributed component.

In the receiver end, the reversed order of the steps in the transmitter is performed. Ideally, the same information must be decoded in the receiving end.

#### 1.2 Project Background

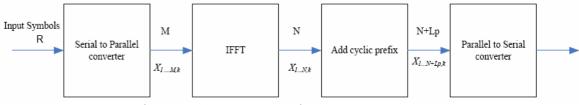

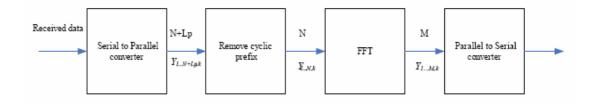

Figure 1.2 and 1.3 show a detailed OFDM transmitter and receiver communications system. In this project, the main focus is in the FFT and IFFT part of the OFDM system.

Figure 1.2 OFDM Transmitter

The input symbols are input into the transmitter in series at R symbols/second. These symbols pass through a serial to parallel converter and output data on M lines in parallel. The data rate on every M line is R/M symbols/second.

A symbol in this parallel stream of data is denoted as  $X_{i,k}$ . The index *i* refer to which sub channel the symbol belongs to, and *i* ranges from 1 to M. The *k* denotes the *k*-th collection of M symbols. The sub symbol collection from  $X_{I,k}$  to  $X_{M,k}$  makes up an OFDM symbol.

The M symbols are sent to an Inverse Fast Fourier Transform (IFFT) block that performs N-point IFFT operation. The IFFT transform a spectrum (amplitude and phase of each component) into a time domain signal. An IFFT converts a number of complex data points, of length that is power of 2, into the same number of points in time domain. Each data point in frequency spectrum used for an FFT or IFFT operation is called a bin. The output is N time-domain samples.

In order to preserve the sub-carrier orthogonality and the independence of subsequent OFDM symbols, a cyclic guard interval is introduced. Time and frequency synchronization can be established by means of cyclic extension in the prefix and the postfix period.

In this case, assumed a cyclic prefix of length  $L_p$  samples is pre-pended to the N samples to form a cyclically extended OFDM symbol. The cyclic prefix is simply the last  $L_p$  samples of the N inverse Fast Fourier Transform output samples.

For example, assumed N=4 and  $L_p=2$ . If the outputs of a 4 point inverse Fourier transform is [1 2 3 4]. The cyclic prefix will be [3 4]. The cyclically extended symbol would be [3 4 1 2 3 4]. Therefore, the length of the transmitted OFDM symbol is N+ $L_p$ .

Pre-pending the cyclic prefix aids in removing the effects of the channel at the receiver. ISI can occur when multi path channel cause delayed version of previous OFDM symbol to corrupt the current received symbol. If the value of  $L_p$  is greater than or equal to the size of the transmission channel, the ISI will only affect the cyclic prefix. The actual OFDM symbol will arrive unchanged.

The cyclic prefix makes the OFDM symbol appear periodic over the band of interest. The cyclically extended symbols are passed through a parallel-to-serial converter. They are transmitted in series across the channel response of the OFDM symbol with the frequency response of the channel.

Figure 1.3 OFDM Receiver

The received symbol is in time domain and it is distorted due to the effect of the channel. The received signal goes through a serial to parallel converter and cyclic prefix removal.

After the cyclic prefix removal, the signals are passed through an N-point fast Fourier transform to convert the signal to frequency domain. The output of the FFT is formed from the first M samples of the output.

#### **1.3 Project Objective**

The project aim is to design an OFDM transmitter and receiver using FPGA. The OFDM signal is generated by implementing the Inverse Fast Fourier Transform (IFFT) function at the transmitter. At the receiver end, the Fast Fourier Transform (FFT) is implemented.

The objective of this project is to use High-Speed-Integrated-Circuit (VHSIC) Hardware Description Language (VHDL) to produce VHDL code that carry out FFT and IFFT function.

The synthesis tool utilized is Altera Max Plus II to map the design to targeted device. Validation of the result and timing simulation are also using Altera Max Plus II.

The main challenge in this project is to derive the algorithm that is to be used in this project, for example, the algorithm for Fast Fourier Transform (FFT) and Inverse Fast Fourier Transform (IFFT). There are many algorithms available that can implement FFT / IFFT.

Second, the author finds it is very challenging on how software algorithm may be mapped to hardware logic. After the simulation result is verified, the process of converting the software statement into VHDL code is a major task. A variable may correspond to a wire or a register depending on its application and sometimes an operator can be mapped to hardware like adder, latches, multiplexers etc.

#### 1.4 Project Scope

The scope of the project is focuses on the design and implementation of OFDM base band transmitter and receiver. This project focuses on the core processing block of the transmitter and receiver, which is the IFFT and FFT block. This design computes 8-points IFFT and implements 8 inputs of real binary bits. The design will discuss on optimization of computational time by using the direct mathematical derivation method.

The implementation of the IFFT and FFT block is using VHDL code. The computation is done in separate sub modules for each output. Each sub module computes a single output path. The combination of eight sub modules produces the complete design of 8 points IFFT and FFT.

### **1.5 Project Outline**

The project is organized into five chapters, namely introduction, literature review, implementation of an OFDM transmitter and receiver based on 8- points inverse Fast Fourier Transform and Fast Fourier Transform, result of VHDL simulation and Conclusion.

Chapter 1 discusses the general idea of the project which cover the overview, project objective, project background and scope of the project.

Chapter 2 shows the literature review of the OFDM system. The history and principle of the OFDM system, Fast Fourier Transform introduction and VHDL programming basic introduction is elaborate in this chapter.

Chapter 3 derives the Fast Fourier Transform and Inverse Fourier Transform algorithm using direct mathematical method. The equations are optimized for digital implementation.

Chapter 4 shows the VHDL simulation output. The results are presented in their sub-modules and then all the modules are combined to give the final output. Then, the VHDL output are compared with Matlab simulation output.

Chapter 5 consists of conclusion, problems encountered in completing this project and suggestion to further improve this project.

#### REFERENCE

- 1. Dusan Matiae, "OFDM as a possible modulation technique for multimedia applications in the range of mm waves," TUD-TVS, 30-10-1998.

- R. W. Chang, "Synthesis of Bandlimited Orthogonal Signals for Multichannel Data Transmission," Bell System Tech. J., pp. 1775-1796, Dec, 1966.

- 3. B. R. Saltzberg, "Performance of an Efficient Parallel Data Transmission Sytem," IEEE Trans. Comm., pp 805-811, Dec, 1967.

- 4. S. B. Weinstein and P.M. Ebert, "Data transmission by frequency division multiplexing using the discrete fourier transform," IEEE Transactions on Communication Technology", vol. COM-19, pp. 628-634, October 1971.

- 5. A. Peled and A. Ruiz, "Frequency Domain Data Transmission using Reduced Computational Complexity Alogrithms," In Proc. IEEE Int. Conf. Acoust., Speech, Signal Processing, pp 964-967, Denver, CO, 1980.

- L. Hanzo, M. Munster, B.J. Choi and T. Keller, "OFDM and MC-CDMA for Broadband Multi-User Communications, WLANs and Broadcasting," IEEE Press, Wiley.

- White paper, "Orthogonal Frequency Division Multiplexing (OFDM) Explained", Magis Networks, Inc. 2001

- 8. Eric Lawrey, "The suitability of OFDM as a modulation technique for wireless telecommunications, with a CDMA comparison", 1997, BSEE thesis.

- 9. Erich Cosby, "Orthogonal Frequency Division Multiplexing (OFDM): Tutorial and Analysis", 11-12-2001, Virginia Tech. Northern Virginia Center.

- 10. J. Bhasker, "A VHDL Synthesis Primer", 2<sup>nd</sup> Edition, Star Galaxy Publishing, 1998.

- Yu-Chin Hsu, Kevin F. Tsai, Jessie T. Liu & Eric S. Lin, "VHDL Modeling for Digital Design Synthesis." Kluwer Academic Publishing, 1995.

- 12. Jeffrey H. Reed, "Software Radio A Modern Approach to Radio Engineering", Prentice Hall, 2002

- 13. Mark Zwolinski, "Digital System Design with VHDL", Prentice Hall, 2000