## Self-Synchronization Scheme for OTDM Packet Signal Using a Symmetric Mach Zehnder Switch

Razali Ngah Wireless Communication Centre Faculty of Electrical Engineering Universiti Teknologi Malaysia Email: razalin@fke.utm.my

Abstract— The key issue in being able to implement efficient all-optical switching/routing is the ability to carry out synchronization between the switching node and the incoming packets. In this paper we report the simulation results of all optical clock recovery scheme for packet-level self-synchronization using a single symmetric Mach-Zehnder (SMZ) switch. Simulation results demonstrate that clock recovery is successfully carried out employing SMZ switches with high on-off ratio and low crosstalk. On-off ratio for different packets separation has been carried out, showing that long packets separation results in a higher on-off ratio.

*Index Terms*— Self-synchronization, all-optical switch, on-off ratio, crosstalk

### 1. Introduction

All optical switches based on the cross-phase (XPM) in conjunction with modulation interferometric configurations such as Mach-Zehnder interferometers (MZIs), terahertz optical asymmetric demultiplexers (TOADs) and ultrafast nonlinear interferometers (UNIs) have been extensively investigated for the implementation of ultra fast optical networks, particularly for selfsyncronization schemes [1]. Self-synchronization schemes are attractive for optical packet networks due to reduced hardware costs and control complexity [2]. These schemes require only a single signal in the first bit position of the packet, corresponding to the clock signal; that it is extracted for synchronization purposes. The clock signal could be at different wavelengths [3]. polarizations [4], bit rates [5], or intensities [6] in comparison to the remaining signals within the packets. Normally a packet is composed of the clock signal, the address bits and the payloads. In the co-propagating geometry of the SMZ, normally the control signals have a different wavelength to that of the data signals [7]. However, these schemes have a number of drawbacks such as: generation and transmission of packets is significantly complicated, and the clock signals may lose their timing relationship to other signals in the same packet after propagating a long distance [8]. To avoid these problems, here we have proposed a packet format where the clock, the address and the payloads all have the same intensity, polarization, width and wavelength.

Zabih Ghassemlooy Optical Communication Research Lab., School of Engineering & Technology, Northumbria University, UK. Email: <u>fary.ghassemlooy@unn.ac.uk</u>

In this paper, we simulate all-optical clock recovery using a single SMZ switch with an optical feedback. Since the same intensity, polarization, width and wavelength have been used for the entire packet including the clock pulse; there is no requirement for additional filter and laser in the optical feedback loop.

### 2. Operation Principles

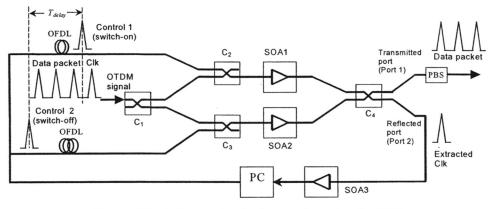

The proposed clock and data extraction modules is shown in Figure 1, which is composed of optical fibre delay lines (OFDLs), an SMZ in combination with an optical feedback, a polarization controller (PC) and a polarization beam splitter (PBS). The clock signal positioned at the head of incoming OTDM packet enters the SMZ module via an input 3-dB coupler C<sub>1</sub> splits into two components, with a  $\pi/2$  phase shift due to the input coupler, propagating through physically separate arms of the interferometer. In the absence of the control signal, the two clock components experience the same relative phase shift during propagation, and recombine at the output 3-dB coupler C<sub>4</sub> before re-emerging from the reflected output port 2. The reflected clock signal is amplified by semiconductor optical amplifier (SOA3) and passed through a PC before being fed back via an OFDL into the control ports of the interferometer, orthogonally polarized to the data packet. OFDLs are used to create the necessary time delay  $T_{delay}$  between the two input control signals. The function of the control signals is to change the optical properties of the SOAs, thus introducing a phase shift that results in a switching window for extraction of the data packet (address and payload bits) at the transmitted output port 1 of the interferometer. At the output port 1 of the SMZ a polarization beam splitter has been used to separate the outgoing data and the control signals.

With this approach, simpler router synchronization is achieved by inserting only a single clock signal, which has the same width, wavelength, polarisation and amplitude as the signals in the payload, within the OTDM packets.

# 3.0 Simulation of Clock Recovery Using VPI and Results

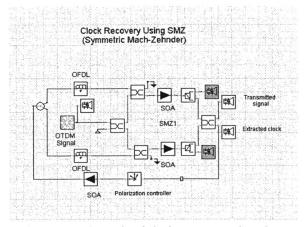

The proposed SMZ clock recovery is simulated using the Virtual Photonic (VPI) simulation software

as shown in Figure 2. All the relevant simulation parameters are for real practical devices reported in [9] and listed in Table 1.

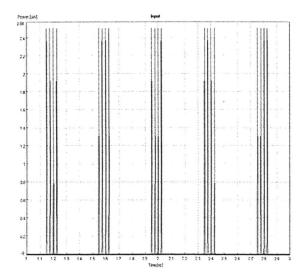

Figure 3 shows an OTDM packet train with packet length of ~ 25 ps which composed of a clock signal (first bit), followed by one bit of address and two bits of payload. All the signals have same amplitude, polarization and wavelength. The aggregate bit rate is 40 Gbit/s, and each bit is represented by a very-low duty cycle signal with a full-width at half-maximum (FWHM) of 2 ps and packet separation time of 375 ps. Both the data and control signal are at the same wavelength of 1550 nm. As described in the previous section, the first bit in each OTDM packet signal is extracted for synchronization.

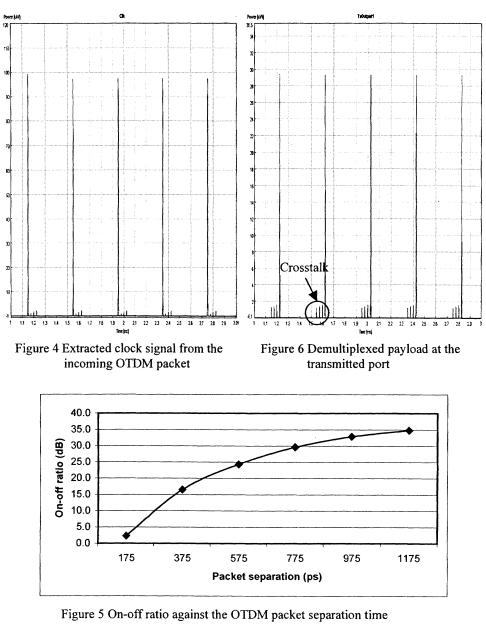

Figure 4 shows the extracted clock signals from OTDM packet signal. Notice that the presence of residual crosstalk which is ~20 dB lower than the extracted clock signal. As mentioned before, the emerged signal from the reflected output port of the SMZ is independent of the  $\pi$ -phase shift of the SOA, however due to reduced spacing between the control pulses and imperfect switching extinction ratio there is an increase in the residual crosstalk compared to long packet separation. For the same reason, lower on-off ratio of 17 dB is achieved for packets with short separation time (in this case 375 ps), which is smaller when compared with long packet separation as shown in Figure 5. Figure 5 shows the on-off ratio for different packet separations. As can be seen the on-off ratio exponentially increases as the packet separation increases reaching 35 dB at packet separation of 1175 ps.

The train of the extracted clock signal (Figure 4) is fed to the SMZ switch via a splitter and OFDLs. OFDLs are used for time synchronization between the control and data signals.  $T_{delay}$  of 30 ps is used to create a switching window with FWHM of 30 ps for extraction of 10 Gbit/s, the demultiplexed payload from the remaining data packet at the transmitted port as shown in Figure 6. As can be seen from the figure, there is some crosstalk, which is due to imperfect switching extinction ratio.

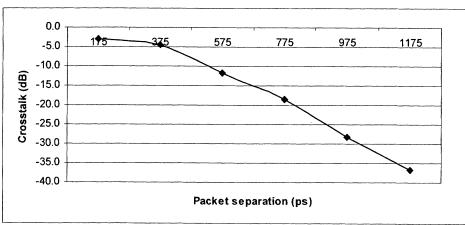

Figure 7 shows the crosstalk against the packet separation. The crosstalk is defined as the ratio of the power of non-target channels to the power of a target channel. The figure shows that the crosstalk decreases with the increasing packet separation, reaching a - 37 dB at packet separation time of ~ 1200 ps, where the on-off ratio is 35 dB.

### 4.0 Conclusion

We have proposed a self-synchronization scheme for OTDM packet networks using a single alloptical SMZ switch with a simple optical feedback loop. In this scheme only a single clock signal with the same width, wavelength, polarization and amplitude as that of the payload within the packet is required. Simulation results showed that on-off ratio of extracted clock is highly depended on the separation time of the OTDM packets. Higher packet separation time resulted in higher on-off ratio. However, higher packet separation time in turn meant reduced throughput. Thus there is trade off between the on-off ratio and throughput.

### REFERENCES

[1] J. M. Tang, P. S. Spenser, P. Rees, and K. A. Shore, "Ultrafast optical packet switching using low optical pulse energies in a self-synchronization scheme," *J. Lightwave Technol.*, vol. 18, pp. 1757-1764, 2000.

[2] X. C. Yuan, V. O. K. Li, C. Y. Li, and P. K. A. Wai, "A novel self-routing address scheme for alloptical packet switched networks with arbitrary topologies," *J. Lightwave Technol.*, vol. 21, pp. 329-339, 2003.

[3] Y. Shimazu, M. Tsukada, "Ultrafast photonic ATM switch with output buffers," J. Lightwave Technol., vol. 10, pp. 265-272, 1992.

[4] I. Glesk, K. I. Kang, and P. R. Prucnal, "Demonstration of ultrafast all-optical packet routing," *Electron. Lett.*, vol. 33, pp. 794-795, 1997.

[5] D. Cotter, J. K. Lucek, M. Shabeer, K. Smith, D. C. Rogers, D. Nesset, and P. Cunning, "Self-routing of 100 Gbit/s packets using 6 bit 'keyword' address recognition," *Electron. Lett.*, vol. 31, pp. 2201-2202, 1995.

[6] R. A. Barry, V. W. S. Chan, K. L. Hall, E. S. Kintzer, J. D. Moores, K. A. Rauschenbach, E. A. Swanson, L. E. Adams, C. R. Doerr, S. G. Finn, H. A. Hauss, E. P. Ippen, W. S. Wong, and M. Haner, "All-optical network consortium-ultrafast TDM networks," *IEEE J. Select. Areas Commun.*, vol. 14, pp. 999-1013, 1996.

[7] S. Nakamura, Y. Ueno, K. Tajima, J. Sasaki, T. Sugimoto, 'T. Kato, T. Shimoda, M. Itoh, H. Hatakeyama, T. Tamanuki, and T. Sasaki, "Demultiplexing of 168-Gb/s data pulses with a hybrid-integrated symmetric Mach-Zehnder all-optic switch," *IEEE Photon. Technol. Lett.*, vol. 12, pp. 425-427, 2000.

[8] T. J. Xia, Y. H. Kao, Y. Liang, J. W. Lou, K. H. Ahn, O. Boyraz, G. A. Nowak, A. A. Said, and M. N. Islam, "Novel self-synchronization scheme for high-speed packet TDM networks," *IEEE Photon. Technol. Lett.*, vol. 11, pp. 269-271, 1999.

[9] L. Gillner, "Modulation properties of near travelling-wave semiconductor laser amplifier," *IEE Proceeding-J*, vol. 139, pp. 331-338, 1992.

Figure 1 Block diagram for clock extraction using the SMZ

Figure 2 A schematic of clock recovery using the VPI software

Figure 3 OTDM packet stream with 375 ps packet separation

**Parameters** Values Data and control signals 10 Gbit/s Data bit rate per channel Clock signal FWHM width 2 ps Address bit FWHM width 2 ps Data bit FWHM width 2 ps Data signal peak power 2.5 µW Control signal peak power 1.2 W SOA Injection current 0.15 A 0.3 mm Length 3.0x10<sup>-13</sup>m<sup>2</sup> Active area 1.0x10<sup>24</sup>m<sup>-3</sup> Transparent carrier density Confinement factor 0.15 2.78x10<sup>20</sup>m<sup>2</sup> Differential gain 4.0 Linewidth enhancement Recombination coeff. A 1.43x10<sup>8</sup> 1/s 1.0x10<sup>-16</sup>m<sup>3</sup>/s Recombination coeff. B 3.0x10<sup>-41</sup>m<sup>6</sup>/s Recombination coeff. C 2.8x10<sup>24</sup>m<sup>-3</sup> Initial carrier density

Table 1 Simulation parameters for clock recovery

Figure 7 Crosstalk against the OTDM packet separation time