# IMPLEMENTATION OF RECONFIGURABLE VITERBI DECODERS IN HARDWARE

### MOHAMED FARID BIN NOOR BATCHA

A thesis submitted in fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical)

Faculty of Electrical Engineering Universiti Teknologi Malaysia

#### **ACKNOWLEDGEMENT**

This thesis is the result of a research project as partial fulfillment of the requirements for a Masters degree in Electrical Engineering at University Technology Malaysia. The research project has been carried out in MIMOS Berhad as part of the research work on wireless mobile communication.

I would like to express my appreciation and gratitude to my supervisor, Assoc. Prof. Dr. Ahmad Zuri Sha'ameri, for his guidance, support, and patience during my graduate education. He has been an invaluable source of technical knowledge and has certainly helped inspire many of the ideas expressed in this thesis. I had received great benefits from the courses that he has taught such as Random Process, Advanced Digital Communication and also Digital Signal.

I would like to thank MIMOS Berhad for sponsoring the Masters Program, and help me achieve my goals in life.

Last but not the least I want to thank my family and friends who has given me positive encouragement in fulfilling this journey of life.

#### **ABSTRACT**

Channel coders are widely used in digital transmissions where data can be corrupted due to interference. They are used in a large proportion of digital transmission and digital recording systems, including digital mobile telephony and digital television broadcast, compact disc, and magnetic disk reading. Viterbi decoder is one of the most widely used channel decoders that are used for decoding data that are encoded using convolutional forward error correction codes. This research investigates an adaptive channel coder that is able to switch between few configurations depending on the channel conditions. Channel codes consist of encoders and decoders, and since encoders are rather simple, the main focus of the research is towards the decoders. The research explores into an optimized shared hardware structure between various Viterbi decoders especially of those being used in current technologies such as General Packet Radio Service (GPRS), Enhanced Data rates for GSM Evolution (EDGE), and Worldwide Interoperability for Microwave Access (Wimax). The research looks into optimized methods of memory management and is also aimed for high throughput to be used for high speed applications that are a trend for new and upcoming technologies. Initially the performance of various configuration of Viterbi decoder with respect to different channel conditions was looked into to select few suitable Viterbi decoders to be implemented on Field Programmable Gate Array (FPGA). The final implementation on FPGA combines three Viterbi decoders into a single core. The gain in area of the three Viterbi existing separately when compared to the joint hardware is about 15 %, with no loss in processing speed and throughput. The latency is measured to be a minimum amount with respect to the data size. For a packet size of 100 information bits and code rate r=1/2 the latency would be 162 cycles. The main idea in having a shared hardware structure was to basically map the trellis structure of the smaller Viterbi configuration over the larger one, thereby not taking any extra hardware of its own. The significance would be a reduced complexity of various Viterbi decoders existing on a single shared hardware.

#### **ABSTRAK**

Kod saluran digunakan dengan meluas di dalam transmisi digital di mana kerosakan maklumat boleh terjadi disebabkan gangguan bisingan. Teknik ini digunakan dengan banyaknya di dalam transmisi digital dan sistem rakaman digital, termasuk telefon bimbit dan siaran televisyen digital, cakera padat dan rakaman cakera bermagnet. Penyahkod Viterbi adalah salah satu penyahkod saluran yang digunakan dengan meluas untuk menyahkod maklumat yang telah dikod menggunakan kod pembetulan kesalahan ke hadapan konvolusi. Penyelidikan ini menyiasat kod saluran ubahsuai yang boleh bertukar konfigurasi bergantung kepada keadaan saluran isyarat. Kod saluran terdiri daripada pengekod dan penyahkod, dan sememangnya pengekod adalah mudah, maka fokus utama penyelidikan ini adalah ke arah penyahkod. Kajian ini juga menyelidik struktur perkakasan perkongsian optimum antara pelbagai penyahkod Viterbi terutamanya yang digunakan di dalam teknologi terkini seperti General Packet Radio Service (GPRS), Enhanced Data rates for GSM Evolution (EDGE), dan Worldwide Interoperability for Microwave Access (Wimax). Penyelidikan ini mengkaji kaedah optimum pengurusan memori dan juga untuk pemprosesan yang pantas untuk aplikasi kelajuan tinggi yang merupakan suatu bentuk teknologi baru akan datang. Pada mulanya prestasi pelbagai konfigurasi penyahkod Viterbi berdasarkan perbezaan keadaan saluran dikenalpasti untuk digunakan ke Field Programmable Gate Array (FPGA). Pelaksanaan terakhir adalah menggabungkan tiga penyahkod Viterbi ke dalam satu teras. Perolehan kawasan bagi tiga Viterbi yang wujud berasingan dibandingkan dengan perkakasan gabungan adalah kira-kira 15%, dengan tiada kekurangan kelajuan dan daya pemprosesan. Tempoh pendaman dikira sebagai jumlah minimum berdasarkan saiz data. Tujuan utama untuk menghasilkan struktur perkakasan perkongsian ialah pada dasarnya memetakan struktur trellis Viterbi yang mudah kepada struktur yang lebih kompleks; di mana kaedah ini tidak akan mengambil mana-mana lebihan perkakasan yang ada. Yang penting dan ternyata sekali di dalam kajian ini adalah pengurangan kompleksiti untuk pelbagai penyahkod Viterbi yang sedia ada dalam satu perkakasan perkongsian.

# TABLE OF CONTENTS

| CHAPTER | TITLE                     | PAGE |

|---------|---------------------------|------|

|         | DECLARATION               | ii   |

|         | ACKNOWLEDGEMENT           | iii  |

|         | ABSTRACT                  | iv   |

|         | ABSTRAK                   | v    |

|         | TABLE OF CONTENTS         | vi   |

|         | LIST OF TABLES            | ix   |

|         | LIST OF FIGURES           | xi   |

|         | LIST OF ABBREVIATIONS     | xiv  |

|         |                           |      |

| 1       | INTRODUCTION              | 1    |

|         | 1.1 Background            | 1    |

|         | 1.2 Problem Description   | 3    |

|         | 1.3 Project Objectives    | 4    |

|         | 1.4 Scope of Project      | 4    |

|         | 1.5 Proposed Methodology  | 6    |

|         | 1.6 Outline of the Thesis | 8    |

| 2 | LITERATURE       | REVIEW                                  | 9  |

|---|------------------|-----------------------------------------|----|

|   | 2.1 Mobile syste | ems-GPRS and EDGE                       | 9  |

|   | 2.2 Wimax Syst   | ems                                     | 11 |

|   | 2.3 Viterbi Com  | piler by Altera                         | 14 |

|   | 2.4 MFDA (Mod    | dified Feedback Decoding Algorithm)     | 16 |

|   | 2.5 Other types  | of Adaptive Viterbi Algorithms          | 18 |

|   | 2.6 New Develo   | pments in Adaptive Coding               | 21 |

| 3 | THEORY           |                                         | 22 |

|   | 3.1 Channel Mo   | dels                                    | 22 |

|   | 3.1.1            | Multipath fading channel                | 24 |

|   | 3.1.2            | Methods to reduce the effects of fading | 25 |

|   | 3.1.3            | Combating Distortion                    | 27 |

|   | 3.1.4            | Combating Loss in SNR                   | 28 |

|   | 3.2 Convolution  | al Codes / Viterbi Decoder              | 29 |

|   | 3.2.1            | Encoder Structure                       | 29 |

|   | 3.2.2            | Generator representation                | 31 |

|   | 3.2.3            | Tree Diagram representation             | 31 |

|   | 3.2.4            | State Diagram representation            | 33 |

|   | 3.2.5            | Trellis Diagram representation          | 34 |

|   | 3.2.6            | Convolutional Decoding                  | 35 |

|   | 3.2.7            | Puncturing and Depuncturing             | 40 |

|   | 3.3 Fire Codes   |                                         | 41 |

|   | 3.4 Reed Solom   | on Codes                                | 41 |

|   |                  |                                         |    |

| 4 | DESIGN MET       | HODOLOGY                                | 42 |

|   | 4.1 Introduction |                                         | 42 |

|   | 4.2 Target FPG   | A description                           | 43 |

|   | 4.3 Implementat  | ion Flow Diagram                        | 44 |

|   | 4.4 RTL Archite  | ecture                                  | 48 |

|   | 4.5 Shared meth  | odology for the Viterbi Decoder         | 52 |

|              | 4.5.1          | BMC unit description                     | 57      |

|--------------|----------------|------------------------------------------|---------|

|              | 4.5.2          | ACS unit description                     | 60      |

|              | 4.5.3          | Trace Back Unit / Survivor Memory        | 65      |

|              |                |                                          |         |

| 5            | RESULTS        |                                          | 68      |

|              | 5.1 Overview   | ,                                        | 68      |

|              | 5.2 Approach   | in selecting candidate configuration     | 68      |

|              | 5.3 Algorithm  | n / Matlab results – Viterbi Performance | 69      |

|              | 5.3.1          | Trace back length determination          | 75      |

|              | 5.4 RTL resu   | lts                                      | 77      |

|              | 5.4.1          | Test method                              | 77      |

|              | 5.4.2          | Timing results                           | 78      |

|              | 5.4.3          | Functional coverage                      | 84      |

|              | 5.5 FPGA res   | sults                                    | 85      |

|              | 5.5.1          | FPGA configuration                       | 85      |

|              | 5.5.2          | FPGA system simulation                   | 86      |

| 6            | CONCLUSI       | IONS AND RECOMMENDATIONS                 | 90      |

|              | 6.1 Conclusion | on and Recommendations                   | 90      |

|              | 6.2 Recomme    | endation for Future Work                 | 91      |

| REFERENCES   |                |                                          | 92      |

| Appendix A-B |                |                                          | 101-127 |

# LIST OF TABLES

| TABLE NO. | TITLE                                       | PAGE |

|-----------|---------------------------------------------|------|

| 2.1       | Coding schemes in GPRS                      | 10   |

| 2.2       | Coding Schemes in EGPRS                     | 11   |

| 2.3       | Brief Summary of the Code Sets              | 15   |

| 3.1       | Conventional Bit Metric Values              | 39   |

| 4.1       | Input / Output signal for top level Viterbi | 49   |

|           | Decoder                                     |      |

| 4.2       | Input / Output signal for Viterbi_BMC block | 50   |

|           | (Branch Metric Calculator)                  |      |

| 4.3       | Input / Output signal for Viterbi_ACS block | 50   |

|           | (Add Compare Select)                        |      |

| 4.4       | Input / Output signal for Viterbi_MEM block | 51   |

|           | (Memory)                                    |      |

| 4.5  | Input / Output signal for Viterbi_traceback    | 51 |

|------|------------------------------------------------|----|

|      | block (Traceback)                              |    |

| 4.6  | Input / Output signal for Viterbi_filo block   | 51 |

|      | (First In-Last Out)                            |    |

| 4.7  | Generator Polynomial of the various Standards  | 52 |

|      | and its similarity                             |    |

| 4.8  | State Table of Constraint length 3 encoder of  | 53 |

|      | polynomial G[7,5].                             |    |

| 4.9  | State Table of Constraint length 4 encoder of  | 54 |

|      | polynomial G[15,11].                           |    |

| 4.10 | Rate 1/2 BMC calculation                       | 58 |

| 4.11 | Rate 1/3 BMC calculation                       | 59 |

| 4.12 | Pipelined structure of the BMC formula         | 59 |

| 5.1  | Test Methodology                               | 69 |

| 5.2  | Legend explanation                             | 70 |

| 5.3  | Summary of the plots in Figure 5.1,5.2 and 5.3 | 72 |

| 5.4  | PER values of packet size N=500 and N=1000     | 74 |

|      | respectively                                   |    |

| 5.4  | Statement coverage and Branch coverage from    | 84 |

|      | Modelsim                                       |    |

| 5.6  | Summary of APEX20K200E features                | 85 |

| 5.7  | LE used in the adaptive Viterbi design         | 86 |

# LIST OF FIGURES

| FIGURE NO. | TITLE                                      | PAGE |

|------------|--------------------------------------------|------|

| 1.1        | Tx - Rx modules                            | 5    |

| 1.2        | Conventional method for GPRS and EDGE      | 6    |

| 1.3        | Shared Hardware approach GPRS and          | 7    |

|            | EDGE                                       |      |

| 1.4        | Internal Viterbi blocks                    | 7    |

| 2.1        | Convolutional encoder constraint length 7  | 12   |

|            | and rate ½                                 |      |

| 2.2        | BTC and shortened BTC codes                | 13   |

| 2.3        | CTC encoder                                | 13   |

| 2.4        | Configurability of the Viterbi on Altera's | 15   |

|            | MegaCore                                   |      |

| 2.5  | Block diagram of a MFD                             | 17 |

|------|----------------------------------------------------|----|

| 3.1  | Channel Modeling                                   | 23 |

| 3.2  | The Three major performance categories in          | 26 |

|      | terms of BER vs EB/No.                             |    |

| 3.3  | Methods of Mitigating Frequency selective          | 27 |

|      | and Fast Fading.                                   |    |

| 3.4  | Methods to combat loss in SNR                      | 28 |

| 3.5  | General structure of convolutional encoder         | 29 |

| 3.6  | K=3, $r = \frac{1}{2}$ , m=2 convolutional encoder | 29 |

| 3.7  | Tree diagram representation for four input bit     | 32 |

|      | intervals                                          |    |

| 3.8  | State machine of the convolutional encoder         | 33 |

|      | in figure 3.6.                                     |    |

| 3.9  | Trellis diagram of the encoder of figure 3.6       | 34 |

| 3.10 | Trellis path for the input sequence of $x =$       | 35 |

|      | {1,0,1,1}                                          |    |

| 3.11 | Soft Decision and Hard Decision example            | 36 |

| 3.12 | Convolution Encoder + Viterbi decoder              | 37 |

|      | system                                             |    |

| 3.13 | BSC Channel, where p is the crossover              | 38 |

|      | probability                                        |    |

| 3.14 | System showing puncturing and                      | 40 |

|      | depuncturing blocks                                |    |

| 3.15 | Example of data structure after puncturing         | 40 |

| 3.16 | Example of data structure after depuncturing       | 41 |

| 4.1  | FPGA integration                                   | 42 |

| 4.2  | Flow Diagram of Viterbi Decoder                    | 44 |

| 4.3  | Behavioral structure of the branch metric          | 45 |

|      | computation                                        |    |

| 4.4  | Behavioral structure of the Add Compare            | 46 |

|      | Select unit                                        |    |

| 4.5  | FSM structure of the Traceback unit                | 48 |

| 4.6  | Top Level RTL Architecture of Viterbi              | 48 |

| $\mathbf{r}$ |     | 1    |            |

|--------------|-----|------|------------|

| ı١           | ecc | NA   | $\Delta r$ |

| .,           |     | ж 11 |            |

| 4.7   | Viterbi Flow Structure                         | 53 |

|-------|------------------------------------------------|----|

| 4.8   | Trellis Diagram for a constraint length 3 over | 55 |

|       | 1 time period                                  |    |

| 4.9   | Trellis diagram for constraint length 4 and 3  | 56 |

|       | over 1 time period                             |    |

| 4.10  | Branch Metric Unit                             | 58 |

| 4.11a | Trellis of K=3, 4 states                       | 60 |

| 4.11b | Trellis structure for K=4, 8 states            | 61 |

| 4.12  | ACS Unit                                       | 62 |

| 4.13  | 2 ACS units showing the shared multiplexer     | 63 |

| 4.14  | Sample Merging Paths and its selection         | 64 |

| 4.15  | Numerical Example of how the ACS works         | 65 |

| 4.16  | Memory structure for a traceback length of     | 66 |

|       | 50                                             |    |

| 5.1   | BER under AWGN channel                         | 70 |

| 5.2   | BER under fast fading with AWGN channel        | 71 |

| 5.3   | BER under Slow fading with AWGN                | 71 |

|       | channel                                        |    |

| 5.4   | Simulation curve of 3 different convolutional  | 73 |

|       | encoder                                        |    |

| 5.5   | BER of various traceback length MCS9-P1        | 75 |

| 5.6   | BLER of various traceback length MCS9-P1       | 76 |

| 5.7   | Functional RTL test methodology                | 77 |

| 5.8   | Timing Diagram showing the Code Rate 1/2       | 78 |

|       | input mechanism                                |    |

| 5.9   | Timing Diagram showing the Code Rate 1/3       | 78 |

|       | input mechanism                                |    |

| 5.10  | Timing diagram for configuration of K=5,       | 79 |

|       | rate ½                                         |    |

| 5.11  | Timing diagram for configuration of K=7,       | 79 |

|       |                                                |    |

|       | rate ½                                         |    |

#### rate 1/3

| 5.13 | Timing diagram of the BMC block        | 81 |

|------|----------------------------------------|----|

| 5.14 | Timing diagram of the ACS block        | 81 |

| 5.15 | Timing diagram of the Memory block     | 82 |

| 5.16 | Timing diagram of the Trace Back Block | 82 |

| 5.17 | Timing diagram of the FILO Block       | 83 |

| 5.18 | FPGA simulation setup                  | 87 |

| 5.19 | HyperTerminal settings                 | 88 |

### LIST OF ABBREVIATIONS

GPRS - General Packet Radio Service

EDGE - Enhanced Data Rates for GSM Evolution

3G - Third Generation

WiMAX - Worldwide Interoperability for Microwave Access

MIPS - Millions of Instructions per Second

DSP - Digital Signal Processor

FPGA - Field Programmable Gate Array

BPSK - Binary Phase Shift Keying

TX - Transmitter

RX - Receiver

FEC - Forward Error Control

BER - Bit-Error Rate

Eb/No - Energy per Bit over Spectral Noise Density

SNR - Signal to Noise Ratio

CRC - Cyclic Redundancy Check

WLAN - Wireless Local Area Network

GSM - Global System for Mobile communication

EGPRS - Enhanced GPRS

TB-CC - Tail Biting Convolutional Codes

BTC - Block Turbo Codes

CTC - Convolutional Turbo Codes

LDPCC - Low Density Parity Check Codes

ZT-CC - Zero Tail Convolutional Code

OFDM - Orthogonal Frequency Division Multiplexing

OFDM A - Orthogonal Frequency Division Multiplexing Access

RS - Reed Solomon

CS - Coding Scheme

MCS - Modulation Coding Scheme

BCH codes - Bose-Chauduri-Hocquenghem codes

GF - Galois Field

XOR - Exclusive OR

CPLD - Complex Programming Logic Device

JTAG - Joint Test-Action Group

ROM - Read Only Memory

RAM - Random Access Memory

PSK - Phase Shift Keying

GMSK - Gaussian Minimum Shift keying

TDD - Time Division Muliplexing

FDD - Frequency Division Muliplexing

BPS - bits per second

MFDA - Modified Feed back Decoding Algorithm

FDA - Feed Back Decoding

BSC - Binary Symmetric Channel

TB - Trace Back

#### **CHAPTER 1**

INTRODUCTION

## 1.1 Background

Wireless digital communications is one of the most advanced technologies at present. In order to transmit multimedia information, which includes not only voice information but also various kinds of data such as pictures and moving images, communication systems must support very low bit error rate (BER) digital transmission. The communication channel introduces noise and interference to corrupt the transmitted signal. At the receiver, the corrupted transmitted signal is mapped back to binary bits. The received binary information is an estimate of the

transmitted binary information. Bit errors may result due to the transmission and the number of bit errors depends on the amount of noise and interference in the communication channel.

Channel coding is often used in digital communication systems to protect the digital information from noise and interference and reduce the number of bit errors. If channel coding was not used, data would have to be sent at much higher power, and sometimes due to certain design constraints/system requirement, transmission power is a limiting factor. To overcome power issues and at the same time be able to withstand harsh channel conditions, the data is given some protection, where on the receiver side; the data can be recovered even if some portion of the data stream was corrupted with noise/fading. Channel coding is mostly accomplished by selectively introducing redundant bits into the transmitted information stream. These additional bits will allow detection and correction of bit errors in the received data stream and provide more reliable information transmission. The cost of using channel coding to protect the information is a reduction in data rate or an expansion in bandwidth.

There are two main types of error correcting codes, namely block codes and convolutional codes. There are many differences between block codes and convolutional codes. Block codes are based rigorously on finite field arithmetic and abstract algebra. They can be used to either detect or correct errors. Some of the commonly used block codes are Hamming codes, Golay codes, BCH codes, and Reed Solomon codes (uses non-binary symbols).

Convolutional codes are one of the most widely used channel codes in practical communication systems. These codes are developed with a separate strong mathematical structure and are primarily used for real time error correction. Convolutional codes convert the entire data stream into one single codeword. The encoded bits depend not only on the current k input bits but also on past input bits, so basically every encoded bit has some memory of its neighboring bits. The main decoding strategy for convolutional codes is based on the widely used Viterbi algorithm.

## 1.2 Problem Description

High data rate communication such as GPRS, EDGE, 3G, Wimax are susceptible to multipath fading effects and therefore reliable error control is essential in such wireless communications. Usually, systems have to meet certain BER requirements that will satisfy the worst case channel conditions. For an error correction encoder, to meet worst case scenarios, it usually requires high level of redundancy bits added to the information bits. Adding too many redundancy bits will again reduce the high data rate that we are trying to achieve in the first place. The channel will not be in the worst case all the time, and therefore it is possible to transmit at higher data rates for most of the time. To overcome the effect of noise under very bad channel, and also not burden the throughput with too much protection under good channel condition, the error control schemes have to be able to adapt to the channel that the device is working on. Under harsh channel conditions, the data will have heavy protection against interference to meet the required BER, and under good conditions, the data will have minimal or no protection, and increase the data throughput.

Implementation wise, channel decoders have a high latency in decoding the received data and consumes many clock cycles or MIPS if it is implemented on DSP. With the demand for high data rate applications, latency is no longer a compromise in design. Parallel processing of the decoding blocks has become a must and its impact to the size of the decoder in terms of gate count has to be

compromised. Too high of a gate count or logic cells in FPGA is also not desired. DSP processors with no power in parallel processing have become too slow and usually require a hardware acceleration block to do such high speed processing in a separate core.

#### 1.3 Project Objectives

The most widely used decoding algorithm as mentioned above is the Viterbi decoder which is used with different parameters for different standards requirements. This thesis analyses the different Viterbi decoders and implements a reconfigurable adaptive Viterbi decoder with shared hardware structure for GSM, GPRS, EDGE and Wimax technologies. The adaptability nature of the implemented Viterbi decoder helps to combat different channel conditions and can be used in a configurable manner to improve the received BER. The shared hardware structure would help in limiting the number of logic cells used compared to if the implementation were to be done separately. The high performance generic soft input hard output Viterbi decoder is prototyped on a FPGA.

# 1.4 Scope of Project

The scope of this study would be focused towards the channel coding blocks, such as convolution coding/Viterbi decoding and studying the effect of various channel models to obtain the best suitable coding rate and constraint length. The study does not include the effect of modulation, as the modulation scheme is fixed to BPSK.

The parameters of the various Viterbi decoders used in the study are of coding rates r = 1/2, and r = 1/3, and constraint length k = 5 and k = 7, which are the ones used in GSM, GPRS, EDGE and WiMax.

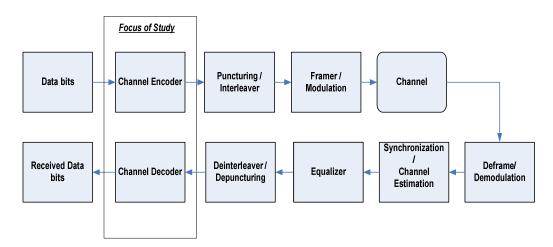

The fading model is a non-frequency selective Rayleigh fading with characteristics such as fast and slow fading. Fast fading is assumed such that the coherence bandwidth is larger that a symbol period, and the fading is uncorrelated, making the symbols independent to each other. Slow fading is limited to affect around 20 consecutive symbols, to avoid enhanced methods of interleaving. The interleaving mechanism to overcome the slow fading will be the standard block rectangular interleaver. It is assumed to be independent to the encoder/decoder design as it is placed after the channel coding process. The channel estimate and synchronization is assumed to be perfect. Figure 1.1 highlights the area of research.

**Figure 1.1**: Tx - Rx modules

The channel encoder system can achieve various coding rates with the use of puncturing. Puncturing removes certain bit streams from the encoded data stream. Puncturing is used to achieve coding rates of r = 2/3, r = 3/4, r = 5/6 and r = 7/8.

The focus of the project basically is on the channel encoder (convolutional encoders) and decoder (Viterbi decoders) blocks with various CRC types. The CRC

is added to detect if the channel decoder was able to reconstruct the frame correctly or if there was a frame error.

## 1.5 Proposed Methodology

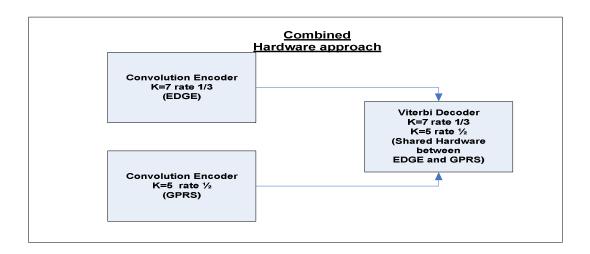

The designed adaptive encoder/decoder could be adopted to any wireless communication systems that requires robust error correction and also support high data rate. The hardware implementation combines the Viterbi decoder of constraint length K = 7 and K = 5. This combination allows the use of shared Viterbi decoder to be used on the GPRS, EDGE (Enhanced Data rates for Global Evolution) and 802.11(WLAN)/802.16 (Wimax) systems.

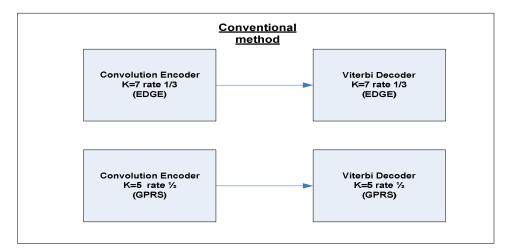

Figure 1.2: Conventional method for GPRS and EDGE

Figure 1.2 depicts the traditional method in having two different constraint lengths Viterbi decoder. For a mobile device that supports EDGE, it has to be backward compatible to the GPRS network. Since both these systems use different types of encoding methods, the conventional method of design is described in Figure 1.2. Below in Figure 1.3, a combined approach to share relevant blocks in doing the computation for the Viterbi decoder is described.

Figure 1.3: Shared Hardware approach GPRS and EDGE

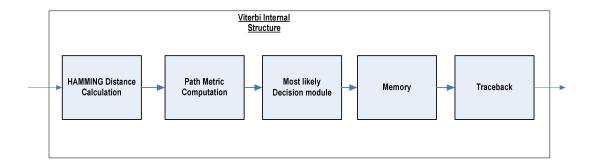

Figure 1.4 shows the internal block diagram of a Viterbi decoder. Since all Viterbi decoders consist of these basic blocks, combining two different Viterbi decoder structure will be possible with the addition of configurable blocks.

Figure 1.4: Internal Viterbi blocks

#### 1.6 Outline of the Thesis

The thesis is outlined into 6 chapters. Chapter 2 will discuss the work done by other researchers in the related field. Chapter 3 describes the theory of background knowledge on some encoding/decoding processes is described to some detail. Further on in Chapter 4, the design methodology is described, followed by the results obtained from the experiment in Chapter 5. The results will cover both the results on the algorithm which includes performance curves and also on the RTL implementation. Chapter 6 summarizes the important findings regarding the shared structure and the thesis conclusion.