## Electrical Characterization of the High Speed I/O Data Bus Using Cross Correlation Method

Jimmy Huat Since Huang, Zuri Shaameri Ahmad, Teong Guan Yew

<sup>1</sup>University of Technology Malaysia, Penang, Malaysia

<sup>2</sup>Intel Microelectronic (M) Sdn Bhd, FTZ, 11900 Bayan Lepas, Penang, Malaysia

jimmy.huat.since.huang@intel.com, ahmadzs@yahoo.com, teong.guan.yew@intel.com

#### Abstract

High speed data transportation between the CPU and peripherals on the PC motherboard is needed to support heavy data traffic such as multimedia, games and broadband networks. At multi Gbits/sec high speed, impedance mismatch between the CPU and peripherals becomes critical and limits the possible maximum throughput. The I/O transportation bus can be modeled as a linear time invariant system. The output signal at the receiver is the convolution function of the transfer function and transmitter signal. Due to the complexity of the motherboard ingredient, it is desired to model the I/O bus in black box behavior model. Instead of using traditional passive measurement method such as Time Domain Reflectometry (TDR) and Scattering parameter measurement, cross correlation method is used to find out the impulse response transfer function when the I/O Bus is active. By using MATLAB and SPICE tools, the method is simulated to understand its accuracy and robustness under noisy environment.

#### Introduction

Computer system organization has three main components, the CPU, the memory subsystem and the I/O subsystem. Bus is a terminology used to describe the interconnecting between the components in the architecture organization. Physically, a bus is a set of wire to send the information from one component to another; the source output the components onto the bus. The destination component then inputs this data from the bus. Due to the increasing complexity of computer architecture, the bus system is much more efficient in higher speed, less power consumption; less space and fewer pin routes.

Moore's Law drives transistor scaling by 2x for every 21 months. Advanced computer system benefits from the transistor scaling allowing more processing capabilities can be achieved. Higher data bandwidth is needed to support the increasing processing power. The performance degrades if the computer spends most of its time waiting for the data. The needs of data bandwidth is even critical with the introduction of parallel processing, distribution computing system, multi core CPU and more efficient pipeline architecture.

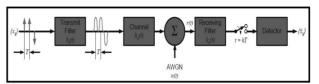

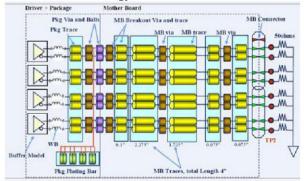

From communication view of point, the transmission bus channel is composed of transmitter block, bus channel block and receiver channel block as illustrated in Figure 1. The source output is x(t), channel impulse response is h(t), receiver output is r(t) and r(t) is Additive White Gaussian noise. The receiver output is the convolution of r(t) and r(t) plus summation of r(t).

$$r(t) = x(t) \otimes h(t) + n(t)$$

Figure 1: Transmission line can be modeled into communication blocksets

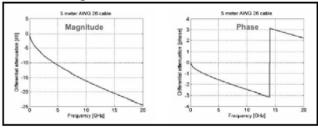

The transmission bus channel behaves as a low pass filter because the channel loss increases with the frequency. It is due to skin effect loss and dielectric loss. Instead of amplitude loss, the channel also suffers from phase distortion as illustrated in Figure 2.

Figure 2: Frequency response of transmission line behaves like a low pass filter

Equalizer is implemented to improve the signal quality by introducing the inverse transfer function of the transmission bus channel so that it can cancel the channel loss effect and retrieve back the original transmitting data. The equalizer,  $C(f) = H^{-1}(f)$ , can be placed at the transmitter, receiver or both side. The equalizer can be an analog passive high pass filter or discrete FIR filter. No matter which equalizer is used, the H(f) must be characterized to obtain the inverse transfer function coefficients.

#### **Background**

There are active components and passive components in I/O Bus channel. The active elements include I/O buffers, opamp, PLL and data pattern. Passive elements include wire, printed circuit board, IC package, connector and others. At low speed, the passive elements are just part of the product's packaging but at higher speed they behave like a transmission line and affects electrical performance directly.

Figure 3: Interconnect diagram of chip, package and printed circuit board

Due to the complexity and overheads in generating the impulse or step response to the transmission bus channel during active condition, auto and cross correlation method is proposed because the

$$R_{XX}(\tau) = E[X(t)X * (t - \tau)],$$

(1)

$$R_{XX}(\tau) = P_0 (1 - \frac{|\tau|}{T_b}),$$

(2)

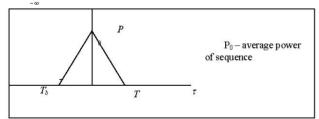

where the input is pseudo random sequence, Tb is the pulse period and  $P_0$  is the average power of the random sequence as Figure 4

$$R_{yy}(\tau) \approx \sigma_{\tau}^2 \delta(\tau),$$

(3)

Given  $\sigma_x^2$  is the variance of the inputs, if the pseudo random has a long and non-repetitive sequence

$$S_{XX}(f) = \int_{-\infty}^{\infty} \left\{ \lim_{T \to \infty} \frac{1}{T} \int_{-T/2}^{T/2} R_{XX}(t_1, t_1 - \tau) dt_1 \right\} \exp(-j2\pi f \tau) d\tau$$

(4)

$$\lim_{T \to \infty} \frac{1}{T} \int_{-T/2}^{T/2} R_{XX}(t_1, \tau) dt_1 = R_{XX}(\tau)$$

(5)

$$S_{XX}(f) = \int_{-\infty}^{\infty} R_{XX}(\tau) \exp(-j2\pi f \tau) d\tau \tag{6}$$

For a impulse response of  $R_{XX}(\tau) = \sigma_x^2 \delta(\tau)$

$$S_{XX}(f) = \sigma_{x}^{2} \tag{7}$$

By using additive White Gaussian Pseudo Random Sequence as the inputs,

(8)

$$R_{YX}(\tau) = E[Y(t)X(t-\tau)]$$

$$= E[\int_{0}^{\infty} h(\lambda)X(t-\lambda)d\lambda X(t-\tau)]$$

Figure 4: AutoCorrelation function of Pseudo random sequence

By putting the expectation operator within the integral, the cross correlation function obtained is

$$R_{YX}(\tau) = \int_{-\infty}^{\infty} h(\lambda) E[X(t-\lambda)X * (t-\tau)d\lambda]$$

(9)

Since X(t) is stationary random process, the autocorrelation of X(t) derived,

$$E[X(t_1)X * (t_1 - (\tau - \lambda))] = R_{XX}(\tau - \lambda)$$

(10)

$$R_{YX}(\tau) = \int_{-\infty}^{\infty} h(\lambda) R_{XX}(\tau - \lambda) d\lambda$$

$$= h(\tau) * R_{XX}(\tau)$$

(11)

The cross power spectrum is

$$S_{YX}(f) = \int_{-\infty}^{\infty} R_{YX}(\tau) \exp(-j2\pi f \tau) d\tau$$

(12)

$$S_{YX}(f) = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} h(\lambda) R_{XX}(\tau - \lambda) \exp(-j2\pi f \tau) d\lambda d\tau$$

$$= H(f)S_{XX}(f)$$

$$= H(f)\sigma_{x}^{2}$$

(13)

Data packet pattern behaves as a pseudo random sequence generator (PRSG). It itself is the inputs to this equation.

## Methodology

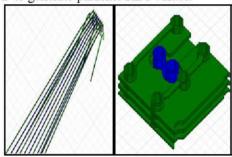

There are some complex motherboard components that require detail electrical modeling such as package, breakout motherboard trace, vias, motherboard trace and connector. These interconnect segments are modeled in 2D or 3D models using appropriate simulation tools. The board traces are modeled using Ansoft Q2D to obtain the transmission line RLGC model. AnsoftLink™ is a tool used to extract 3D model with actual dimension from package layout. The same 3D model is then imported, modeled and analyzed in Ansoft Q3D to generate parasitic RLC values.

Figure 5: Physical dimension of Q3D interconnect model (wirebond, via model).

The I/O bus system as Figure 6 is simulated to obtain the transient response using step or impulse function. Then cross correlation method is used and the output is compared with the traditional method. It succeeds if both them match. Then it will be tested again under noisy environment. Figure 7 illustrates the methodology chart.

Figure 6: Full EM Modeling Platform Data Bus topology system

Figure 7: Methodology flow chart

## Simulation from single transmission model

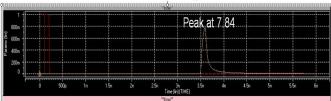

Cross correlation method was used on simple transmission line model. In HSPICE, A pulse wave signal was injected at the transmitter to obtain impulse response. The HSPICE result was used as the bench mark for comparison.

Figure 8: HSPICE impulse response analysis. Red line is the pulse wave at transmitter while the magenta line is output at receiver

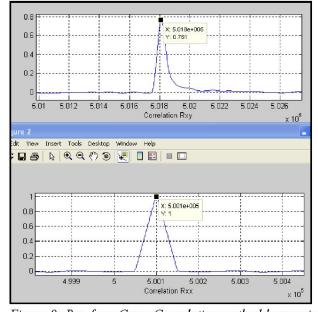

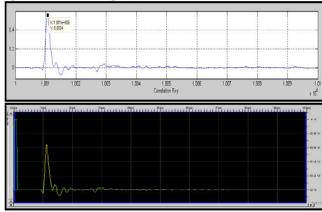

Figure 9: Rxy from Cross Correlation method by running 10,000 sample random data

From the pulse response result, the overshoot amplitude was 0.784 and the delay time was 3.4ns. Comparing with cross correlation method in Figure 9 by using 10,000 samples in HSPICE, the overshoot was 0.761, which was close to the impulse response analysis. Both of them had same delay time, 3.4ns, and very similar waveform shape. Thus it was concluded that cross correlation method using 10,000 sample data producing convincing h(t).

The correlation method was also tested under noisy environment. By injecting a random uniform 10% noise and 10% DC gain. The result in Figure 10 still captured h(t) overshoot, delay time and waveform shape accurately. The difference was the DC gain only. Correlation method was proven to be effective under noisy environment.

Figure 10: Rxy under uniform 10% random noise condition

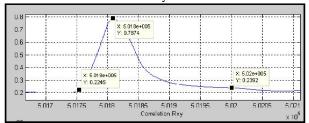

# Simulation using complex full EM modeling platform data bus topology

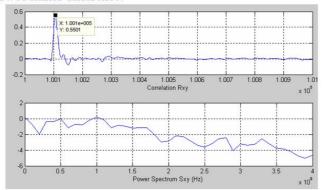

The cross correlation method was applied on complicated data bus system as shown in Figure 6. Again, using HSPICE simulation, single pulse response analysis was used as the bench mark for comparison. From the result, the overshoot amplitude was 0.64 and the delay time was 1.1ns. Comparing with cross correlation method using 10,000 samples, the overshoot was 0.553, which was close to the impulse response analysis. Both of them had same delay time, 1.1ns, and very similar waveform shape as shown in Figure 11. Thus it was concluded that correlation method using 10,000 sample data produce convincing h(t).

Figure 11: Comparison between impulse response and correlation method on complicated data bus. Both waveforms had very similar waveform shape

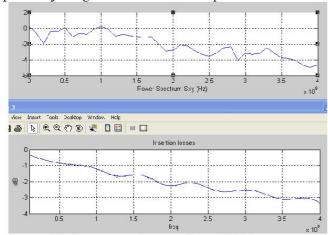

By using Blackman Tukey Window, the power spectrum, Sxy was round -1dB/GHz while S21, the result was -0.875dB/GHz as illustrated in Figure 12. They were close inside 4GHz frequency band Thus it was concluded that cross correlation

method producing Sxy but the accuracy was needed to be improved by using better Window technique.

Figure 12: Comparison between Sxy and S21

The correlation method was also tested under noisy environment. By injecting a distributed random uniform 10% noise, the result still captured h(t) overshoot, delay time and waveform shape accurately. The Sxy also didn't show any difference.

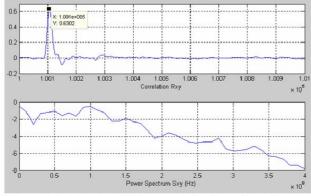

By injecting 50ps jitter noise, the result still captured h(t) overshoot, delay time and waveform shape accurately although not as accurate as random noise. The Sxy also showed minor difference.

Figure 13: Injecting 10% distributed random noise. No difference compared with noiseless environment

Figure 14: Injecting 50% normal distributed random jitter noise. Slight difference was observed compared with noiseless environment

## Conclusions

The result from cross correlation method correlated with the benchmark impulse response analysis. By simulating the model under 10% random noise, the result had very minor difference compared to noise free simulation. The algorithm was proven to be robust.

The algorithm was applied to HSPICE full EM modeling data bus transmission topology system that representing actual motherboard system. The Rxy result correlated with h(t) from impulse response. The Sxy was close to insertion loss, S21 but not as close as h(t). It was due to the Windowing technique because Blackman Tukey produced noise over power spectrum. It was suggested to explore better Windowing technique for more accurate result.

The algorithm was tested under noisy environment. It was proven to be very robust with almost no difference using 10% distributed random noise. With the presence of 50% jitter, the Rxy and Sxy result were still look good but not as close as 10% noise.

## Acknowledgments

Thanks to Intel Corporation Penang Design Center in providing EDA tools, circuit behavior model, package and motherboard electrical modeling.

#### References

- Maynard Falconer, "Bus Design Boot Camp", Intel Corp, 2005

- 2. Adam Norman, "Chapter 13: Peak Distortion analysis" Bus Design Boot camp, 3/3/05

- M. Cases, D. N. de Araujo, E. Matoglu, "Electrical Design and Specification Challenges for High Speed Serial Links", 2005 Electronics Packaging Technology Conference

- Howard Johnson, "High-Speed Signal Propagation", Prentice Hall, 2003

- B. Casper, M. Haycock, R. Mooney, "An Accurate and Efficient Analysis Method for Multi-Gb/sChip-to-Chip Signaling Schemes," Symposium on VLSI Circuits Digest of Technical Papers, 2002, pp. 54-57, June 13-15, 2002

- 6. Cattalen Pelard, Edward Gebara, Andrew J. Kim, Michael G. Vrazel, Franklin Bien, Youngsik Hur, Moonkyun Maeng, Soumya Chandramouli, Carl Chun, Sanjay Bajekal, Stephen E. Ralph, Bruce Schmukler, Vincent M. Hietala, "Realization of Multigigabit Channel Equalization and Crosstalk Cancellation Integrated Circuits", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 39, NO. 10, OCTOBER 2004