# IMPROVED CHARACTERISTICS OF RADIO FREQUENCY INTERDIGITAL CAPACITOR

# LIM YUN ROU

A project report submitted in fulfilment of the requirements for the award of the degree of Master of Engineering (Electrical – Electronics & Telecommunication)

> Faculty of Electrical Engineering Universiti Teknologi Malaysia

> > **APRIL, 2006**

To My Beloved Family

#### **ACKNOWLEDGEMENTS**

For the success of this study, I would like to thank all those who helped with the work undertaken in this study especially to:-

My supervisor, Associate Professor Dr. Mazlina Esa for her valuable guidance, assistance and advice, in which without her this study can never succeed.

My friends for their continuous suggestion and encouragement from the beginning until the end of study.

Finally, I would like to dedicate my appreciation to my family for their continuous support and encouragement.

#### ABSTRACT

Technology advances in complimentary-metal-oxide-silicon (CMOS) process offer some interesting possibilities for radio frequency (RF) circuit designers. Some circuits that would have to be done with GaAs monolithic microwave integrated circuits (MMICs), for instance, are now possible in CMOS. While the transistor speed has been improving significantly, fuller integration of RF integrated circuits (RFICs) is often retarded by the absence of high quality, high rangebility and efficient on-chip passive components. This thesis presents the possibilities of improving the characteristics of an RF capacitor having interdigital configuration. Modifications in the form of combline structure were introduced into the conventional configuration to improve the capacitor characteristics. Performance in the form of capacitance and Quality, Q, factor were investigated through simulations using electromagnetic simulation software, Ansoft HFSS. The analysis and comparison between conventional and the proposed interdigital capacitor (IDC) with combline structure were discussed in detail. It can be concluded that the proposed IDC with combline structure improves the capacitance of an IDC. The optimum combline configuration which achieved useful capacitance with sufficiently high Q factor is the design with 110 mils effective finger length. It produces 5.48 pF capacitance at first resonance of 2 GHz, with sufficiently high Q factor of 13.88. This is a factor of 1.72 higher than the corresponding conventional IDC having 3.18 pF at first resonance of 3 GHz albeit 10 % slightly higher Q factor of 15.41.

#### ABSTRAK

Kecanggihan teknologi pemprosesan silikon-oksida-logam-pelengkap (CMOS) menawarkan peluang menarik kepada perekabentuk litar frekuensi radio. Sesetengah litar yang perlu direkabentuk seperti menggunakan litar bersepadu gelombang mikro monolitik (MMICs), kini boleh dilakukan dengan teknologi CMOS. Sementara kelajuan transistor meningkat dengan pesat, penyepaduan sepenuhnya litar bersepadu RF (RFIC) terbantut oleh ketiadaan komponen pasif atascip yang berkualiti tinggi, berkebolehharapan tinggi dan tinggi kecekapan. Tesis ini membentangkan kemungkinan untuk membuat penambahbaikan terhadap ciri kapasitor RF menggunakan konfigurasi interdigital. Modifikasi berbentuk struktur talian komb diperkenalkan pada kapasitor interdigital konvensional untuk memperbaiki ciri prestasinya. Prestasi dalam bentuk kapasitan and faktor kualiti (Q) dikaji menerusi simulasi perisian elektromagnet, Ansoft HFSS. Analisis dan perbandingan antara kapasitor interdigital konvensional dan kapasitor interdigital dengan struktur talian komb dibincang dengan terperinci. Dapat disimpulkan bahawa kapasitor interdigital dengan struktur talian komb meningkatkan kapasitan bagi kapasitor interdigital. Konfigurasi talian komb optimum yang memperoleh kapasitan berguna dan faktor Q yang cukup tinggi adalah rekabentuk dengan panjang jari berkesan bernilai 110 mil. Ia menghasilkan kapasitan 5.48 pF pada resonans pertama 2 GHz dengan faktor Q mencukupi sebesar 13.88. Nilai ini adalah 1.72 lebih tinggi berbanding struktur IDC konvensional dengan 31.8 pF pada resonans pertama 3 GHz, namun dengan faktor Q = 15.41 yang 10 % sahaja lebih tinggi.

## TABLE OF CONTENTS

PAGE

| TITLE                 | i    |

|-----------------------|------|

| ADMISSION             | ii   |

| DEDICATION            | iii  |

| ACKNOWLEDGEMENTS      | iv   |

| ABTRACT               | v    |

| ABSTRAK               | vi   |

| TABLE OF CONTENTS     | vii  |

| LIST OF TABLES        | x    |

| LIST OF FIGURES       | xi   |

| LIST OF SYMBOLS       | xvi  |

| LIST OF ABBREVIATIONS | xvii |

| CHAPTER I | INT | RODUCTION                                  | 1 |

|-----------|-----|--------------------------------------------|---|

|           | 1.1 | Background of Study                        | 1 |

|           | 1.2 | Goals and Limitations of On-chip Capacitor | 4 |

|           |     | Design                                     |   |

CONTENTS

# PAGE

| 1.3 | Objectives       | 5 |

|-----|------------------|---|

| 1.4 | Scope of Project | 6 |

| 1.5 | Project Outline  | 7 |

| CHAPTER II | LIT | ERATURE REVIEW                    | 9  |

|------------|-----|-----------------------------------|----|

|            | 2.1 | Basic capacitor at High Frequency | 9  |

|            | 2.2 | Capacitor Parameters and Model    | 13 |

|            | 2.3 | Interdigital Capacitor (IDC)      | 15 |

|            | 2.4 | Summary                           | 22 |

| CHAPTER III | MET | THODO  | DLODY                                   | 24 |

|-------------|-----|--------|-----------------------------------------|----|

|             | 3.1 | Introd | uction                                  | 24 |

|             | 3.2 | Overa  | ll Project Flow                         | 24 |

|             | 3.3 | Imple  | mentation and Simulation of IDC with    |    |

|             |     | Comb   | line Structure                          | 26 |

|             |     | 3.3.1  | Layout of IDC with Combline Structure   | 26 |

|             |     | 3.3.2  | Combline Structures as Capacitors with  |    |

|             |     |        | Parallel Connection in High Frequency   |    |

|             |     |        | Range                                   | 28 |

|             |     | 3.3.3  | Simulation of Conventional and Combline |    |

|             |     |        | Interdigital Capacitor                  | 32 |

# CONTENTS PAGE

| CHAPTER IV | RES | ULTS AND DISCUSSION      | 38 |

|------------|-----|--------------------------|----|

|            | 4.1 | Introduction             | 38 |

|            | 4.2 | S- and Z-parameters      | 38 |

|            | 4.3 | Capacitance and Q Factor | 54 |

| CHAPTER V | CON | NCLUSION                               | 65 |

|-----------|-----|----------------------------------------|----|

|           | 5.1 | Conclusion                             | 65 |

|           | 5.2 | Recommendations for Future Improvement | 66 |

# REFERENCES

69

# LIST OF TABLES

| TABLE NO. | TITLE                                                                                                                                        | PAGE |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1       | Capacitor behavior with respect to frequency range.                                                                                          | 14   |

| 3.1       | Settings and parameter assumptions in HFSS simulation for experiment 1.                                                                      | 34   |

| 3.2       | Settings and parameter assumptions in HFSS simulation for experiment 2.                                                                      | 35   |

| 3.3       | Settings and parameter assumptions in HFSS simulation for experiment 3.                                                                      | 36   |

| 3.4       | Settings and parameter assumptions in HFSS simulation for experiment 4.                                                                      | 37   |

| 4.1       | Summary of Capacitance and Q factor for both conventional and combline IDC with 22 mils effective                                            |      |

|           | finger length and 6 fingers $(N = 6)$ .                                                                                                      | 56   |

| 4.2       | Summary of Capacitance and Q factor for both<br>conventional and combline IDC with 66 mils effective<br>finger length and 6 finger $(N = 0)$ | 50   |

|           | finger length and 6 fingers $(N = 6)$ .                                                                                                      | 59   |

| 4.3       | Summary of Capacitance and Q factor for both conventional and combline IDC with 110 mils effective                                           |      |

|           | finger length and 6 fingers $(N = 6)$ .                                                                                                      | 61   |

## LIST OF FIGURES

| FIGURE NO. | TITLE                                                                                                                                                                                                                                                                                                                                              | PAGE     |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

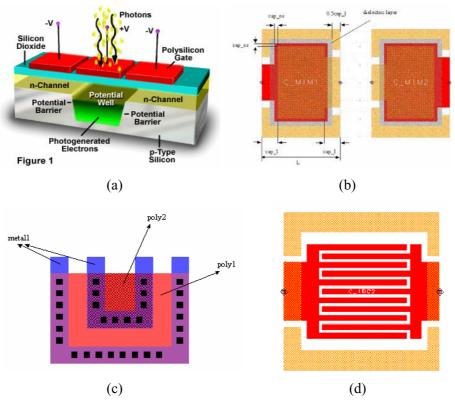

| 1.1        | Different types of CMOS or BiCMOS capacitor. (a)                                                                                                                                                                                                                                                                                                   |          |

|            | MOSFET gate oxide capacitor, (b) MIM Capacitor, (c)                                                                                                                                                                                                                                                                                                |          |

|            | Double-poly capacitor, (d) IDC.                                                                                                                                                                                                                                                                                                                    | 4        |

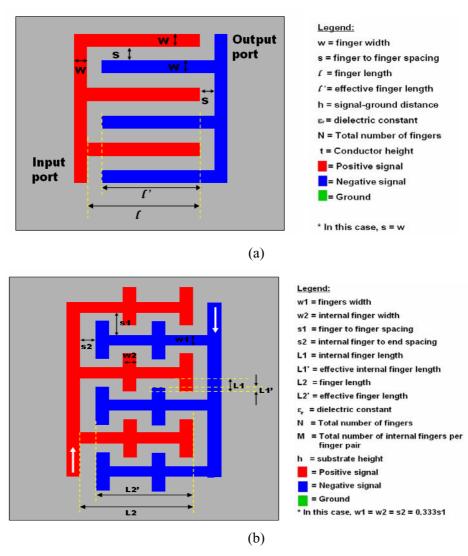

| 1.2        | IDC configurations (a) basic, (b) six fingers.                                                                                                                                                                                                                                                                                                     | 6        |

| 2.1        | Basic capacitor. (a)Two thin plate conductors with fixed                                                                                                                                                                                                                                                                                           |          |

|            | distance d, plate area A, and charges +Q on one plate and                                                                                                                                                                                                                                                                                          |          |

|            | -Q on the other form a parallel-plate capacitor, (b)                                                                                                                                                                                                                                                                                               |          |

|            | Voltage is applied across the plates, the electric field in                                                                                                                                                                                                                                                                                        |          |

|            | the dielectric displaces electric charges.                                                                                                                                                                                                                                                                                                         | 9        |

| 2.2        | System configuration consisting of two parallel plates in                                                                                                                                                                                                                                                                                          |          |

|            | the air. Fixed dimension d=8 cm, a=3 mm, h=1 mm.                                                                                                                                                                                                                                                                                                   | 10       |

| 2.3        | Plots of the device susceptance against frequency for                                                                                                                                                                                                                                                                                              |          |

|            | three different localization of the input terminals. (a) $d_2 =$                                                                                                                                                                                                                                                                                   |          |

|            | 8 cm, $d_1 = 0$ cm. (b) $d_2 = 6$ cm, $d_1 = 2$ cm. (c) $d_2 = 4$ cm,                                                                                                                                                                                                                                                                              |          |

|            | $d_1 = 4$ cm.                                                                                                                                                                                                                                                                                                                                      | 12       |

| 2.4        | Series RLC network representing behavior of a simple                                                                                                                                                                                                                                                                                               |          |

|            | parallel plate capacitor at high frequency.                                                                                                                                                                                                                                                                                                        | 13       |

| 2.5        | Conventional interdigital capacitor layout, (a) Cross                                                                                                                                                                                                                                                                                              |          |

|            | section view. (b) Top view.                                                                                                                                                                                                                                                                                                                        | 16       |

| 2.6        | Interdigital capacitor in Gary D. Alley study and its low                                                                                                                                                                                                                                                                                          |          |

|            | frequency equivalent circuit.                                                                                                                                                                                                                                                                                                                      | 17       |

| 2.5        | 8 cm, $d_1 = 0$ cm. (b) $d_2 = 6$ cm, $d_1 = 2$ cm. (c) $d_2 = 4$ cm,<br>$d_1 = 4$ cm.<br>Series RLC network representing behavior of a simple<br>parallel plate capacitor at high frequency.<br>Conventional interdigital capacitor layout, (a) Cross<br>section view. (b) Top view.<br>Interdigital capacitor in Gary D. Alley study and its low | 13<br>16 |

| 2.7  | Coplanar interdigital capacitor. (a) Layout, (b) Circuit model.                                                                                                                                                                                                                                                                           | 17       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.8  | Series capacitance of coplanar interdigital capacitor with finger length varying from 100 $\mu$ m to 350 $\mu$ m.                                                                                                                                                                                                                         | 18       |

| 2.9  | An IDC structure having zig-zag fingers. Structure<br>characteristics: $w = 1.2$ mm, $t = 34 \mu$ m, $h = 1.27$ mm, $L = 2.6$ mm, $b = 2$ mm, $s = 0.2$ mm, $d = 0.28$ mm, $w_f = 0.4$<br>mm, $\alpha = 90^\circ$ , $w_b = 0.4$ mm, $w_{gx} = 15.36$ mm, $w_{gy} = 33.08$<br>mm, $\varepsilon_r = 10.2$ .                                 | 18       |

| 2.10 | Comparison of magnitude of S-parameter versus<br>frequency for conventional IDC, IDC with zig-zag                                                                                                                                                                                                                                         |          |

| 2.11 | fingers and the equivalent circuit.<br>Equivalent circuit for the IDC structure with zig-zag<br>fingers. (a) Quasi static network, (b) <i>n</i> th high frequency<br>network.                                                                                                                                                             | 19<br>20 |

| 2.12 | Equivalent circuit of IDC.                                                                                                                                                                                                                                                                                                                | 21       |

| 2.13 | LC sensors comprises of a series connected inductor and<br>interdigitated capacitor LC circuit printed on a plastic<br>substrate used in food quality control application. The<br>sensor is covered with a layer of polyurethane to prevent<br>the conductive biological medium from shorting the<br>capacitor and damping the resonance. | 22       |

| 3.1  | Flow chart showing the overall project activities.                                                                                                                                                                                                                                                                                        | 25       |

| 3.2  | Conventional IDC layout.                                                                                                                                                                                                                                                                                                                  | 27       |

| 3.3  | Planar IDC with combline structure and side feeder.                                                                                                                                                                                                                                                                                       | 27       |

| 3.4  | Two capacitors connected in parallel connection<br>operating at lower frequency and the equivalent<br>capacitance.                                                                                                                                                                                                                        | 28       |

| 3.5  | Capacitor model operating at high frequency range and the simplified model.                                                                                                                                                                                                                                                               | 29       |

| 3.6 | Relationships of impedance versus frequency, (a) parallel<br>and (b) series equivalent circuit                                                                                                                                                                                                               | 30                              |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3.7 | Comparison of different capacitor impedance profiles. (a)<br>One 10 nF versus two 5 nF capacitors. (b) One 20 nF<br>versus two 10 nF capacitors. (c) One 20 nF versus four 5                                                                                                                                 | 21                              |

| 3.8 | nF capacitors.<br>Example of an combline IDC section equivalent to five<br>capacitors connected in parallel.                                                                                                                                                                                                 | <ul><li>31</li><li>32</li></ul> |

| 4.1 | Simulation models in HFSS for conventional IDC with 6 fingers ( <i>N</i> =6) and various effective fingers length, <i>l</i> '. (a) Simulation model with 45° view angle. (b) $l' = 22$ mils                                                                                                                  |                                 |

| 4.2 | [1X], (b) $l' = 66$ mils [3X] and (c) $l' = 110$ mils [5X].<br>Simulated return and insertion loss responses for the<br>conventional IDC with <i>N</i> =6 and increasing finger length<br>from 1X, 3X to 5X simulated from 1 GHz to 40 GHz. (a)<br>l' = 22 mils, (b) $l' = 66$ mils and (c) $l' = 110$ mils. | 39<br>40                        |

| 4.3 | Normalized impedance profile for conventional IDC with $N=6$ and increasing effective fingers length from 1X, 3X to 5X simulated from 1 GHz to 40 GHz. (a) $l' = 22$ mils, (b) $l' = 66$ mils and (c) $l' = 110$ mils.                                                                                       | 42                              |

| 4.4 | Simulation models in HFSS for combline IDC with 6 fingers ( $N$ =6) and various effective fingers length, $l'$ . (a) Simulation model with 45° view angle. (b) $l' = 22$ mils [1X], (b) $l' = 66$ mils [3X] and (c) $l' = 110$ mils [5X].                                                                    | 43                              |

| 4.5 | Simulated return and insertion loss responses for the combline IDC with <i>N</i> =6 and increasing finger length from 1X, 3X to 5X simulated from 1GHz to 40 GHz. (a) $l' = 22$ mils, (b) $l' = 66$ mils and (c) $l' = 110$ mils.                                                                            | 44                              |

| 4.6  | Normalized impedance profile for the combline IDC with $N=6$ and increasing finger length from 1X, 3X to 5X simulated from 1GHz to 40 GHz. (a) $l' = 22$ mils, (b) $l' = 66$ mils and (c) $l' = 110$ mils. (b) $l' = 66$ mils. (c) $l' = 110$ mils                    | 46 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.7  | Simulation models in HFSS for conventional IDC with 22 mils effective fingers length ( $l' = 22$ mils) and various finger numbers, N. (a) Simulation model with 45° view angle, (b) $N = 6$ [1X], (c) $N = 12$ [ 2X] and (c) $N = 18$ [3X].                           | 47 |

| 4.8  | Simulated return loss and insertion loss responses for the conventional IDC with 22 mils effective finger length ( $l' = 22 \text{ mils}$ ) and increasing total fingers from 1X, 2X to 3X simulated from 1GHz to 40 GHz. (a) $N = 6$ . (b) $N = 12$ . (c) $N = 18$ . | 48 |

| 4.9  | Normalized impedance profile for conventional IDC with 22 mils effective fingers length ( $l' = 22$ mils) and increasing total fingers from 1X, 2X to 3X simulated from 1 GHz to 40 GHz. (a) $N = 6$ . (b) $N = 12$ . (c) $N = 18$ .                                  | 50 |

| 4.10 | Simulation models in HFSS for combline IDC with 22 mils effective fingers length ( $l' = 22$ mils) and various finger numbers, N. (a) Simulation model with 45° view angle, (b) $N = 6$ , (c) $N = 12$ and (d) $N = 18$ .                                             | 51 |

| 4.11 | Simulated return loss and insertion loss responses from 1 GHz to 40 GHz for combline IDC with 22 mils effective finger length ( $l' = 22$ mils) and increasing total fingers.<br>(a) $N = 6$ . (b) $N = 12$ . (c) $N = 18$ .                                          | 52 |

| 4.12 | Normalized impedance profile for combline IDC with 22 mils effective fingers length ( $l' = 22$ mils) and various finger numbers, $N$ , (a) $N = 6$ , (b) $N = 12$ and (c) $N = 18$ .                                                                                 | 53 |

| 4.13 | Capacitance versus frequency trend for both<br>conventional and combline IDCs with 22 mils effective<br>finger length ( $l' = 22$ mils) and 6 fingers ( $N = 6$ ).         | 55 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.14 | Q factor versus frequency trend for both the conventional<br>and combline IDCs with 22 mils effective finger length<br>(l' = 22  mils) and 6 fingers $(N = 6)$ .           | 55 |

| 4.15 | Capacitance versus frequency trend for both the conventional and combline IDCs with 66 mils effective finger length ( $l' = 66$ mils) and 6 fingers ( $N = 6$ ).           | 57 |

| 4.16 | Q factor versus frequency trend for both the conventional<br>and combline IDCs with 66 mils effective finger length<br>(l' = 66  mils) and 6 fingers $(N = 6)$ .           | 57 |

| 4.17 | Capacitance versus frequency trend for both<br>conventional and combline IDC with 110 mils effective<br>finger length ( $l' = 110$ mils) and 6 fingers ( $N = 6$ ).        | 60 |

| 4.18 | Quality factor (Q) versus frequency trend for both<br>conventional and combline IDC with 110 mils effective<br>finger length ( $l' = 110$ mils) and 6 fingers ( $N = 6$ ). | 60 |

| 4.19 | Comparison of Q factor for conventional IDC with various finger lengths.                                                                                                   | 62 |

| 4.20 | Comparison of Q factor for combline IDC with various finger lengths.                                                                                                       | 62 |

| 4.21 | Comparison of Q factor for the conventional IDC with various total finger number, <i>N</i> .                                                                               | 63 |

| 4.22 | Comparison of Q factor for the combline IDC with various total finger number, <i>N</i> .                                                                                   | 64 |

| 5.1  | Planar IDC with combline structure and center feeder.                                                                                                                      | 67 |

| 5.2  | Coplanar IDC with combline structure and center feeder.                                                                                                                    | 68 |

# LIST OF SYMBOLS

| A               | - | Area                                        |

|-----------------|---|---------------------------------------------|

| С               | - | Capacitance                                 |

| d               | - | Distance                                    |

| f               | - | Frequency                                   |

| $f_o$           | - | Self resonance frequency                    |

| h               | - | Dielectric thickness                        |

| L               | - | Inductance                                  |

| l               | - | Fingers length                              |

| l'              | - | Effective fingers length                    |

| М               | - | Number of capacitors connected in a network |

| Ν               | - | Total capacitor fingers                     |

| N'              | - | Total combline fingers per finger           |

| Q               | - | Electric charges                            |

| R               | - | Resistance                                  |

| S               | - | Spacing between fingers                     |

| s'              | - | Spacing between combline fingers            |

| t               | - | Conductor height                            |

| W               | - | Finger width                                |

| w'              | - | Combline fingers width                      |

| $X_c$           | - | Reactance                                   |

| $\mathcal{E}_r$ | - | Dielectric relative permittivity            |

# LIST OF ABBREVIATIONS

| CMOS   | - | Complementary metal oxide semiconductor     |

|--------|---|---------------------------------------------|

| ESL    | - | Equivalent series inductance                |

| ESR    | - | Equivalent series resistance                |

| FDTD   | - | Finite-difference time domain               |

| FEM    | - | Finite element model                        |

| IC     | - | Integrated circuit                          |

| IDC    | - | Interdigital capacitor                      |

| MIM    | - | Metal-insulator-metal                       |

| MOSFET | - | Metal oxide semiconductor effect transistor |

| PCB    | - | Printed circuit board                       |

| Q      | - | Quality factor                              |

| RFIC   | - | Radio frequency integrated circuit          |

|        |   |                                             |

#### **CHAPTER I**

#### INTRODUCTION

#### 1.1 Background of Study

The growth of smaller, more power-sensitive wireless-communication products has fueled the explosive development of radio frequency integrated circuits (RFICs) [1]. Highly integrated RF components now populate ICs, replacing the hybrid circuits that used discrete semiconductor devices. As a result, RFICs can be found in applications that blanket the wireless space, ranging from cellular to wireless LANs and everything in between. There are many challenges involved in creating RFICs. At the transistor level, various competing technologies (GaAs, Si, SiGe, and CMOS) each provide different benefits and drawbacks. Aside from the transistors, the creation of passive components such as inductors, capacitors, and resistors also pose unique challenges to the IC designer.

Passive components are referred to as "glue components" because they "glue" integrated circuits together to make a system. For the accurate design and fabrication of these compact high performance systems, accurate modeling of on chip passive components is becoming very important. However, designing circuits with these passive components is non-trivial due to electromagnetic interactions that lead to parasitic, and ultimately non-ideal frequency behavior. Passive devices generally have complex geometries, non-uniform current flow, and correspondingly complex field patterns; therefore, suffer from parasitic effects that influence the electrical behavior of the device at different frequencies. For this reason, accurate models of passive components are crucial for designing and characterizing high performance systems.

Building high-quality on-chip capacitors has attracted tremendous interest from the RFIC design community and semiconductor manufacturers. High-quality on-chip capacitors have been widely demonstrated as a key factor for successfully integrating RF building blocks, such as resonant circuits and filters, voltagecontrolled oscillators, coupling between stages and bypassing [1]. Other characteristics by which such capacitors are judged include capacitance density; parasitic capacitance to ground; voltage, temperature and frequency coefficients; and the maximum allowable peak repetitive voltage. As shown in *Figure 1.1*, commercial CMOS or BiCMOS processes the following capacitors are generally available:

#### (a) Capacitors that use the MOSFET gate oxide [2]

The highest capacitance densities are obtained with these capacitors. Capacitance density of 6 fF/ $\mu$ 2 has been reported [2]. However, there is a trade-off between the gate oxide thickness and the breakdown voltage. A 50-Angstrom gate oxide capacitor in a 0.25 $\mu$  processes can typically withstand a maximum peak repetitive voltage of 2.75V. Depending on the topology and circuit design this may be a limitation. The CV characteristic varies with the particular process technology and is non-linear. This non-linearity may cause distortion in the circuit.

#### (b) Metal-insulator-metal (MIM) capacitors [3, 4]

MIM capacitors are typically built near the top of the metal stack to minimize parasitic capacitance to ground; for example, a bottom-plate using METAL4 and a top-plate using METAL5 separated by a thin insulator layer a few hundred Angstroms thick. The large separation between the bottom plate and substrate ( $\cong 6\mu$ ) helps in reducing the parasitic capacitance to ground to approximately 2% of the useful inter-metal capacitance (trans-capacitance). MIM capacitors have very good voltage and temperature-coefficient characteristics and a capacitance density of approximately  $0.8 \text{fF}/\mu 2$ . MIM capacitors are available in many RF CMOS and BiCMOS processes, however, they require extra masking steps to implement and increase the cost of the IC. Furthermore, these devices do not scale with process technology

#### (c) Poly-insulator-gate poly (Double Poly) capacitors [2]

Double-poly and MOS capacitors also have parasitic capacitance associated with them. Double-poly capacitors have about 18% parasitic capacitance to ground while MOS capacitors can have 2~20% parasitic capacitance to ground depending upon their design. Both MOS and double-poly capacitors have the problem of very high series resistance to one of the two nodes.

#### (d) Planar Interdigital capacitor (Planar IDC) [5]

Planar Interdigital capacitors hold much promise in providing capacitors that continue to improve with succeeding process technologies. Capacitance density increases significantly as the number of metal layers increase and the feature size decreases. Such capacitors can be optimized to minimize parasitic capacitance and to make the parasitic capacitance symmetric, thus reducing noise pickup from the substrate or nearby structures.

**Figure 1.1:** Different types of CMOS or BiCMOS capacitor. (a) MOSFET gate oxide capacitor, (b) MIM Capacitor, (c) Double-poly capacitor, (d) IDC

### 1.2 Goals and Limitations of On-chip Capacitor Design

High-performance on-chip capacitors are required to implement RF integrated circuits [6]. The main requirements for high-performance capacitors are capacitance density, symmetry and high quality factor. Recent literature [6] emphasizes exclusively either high capacitance density or high Q because improvement in Q tends to come at the expense of capacitance density.

For a number of sensitive applications, capacitors with a Q > 15-20 at frequency range of interest are required. However, there is a limitation in obtaining a

high Q factor especially at high frequency range in most of today's applications. These limitations in the poor Q factor are primary due to the resistive losses in the plates and contacts and due to the parasitic capacitance between the passive component and the lossy silicon substrate [7]. Thus, lots of researches and studies are currently on going and some has been carried out focusing on different ways to obtain high Q and high capacitance capacitors. Some researches focus on various capacitors layout and dimensions; some of these studies focus on material science looking for new low loss materials which is suitable for planar capacitor implementation. Accurate capacitor model which gives accurate simulation results for Q factor and series resistance (ESR) is crucial as well for RF circuit design and characterization.

#### 1.3 Objectives

The main objective of this project is to improve the characteristics of a planar interdigital radio frequency capacitor by employing combine structure. The performance in the form of capacitance and Q factor of the modified interdigital capacitor with the conventional configuration interdigital capacitor are compared. It is aimed to obtain a planar combline interdigital capacitor which is able to produce higher capacitance with sufficiently high Q factor of at least 15 in a wider frequency range which suits today's application in various fields. The basic and combline configurations are depicted in *Figure 1.2*.

Figure 1.2: IDC configurations (a) basic, (b) six fingers.

#### 1.4 Scope of Project

The project is focused on developing an interdigital capacitor configuration that will exhibit a high capacitance density as well as high Q-factor. The scope of the project covers the following areas:

#### Study of the theory and fundamentals of RF interdigital capacitor.

This includes basic design of lumped elements, basic capacitor theories, parameters that affect capacitor performance, parameters that used for capacitor performance evaluation, electrical representation of capacitors, interdigital capacitor design and performance improvement techniques.

# Modification of the conventional interdigital configuration with combline structure for performance improvement.

Based on the theories and work done by other researchers, the study further explore and investigate the possibility of improving the interdigital capacitor performance by varying different layout options with combline structure.

#### Electromagnetic simulations.

Simulations of the conventional and modified interdigital configurations were performed using Ansoft HFSS electromagnetic simulation software.

#### Analysis of the results.

Performance comparison of the modified and conventional configuration interdigital capacitor in terms of Q factor and capacitance density.

### 1.5 Outline of Thesis

Chapter one discusses the objectives and scope of the project and gives a general introduction to RFICs and functions of on chip capacitors in RFIC. This chapter also clearly discusses the motivation behind the study and the limitations in order to achieve the project objectives.

In Chapter two, relevant literature and previous work regarding planar interdigital capacitor characterization are reviewed. This chapter also elaborates on the principles of capacitor and the factors that must be taken into consideration to obtain a good capacitor for RFIC usage.

The design and analysis approach used in this project are elaborated in Chapter three. The overall activities of this study are discussed in this chapter. Besides, this chapter also discusses in detail the capacitor modification flow of the proposed interdigital capacitor with combline structure and simulation flow of the designed capacitors using Ansoft HFSS simulation software.

In Chapter four, the final results are presented and analyzed in detail. This includes the modifications from the basic configuration to various combline configurations.

The final chapter concludes the thesis. Suggestions for further improvement are also presented.

#### REFERENCES

- C.-J. Chao, S.-C. Wong, C.-H. Kao, M.-J. Chen, L.-Y. Leu, K.-Y. Chiu, "Characterization and Modeling of On-Chip Spiral Inductors for Si RFICs", *IEEE Transactions on Semiconductor Manufacturing*, vol. 15, No. 1, February 2002, pp. 19-29.

- [2] National Semiconductor Corporation, 0.25um CMOS Process Electrical Design Rules and Characterization Data, May 2001.

- [3] TSMC, CMOS RF/Mixed-Signal 0.25um process design guide, 2000.

- [4] Jeffery A. Babcock, et. Al, "Analog Characteristics of Metal-Insulator-Metal Capacitors using PECVD Nitride Dielectrics", *IEEE Electron Device Letters*, vol. 22, No. 5, May 2001, pp. 230-232

- [5] http://www.eagleware.com/pdf/apps/0009\_AccuracyProofMidcap.pdf

- [6] J. Kim, J.-O. Plouchartz, N. Zamdmerl, M. Sheronyl, L.-H. Lul, Y. Tan,

M. Yoon, Keith A. Jenkins, M. Kumarl, A. Ray, L. Wagner, "3-Dimensional

Vertical Parallel Plate Capacitors in an SO1 CMOS Technology for

Integrated RF Circuits" VLSI Circuits Digest Symposium, 2003.

- S. Jenei, S. Decoutere, Stefaan V. Huylenbroeck, G. Vanhorebeek, B.

Nauwelaers, "High Q Inductors and Capacitors on Si substrate", *IEEE*, 2001, pp. 64-70.

- [8] <u>http://www.alaska.net/~natnkell/simplcap.html</u>

- [9] J. A. Brandao Fario, "Capacitor Modeling at High Frequencies A Pedagogigal Example of Application of Distributed Circuit Analysis for Introductory Electromagnetic or Microwave Courses", *IEEE Transactions* on Education, vol. 35, No. 3, August 1992, pp. 214-216.

- [10] Johanson Technology Corporation, Q and ESR Explained, November 2004.

- [11] http://www.ecircuitcenter.com/Circuits/cmodel1.htm

- [12] Gary D. Alley, "Interdigital Capacitors and Their Application to Lumped-Element Microwave Integrated Circuits", *IEEE Transactions on Microwave Theory and Techniques*, vol. 18, No. 12, December 1970, pp. 1028-1033.

- [13] F. Aryanfar, Kamal Sarabandi, "Characterization of Semi-lumped CPW Elements for Millimeter-Wave Filter Design", *IEEE Transactions on Microwave Theory and Techniques*, vol. 53, No. 4, April 2005, pp. 1288-1293.

- [14] D. Caratelli, R. Cicchetti, "A Full-Wave Analysis of Interdigital Capacitors for Planar Integrated Circuits", *IEEE Transactions on Magnetic*, vol. 39, No. 3, May 2003. pp. 1598-1601.

- [15] R. S. Chen, X. Zhang, K.F. Tsang, K.N. Yung, "Modeling and Design of Interdigital Capacitor Based on Neural Networks and Genetic Algorithm", *Microwave and Optical Technology Letters*, vol. 38, No. 3, August 2003. pp. 231-235.

- [16] K. G. Ong, J. S. Bitler, C. A.Grimes, "Remote Query Resonant-Circuit Sensors for Monitoring of Bacteria Growth: Application to Food Quality Control", *Sensors*, June 2002, pp. 219-232.

- [17] W. Young, J. Starck, "Series and Parallel Capacitors", *Lessons in Electric Circuits*, vol. 1, 2002.

- [18] R. Esfandiari, D. W. Maki, M. Siracusa, "Design of interdigitated capacitors and their application to gallium arsenide monolithic filters," *IEEE Transactions on Microwave Theory Technology*, vol. 31, No. 1, 1983, pp. 57-64.

- [19] S. G. Spartak, M.Torten, L. J. L. Peter, L. K. Erik, "CAD Model for Multilayered Substrate Interdigital Capacitors", *IEEE Transactions on Microwave Theory and Techniques*, vol. 44, No. 6, June 1996, pp. 896-904.

- [20] L. Yu, S. N. Amit, G. E. Erich, R. T. Troy, S. James, A. Y. Robert, "BaSrTiO<sub>3</sub> Interdigitated Capacitors for Distributed Phase Shift Applications", *IEEE Microwave and Guided Wave Letters*, vol. 10, No. 11, November 2000, pp. 448-450.

- [21] L. H. John, "Optimization of Interdigital Capacitors", *IEEE Transactions on Microwave Theory and Techniques*", vol. MTT-27, No. 9, September 1979, pp. 788-791.