# HARDWARE/SOFTWARE CO-DESIGN OF TWO-STAGE SMART ARRHYTHMIA CLASSIFIER BASED ON MULTI-PROCESSOR FIELD PROGRAMMABLE GATE ARRAY SYSTEM-ON-CHIP

OOI TZE KIAN

A project report submitted in partial fulfilment of the requirements for the award of the degree of Master of Engineering (Computer and Microelectronic Systems)

> School of Electrical Engineering Faculty of Engineering Universiti Teknologi Malaysia

> > FEBRUARY 2022

### **DEDICATION**

This thesis is dedicated to my father, who taught me that the best kind of knowledge to have is that which is learned for its own sake. It is also dedicated to mymother, who taught me that even the largest task can be accomplished if it is done onestep at a time.

#### ACKNOWLEDGEMENT

First and foremost, I would like to express my deepest gratitude to my main supervisor, Prof. Muhammad Nadzir Bin Marsono and my second supervisor, Dr Hau Yuan Wen. Without their continuous assistance and dedicated involvement in every step throughout theflow, this project would have never yield results.

I am also indebted to Universiti Teknologi Malaysia (UTM) for the opportunities granted for my master studies. Lecturers, laboratory assistants at School of Electrical Engineering deserve special thanks for their assistance in supplying facilities and relevant publications for literature reviews.

My dearest seniors, Lim Huey Woan and Lim Zhi Qing had shared their advices and research experiences to me were really appreciated. I have many caring friends who have tolerated my overwhelming enquiries over these years. I would like to express my gratitude and sincere apologies to Lim Wei Fang and Tan Zhi Wei.

Most importantly, my families who are always there whenever I need to take a break. To my dearest parents, their unconditional love have propelled me further in my life. I love you all and thanks for everything.

#### ABSTRACT

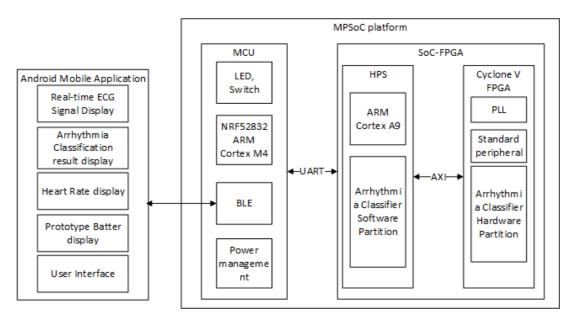

Cardiovascular diseases are the top cause of deaths in Malaysia since 2000. Arrhythmia is one of the precursors for cardiovascular disease that can be diagnosed via electrocardiogram (ECG). This research proposes an embedded multi-processor system-on-chip (MPSoC) architecture of in-house smart arrhythmia classifier using Nordic NRF5282 microcontroller unit (MCU) and DBM Cyclone V system-on-chip SoC (DBM SoC). The MCU houses Bluetooth low energy (BLE) and a 64 MHz Cortex-M4 processor. DBM SoC consists offield programmable gate array (FPGA) with logic elements (LE) and a hardcore ARM Cortex A9 processor that can run at 800MHz frequency. Hardware accelerator for compute intensive Fast Fourier Transform (FFT) is implemented in FPGA using soft intellectual property (IP) provided by vendor Intel. The high-performance DBM SoC will execute arrhythmia classification while the MCU act as master processor that are able to power cycle DBM SoC. Bluetooth communication between MCU and external mobile phone allow user to control DBM SoC, ECG acquisition via mobile phone. Sanity verification, timing performance benchmarking and power measurement are performed on the proposed MPSoC system. Results show that the proposed MPSoC system is able to classify an ECG signal into 6 types of arrhythmias namely Atrial Fibrilaltion (AFib), Ventricular Tachycardia (VTach), premature atrial contractions (PAC), premature ventricular contractions (PVC), left bundle branch block (LBBB), right bundble branch block (RBBB) and normal sinus rhythm (NSR). The proposed system is also able to classify a 10 seconds ECG input data within 1 second, equivalent to real-time detection performance. Results also show the battery-powered MPSoC platform consumes less power in idle mode when the DBM SoC is turned off. The battery life is greatly improved which increase portability and usability as well.

#### ABSTRAK

Penyakit kardiovaskular adalah salah satu penyakit pembunuh utama di Malaysia sejak 2000. Aritmia adalah salah satu punca penyakit kardiovaskular yang boleh didiagnosis dengan peranti elektrokardiogram (ECG). Projek ini membentangkan reka bentuk dalaman aritmia pengelas dengan kaedah seni bina berbilang pemproses system-on-chip (MPSoC) menggunakan unit mikropengawal Nordic NRF52832 (MCU) dan DBM Cyclone V system-on-chip (DBM SoC). MCU menpunyai Bluetooth low energy (BLE) dan 64 MHz pemproses Cortex-M4. DBM SoC menpunyai Field Programmable Gate Array (FPGA) dengan unsur logik (LE) dan pemproses ARM Cortex A9 yang dapat beroperasi di 800 MHz. Pemecut perkakasan Fast Fourier Transform (FFT) yang menggunakan Intel FFT IP telah dilaksanakan. DBM SoC yang berpretasi tinggi akan melaksanakan pengelasan aritmia manakala MCU yang bertindak sebagai pemproses utama boleh mengawal DBM SoC. Komunikasi Bluetooth antara MCU dan telefon bimbit membolehkan pengguna mengawal DBM SoC, pemerolehan ECG melalui telefon bimbit. Pengesahan kewarasan, penanda aras prestasi masa dan pengukuran kuasa dilakukan pada sistem MPSoC yang dicadangkan. Sistem yang dicadangkan juga boleh mengklasifikasikan data input ECG 10 saat dalam masa 1 saat, bersamaan dengan prestasi pengesanan masa nyata. Keputusan juga menunjukkan platform MPSoC berkuasa bateri menggunakan lebih sedikit kuasa dalam mod melahu apabila SoC DBM dimatikan. Hayat bateri bertambah baik yang meningkatkan kemudahalihan dan kebolehgunaan juga.

### TABLE OF CONTENTS

|           | TITLE                                   | PAGE |  |

|-----------|-----------------------------------------|------|--|

|           | DECLARATION                             | ii   |  |

|           | DEDICATION                              | iii  |  |

|           | ACKNOWLEDGEMENT                         | iv   |  |

|           | ABSTRACT                                | v    |  |

|           | ABSTRAK                                 | vi   |  |

|           | TABLE OF CONTENTS                       | vii  |  |

|           | LIST OF TABLES                          | X    |  |

|           | LIST OF FIGURES                         | xi   |  |

|           | LIST OF ABBREVIATIONS                   | xiii |  |

| CHAPTER 1 | INTRODUCTION                            | 1    |  |

| 1.1       | Project Background                      | 1    |  |

| 1.2       | Problem Statement                       | 2    |  |

| 1.3       | Objective                               | 4    |  |

| 1.4       | Project Scope                           |      |  |

| 1.5       | Project Report Organization             |      |  |

| CHAPTER 2 | LITERATURE REVIEW                       | 6    |  |

| 2.1       | Cardiac Rhythm                          | 6    |  |

| 2.2       | Arrhythmia                              | 7    |  |

|           | 2.2.1 Atrial Fibrillation               | 8    |  |

|           | 2.2.2 Ventricular Tachycardia           | 9    |  |

|           | 2.2.3 Premature Atrial Contraction      | 9    |  |

|           | 2.2.4 Premature Ventricular Contraction | 10   |  |

|           | 2.2.5 Right Bundle Branch Block         | 11   |  |

|           | 2.2.6 Left Bundle Branch Block          | 12   |  |

| 2.3       | Multi-processor System-on-Chip (MPSoC)  | 12   |  |

|           | 2.3.1 Embedded System-on-Chip (SoC)     | 15   |  |

| 2.4       | Hardware/Software Co-design             |      |  |

2.4 Hardware/Software Co-design

| 2.5       | Embedded Linux and Bare Metal                          |    |  |  |  |

|-----------|--------------------------------------------------------|----|--|--|--|

| 2.6       | Related Research Works                                 |    |  |  |  |

|           |                                                        |    |  |  |  |

| CHAPTER 3 | PROJECT METHODOLOGY                                    | 25 |  |  |  |

| 3.1       | Project Overview                                       | 25 |  |  |  |

| 3.2       | Project Workflow                                       | 26 |  |  |  |

| 3.3       | Hardware Prototyping Board for Emulation of Arrhythmia |    |  |  |  |

|           | Classifier                                             | 28 |  |  |  |

| 3.4       | Intel FPGA-SoC based Design Methodology                | 30 |  |  |  |

| 3.5       | ARM Embedded SoC based Design Methodology              | 31 |  |  |  |

| 3.6       | EDA Designs Software and Tools                         | 33 |  |  |  |

| 3.7       | Verification Tools                                     | 35 |  |  |  |

|           | 3.7.1 ProSim Fluke 3 Vital Sign Simulator              | 35 |  |  |  |

| 3.8       | Chapter Summary                                        | 36 |  |  |  |

|           |                                                        |    |  |  |  |

| CHAPTER 4 | PROJECT DESIGN                                         | 37 |  |  |  |

| 4.1       | Top Level System Architecture of Arrhythmia Classifier | 37 |  |  |  |

| 4.2       | Top Level System Behavior of Arrhythmia Classifier     | 39 |  |  |  |

| 4.3       | Nordic MCU Hardware design                             | 41 |  |  |  |

|           | 4.3.1 Communication Bus Interface Design               | 41 |  |  |  |

| 4.4       | Mobile Application Design                              | 48 |  |  |  |

| 4.5       | Chapter Summary                                        | 48 |  |  |  |

| CHAPTER 5 | RESULT AND DISCUSSION                                  | 51 |  |  |  |

| 5.1       | Mobile Application ECG Waveform and Classification     | 01 |  |  |  |

| 5.1       | Result Real-time Display                               | 51 |  |  |  |

| 5.2       | Detection Accuracy Analysis                            | 51 |  |  |  |

| 5.3       | Computation Timing Performance on MPSoC Platform       | 54 |  |  |  |

| 5.4       | System Power Performance on MPSoC                      | 55 |  |  |  |

| 5.5       | Chapter Summary                                        | 57 |  |  |  |

| 5.5       | Chapter Summary                                        | 57 |  |  |  |

| CHAPTER 6 | CONCLUSION                                             | 58 |  |  |  |

| 6.1       | Concluding Remark                                      | 58 |  |  |  |

| 6.2 | Limitation and Recommendation for Future Works | 59 |

|-----|------------------------------------------------|----|

| 6.3 | Project Benefits                               | 60 |

## REFERENCES

### LIST OF TABLES

| TABLE NO. | TITLE                                                   | PAGE |

|-----------|---------------------------------------------------------|------|

| Table 2.1 | Difference between loosely-coupled and tighly-coupled   |      |

|           | systems                                                 | 15   |

| Table 2.2 | List of standard peripherals in FPGA system module.     | 18   |

| Table 2.3 | Design trade-offof hardware/software co-design.         | 20   |

| Table 2.4 | Embedded Linux VS Bare Metal.                           | 21   |

| Table 2.5 | Related Works                                           | 24   |

| Table 3.1 | EDA Software Tools                                      | 34   |

| Table 4.1 | RS232 Communication settings.                           | 42   |

| Table 4.2 | UART Communication pins.                                | 42   |

| Table 4.3 | Communication packet format.                            | 43   |

| Table 4.4 | Unsolicited response for battery voltage and level.     | 44   |

| Table 4.5 | List of Commands used in the MPSoC.                     | 45   |

| Table 4.6 | List of Responses used in the MPSoC.                    | 46   |

| Table 5.1 | Confusion matrix parameters.                            | 52   |

| Table 5.2 | Detection accuracy analysis of Arrhythmia classifier on |      |

|           | proposed MPSoC.                                         | 53   |

| Table 5.3 | Computation performance with FFT hardware accelerator.  | 54   |

| Table 5.4 | Computation performance between NIOS II and MPSoC       |      |

|           | ARM A9.                                                 | 55   |

| Table 5.5 | Power consumption in sleep mode.                        | 56   |

| Table 5.6 | Power consumption in idle mode.                         | 56   |

| Table 5.7 | Power consumption in standby mode.                      | 56   |

| Table 5.8 | Power consumption in processing mode.                   | 56   |

### LIST OF FIGURES

| FIGURE NO.  | TITLE                                                      | PAGE |

|-------------|------------------------------------------------------------|------|

| Figure 1.1  | Top causes of death in Malaysia, 2018 & 2019 [1].          | 1    |

| Figure 1.2  | Project Scope.                                             | 5    |

| Figure 2.1  | Cardiac rhythm system.                                     | 7    |

| Figure 2.2  | ECG waveform of normal sinus rhythm.                       | 8    |

| Figure 2.3  | Atrial Fibrillation ECG.                                   | 9    |

| Figure 2.4  | Ventricular Tachycardia ECG.                               | 10   |

| Figure 2.5  | Premature Atrial Contraction ECG.                          | 10   |

| Figure 2.6  | Premature Ventricular Contractions.                        | 11   |

| Figure 2.7  | Right Bundle Branch Block ECG.                             | 11   |

| Figure 2.8  | Left Bundle Branch Block ECG.                              | 12   |

| Figure 2.9  | Loosely-coupled microprocessor system.                     | 13   |

| Figure 2.10 | Tightly-coupled microprocessor system.                     | 14   |

| Figure 2.11 | SoC hardware architecture.                                 | 16   |

| Figure 2.12 | Top level architecture of Cyclone V SoC-FPGA device.       | 17   |

| Figure 2.13 | Hardware module offloading.                                | 19   |

| Figure 2.14 | Typical bootflow of embedded OS.                           | 20   |

| Figure 3.1  | Project workflow.                                          | 28   |

| Figure 3.2  | MPSoC development board.                                   | 29   |

| Figure 3.3  | MPSoC development board block diagram.                     | 30   |

| Figure 3.4  | Development of Intel SoC embedded system.                  | 31   |

| Figure 3.5  | Designflow for embedded ARM SoC.                           | 32   |

| Figure 3.6  | Path to include external library.                          | 33   |

| Figure 3.7  | Software Debugging using RTT viewer.                       | 34   |

| Figure 3.8  | Vital Sign Simulator as algorithm functional verification. | 35   |

| Figure 4.1  | Top level system architecture.                             | 38   |

| Figure 4.2  | Top level behaviouralflowchart of Arrhythmia classifier.   | 40   |

| Figure 4.3  | Nordic MCU state diagram.                                  | 41   |

| Figure 4.4  | Communication bus interface.                               | 42   |

| Figure 4.5  | RES_SENSE_DATA packet format.                              | 44   |

| Figure 4.6 | nRF Connect console log.                                  | 47 |

|------------|-----------------------------------------------------------|----|

| Figure 4.7 | Mobile application BLE packet decode block.               | 49 |

| Figure 4.8 | Mobile application user interface.                        | 50 |

| Figure 5.1 | Real-time ECG waveform and classification result display. | 52 |

### LIST OF ABBREVIATIONS

| CVD   | - | Cardiovascular Diseases            |

|-------|---|------------------------------------|

| AFib  | - | Atrial Fibrillation                |

| VTach | - | Ventricular Tachycardia            |

| PAC   | - | Premature Atrial Contractions      |

| PVC   | - | Premature Ventricular Contractions |

| LBBB  | - | Left Bundle Branch Block           |

| RBBB  | - | Right Bundle Branch Block          |

| NSR   | - | Normal Sinus Rhythm                |

| MCU   | - | Microcontroller Unit               |

| MPSoC | - | Multiprocessor system-on-chip      |

| BLE   | - | Bluetooth Low Energy               |

| FPGA  | - | Field Programmable Gate Array      |

| FFT   | - | Fast Fourier Transform             |

| LE    | - | Logic Elements                     |

| RTC   | - | Real-time Clock                    |

| ECG   | - | Electrocardiogram                  |

| AV    | - | Atrialventricular                  |

| SA    | - | Sinoatrial                         |

| SCA   | - | Sudden Cardiac Arrest              |

| SCD   | - | Sudden Cardiac Death               |

| CPU   | - | Central Processing Unit            |

| GPU   | - | Graphical Processing Unit          |

| SoC   | - | system-on-chip                     |

| OCCA  | - | On-chip Communication Architecture |

| MPU   | - | Microprocessor Unit                |

| PLL   | - | Phase Lock Loop                    |

| DMA    | - | Dynamic Memory Access                       |

|--------|---|---------------------------------------------|

| EMACS  | - | Ethernet Media Access Controller            |

| OTG    | - | On-The-Go                                   |

| MMC    | - | Multimedia Card                             |

| SPI    | - | Serial Peripheral Interface                 |

| I2C    | - | Inter-integrated Circuit                    |

| CAN    | - | Controller Area Network                     |

| UART   | - | Universal Asynchronous Receiver Transmitter |

| DAP    | - | Debug Access Port                           |

| ETR    | - | Embedded Trace Router                       |

| HDL    | - | Hardware Descriptive Language               |

| CU     | - | Control Unit                                |

| DPU    | - | Datapath Unit                               |

| FSM    | - | Finite State Machine                        |

| ADC    | - | Analog to Digital Converter                 |

| PIO    | - | Peripheral Input-Output                     |

| OS     | - | Operating System                            |

| LUT    | - | Look-up Table                               |

| VF     | - | Ventricular Fibrillation                    |

| FF     | - | Flip Flop                                   |

| RAM    | - | Random Access Memory                        |

| BRAM   | - | Block RAM                                   |

| SoCEDS | - | System-on-Chip Embedded Design Suite        |

| GSRD   | - | Golden System Reference Design              |

| SCP    | - | Secure Copy                                 |

| EDA    | - | Electronic Design Automation                |

| HPS    | - | Hard Processor System                       |

| ТР     | - | True Positive                               |

| TN     | - | True Negative                               |

|        |   |                                             |

| FP    | - | False Positive                                     |

|-------|---|----------------------------------------------------|

| FN    | - | False Negative                                     |

| ALM   | - | Adaptive Logic Module                              |

| CMSIS | - | Common Microcontroller Software Interface Standard |

| NN    | - | Neural Network                                     |

| DSP   | - | Digital Signal Processing                          |

| HLS   | - | High Level Synthesis                               |

### **CHAPTER 1**

### **INTRODUCTION**

#### 1.1 **Project Background**

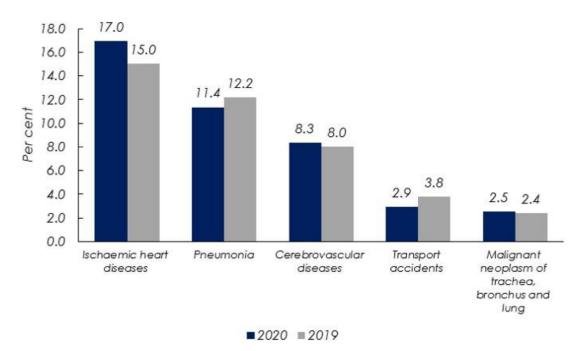

Based on Department of Statistics Malaysia, ischemic heart diseases contributed highest mortalities in Malaysia in 2019 compared to other causes of death, such as pneumonia and cerebrovascular diseases [1]. In fact, ischemic heart diseases and stroke are the top cause of death globally since 2000 [2]. Figure 1.1 illustrates 16% of the total deaths are caused by ischemic heart diseases in Malaysia. This proves that cardiovascular diseases (CVD) remains the top killers since 2000 consecutively.

Figure 1.1 Top causes of death in Malaysia, 2018 & 2019 [1].

Arrhythmia, the precursor of CVDs, is the abnormal rhythm of the heartbeat that caused by irregularities at the cardiac conduction of electrical signals [3, 4]. Common arrhythmias such as ventricular tachycardia can lead to ventricularfibrillation and eventually sudden cardiac arrest [4, 5]. Patients with atrialfibrillation has higher

probabilities of evolving stroke [6]. Arrythmia has obscure symptoms and most patients neither aware of it nor take frequent heart monitoring test. It can only be detected via electrocardiogram (ECG) analysed by cardiologist. Hence, CVDs are also known as the silent killers. The best approach to mitigate the mortality caused by CVDs is via frequent heart monitoring to detect any abnormalities in heart rhythm.

ECG is a non-invasive procedure which measures electrical signals generated by the heart chamber during cardiac cycle [7]. It provides essential details on the heart's rhythm. Cardiologists perform diagnosis based on the signal waveform generated by the heart. However, ECG devices are cost expensive and most of them only acquire impulses but still require professionals to analyse the data. The classification performed is not standalone. Generally, ECG devices available in the market that provide classification functionality, usually do not have state-of-the-art classification algorithm or do not have the capabilities to detect multiple arrhythmias. One example is Holter monitor which although are portable, it performs ECG acquisition solely and the data has to be processed at hospital afterwards [8]. Hospitals do possess advance ECG equipment but those devices are bulky, costly and consume high power.

### **1.2 Problem Statement**

Thoughfield programmable gate array system-on-chip (FPGA SoC) provides the capability of running compute intensive algorithm with superior performance in short design cycle [9, 10], the power consumption is higher compared to applicationspecific integrated circuit (ASIC). Low power design is a critical design attribute in portable device as the power source depends solely on the built-in battery [11]. Hence FPGA SoC is suitable for prototyping within short design cycle or devices who are constantly connected to a wall socket. FPGA SoC requires constant power fed to enable continuous arrhythmia algorithm processing. This put a strain on the battery and generates heat which cause discomforts to user.

Existing device in market able to perform ECG classification using microcontroller which utilize low power consumption and dissipate less heat compared

to FPGA SoC. However, the microcontroller devices are using less powerful processor cores that are not able to perform sophisticated algorithm for higher detection accuracy [10]. In addition, the existing devices are only able to detect single arrhythmia which are not practical as there are more than a few arrhythmias which are life-threatening. Some ECG devices, such as Holter monitor, are not standalone and only acquire ECG signals that is needed to transfer to external computing power forfinal classification. To leverage the low power dissipation of microcontroller coupled with high compute performance of FPGA-SoC, multi-processor architecture is explored. Multiple arrhythmia classifications based on machine learning for heart ECG monitoring are a complex algorithm which require efficient computing architecture, such as multi-processor embedded system to perform real-time processing performance.

To reduce power consumption, compute-intensive with higher power consumption processing block is switched offwhen the device is in hibernate state where background processes such as Bluetooth, power monitoring and data logging are executed by the main processor to ensure basic interaction with user. A systematic approach is required to develop complex master-slave multi-processor embedded system processing architecture that involve embedded OS kernel as well as communication bus protocol between master and slave peripherals. Data integrity is important as well in multi-processor architecture as the clocks are running at different frequencies. Hence, a robust communication bus protocol ensures the data transfer between processors is valid and uncorrupted.

Multiple arrhythmia classifications based on machine learning are complicated and occupied all the resources in single processor. An efficient computing architecture is required to perform classification algorithm as well as peripheral processes (Bluetooth, RTC etc.) simultaneously. SoC FPGA houses a hard processor system (HPS) which consists of a powerful physical processor such as Cortex ARM and FPGA portion which consists of logic elements for hardware accelerator implementation to improve performance but at the cost of higher power consumption compared to microcontrollers. Existing algorithm implemented on development board requires power supply from power outlet which is bulky and reduces portability. Hence, this project proposes an ECG monitoring equipment for multiple arrhythmias detection based on multiprocessor system-on-chip (MPSoC) architecture technology targeting general public. The prototype will consume less power, have Bluetooth capabilities for edge user usability and able to detect 6 types of arrhythmias in real time performance with high accuracy. Functionality verified prototype will retain the same classification capabilities albeit consume less power. Patients are referred to hospital for further diagnosis and follow-up treatment.

### 1.3 **Objective**

Based on the aforementioned problem statement, this project aims to design a device with power optimization capable of executing multiple arrhythmia classifications:

- To design a smart arrhythmia classifier based on master-slave method on multiprocessor-based embedded system with combination of Nordic ARM microprocessor, Cyclone V FPGA-SoC and battery module onboard.

- 2. To develop a proof-of-concept lab demonstration prototype by integration of the smart arrhythmia classifier in (1) with in-house mobile app to form the complete heart monitoring application.

- 3. To conduct system functionality verification and performance measurement in term of timing and power.

### 1.4 Project Scope

The system prototyping platform is targeted for a development board which implements multi-processor architecture that houses Nordic nRF52832 chip which act as the master SoC and a DBM Cyclone V FPGA SoC chip as the slave SoC. The processing architecture is designed based on hardware/software co-design technique. The overall system functionality is tested with ECG signals generated from Fluke ProSim 3 patient simulator. Six types of arrhythmias such as Afib, Vtach, PAC, PVC, LBBB, RBBB and normal sinus rhythm. This project focuses on implementation technology, there are no changes required on algorithm processingflow. The algorithms are ported over from the previous research [12, 13]. On the slave processor, HPS houses arrhythmia classifier algorithm and FFT software driver. FPGA portion houses FFT hardware accelerator. Android application is modified to illustrate real-time ECG signal display, arrhythmia classification result, heart rate display and prototype's battery display. Figure 1.2 below depicts the scope of work.

Figure 1.2 Project Scope.

### **1.5 Project Report Organization**

This project report is divided into six chapters where thefirst chapter has discussed the project background, problem statement, project objectives and scope of work. The second chapter presents the related knowledge background as well as the related work by other researchers in recent years. The project methodology chapter discusses the research and design workflow with associated design tools. Chapter 4 discusses the proposed MPSoC implementation in detail. All the result will be presented in Chapter 5 with analysis discussion. Finally, Chapter 6 concludes this project and recommendation for future works.

### REFERENCES

- Statistics on Causes of Death, Malaysia, 2020. URLhttps://www.dosm. gov.my.

- 2. Cause-Specific Mortality 2000-2019, 2020. URLhttps://www.who.int.

- 3. Chee, K. and Tan, K. Impact of atrialfibrillation among stroke patients in a Malaysian teaching hospital.*Med J Malaysia*, 2014. 69(3): 119–23.

- 4. Thaler, M. S.*The only EKG book you'll ever need*. Lippincott Williams & Wilkins. 2021.

- 5. Malmivuo, J., Plonsey, R.et al. Bioelectromagnetism: principles and applications of bioelectric and biomagneticfields. Oxford University Press, USA. 1995.

- Wolf, P. A., Dawber, T. R., Thomas, H. E. and Kannel, W. B. Epidemiologic assessment of chronic atrialfibrillation and risk of stroke: Thefiamingham Study.*Neurology*, 1978. 28(10): 973–973.

- Thakor, N. V. and Zhu, Y.-S. Applications of adaptivefiltering to ECG analysis: noise cancellation and arrhythmia detection.*IEEE transactions on biomedical engineering*, 1991. 38(8): 785–794.

- 8. Chung, E. K.Ambulatory electrocardiography: holter monitor electrocardiography. Springer Science & Business Media. 2013.

- 9. Muhammad Amin, H.*Real-Time Arrhythmia Classifier Hardware/Software* Architecture on Field Programmable Gate Array. Master's thesis. Universiti Teknologi Malaysia. 2016.

- Yuan Wen, H.An Embedded Cryptosystem Implementing Symmetric Cipher and Public-Key Crypto Algorithms In Hardware. Phd's thesis. Universiti Teknologi Malaysia. 2005.

- Rajesvari, R., Manoj, G. and Angelin Ponrani, M. System-on-Chip (SoC) for Telecommand System Design. *International Journal of Advanced Research in Computer and Communication Engineering*, 2013. 2(3): 1580–1585.

- Huey Woan, L.Embedded System-On-Chip Architecture of Atrial Fibrillation Classifier using Stationary Wavelet Transform and Artificial Neural Network. Master's thesis. Universiti Teknologi Malaysia. 2018.

- Lim, H. W., Mohd Sani, M., Hashim, A. and Hau, Y. W. Throb: System-on-chip based arrhythmia screener with self interpretation.*International Journal of Electrical and Electronic Systems Research,(Special issue: Innovate Malaysia Design Conference)*. 2015, vol. 8. 30–36.

- Heidenreich, P. A., Albert, N. M., Allen, L. A., Bluemke, D. A., Butler, J., Fonarow, G. C., Ikonomidis, J. S., Khavjou, O., Konstam, M. A., Maddox, T. M.*et al*.Forecasting the impact of heart failure in the United States: a policy statement from the American Heart Association.*Circulation: Heart Failure*, 2013. 6(3): 606–619.

- 15. Tikkanen, P.Characterization and application of analysis methods for ECG and time interval variability data. Oulun yliopisto. 1999.

- Go, A. S., Hylek, E. M., Phillips, K. A., Chang, Y., Henault, L. E., Selby, J. V. and Singer, D. E. Prevalence of diagnosed atrialfibrillation in adults: national implications for rhythm management and stroke prevention: the AnTicoagulation and Risk Factors in Atrial Fibrillation (ATRIA) Study.*Jama*, 2001. 285(18): 2370–2375.

- Malmivuo, J. and Plonsey, R. Bioelectromagnetism.*Medical and Biological* Engineering and Computing, 1996. 34: 9–12.

- Pitts, N. Scottish intercollegiate guidelines network. Preventing dental caries in children at high caries risk.[En línea]. 2002.

- Wolf, W., Jerraya, A. A. and Martin, G. Multiprocessor system-on-chip (MPSoC) technology.*IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2008. 27(10): 1701–1713.

- 20. Morady, F. and Zipes, D. P. Atrialfibrillation: Clinical features, mechanisms, and management.*Braunwald's Heart Disease: A Textbook of Cardiovascular Medicine*, 2012. 1: 825–844.

- Podrid, P. J., Lampert, S., Graboys, T. B., Blatt, C. M. and Lown, B. Aggravation of arrhythmia by antiarrhythmic drugs—incidence and predictors. *The American journal of cardiology*, 1987. 59(11): E38–E44.

- Dewland, T. A., Vittinghoff, E., Mandyam, M. C., Heckbert, S. R., Siscovick, D. S., Stein, P. K., Psaty, B. M., Sotoodehnia, N., Gottdiener, J. S. and Marcus, G. M. Atrial ectopy as a predictor of incident atrialfibrillation: a cohort study. *Annals of internal medicine*, 2013. 159(11): 721–728.

- 23. Sreejaa, B., Jayanthy, T. and Logashanmugam, E. FPGA Implementation of Parallel Pipelined Multiplier Less FFT Architecture Based System-On-Chip Design Targetting Multimedia Applications.2007 International Conference on Signal Processing, Communications and Networking. IEEE. 2007. 592–595.

- Aravindakshan, V., ELIZARI, M. V. and ROSENBAUM, M. B. Right bundle-branch block and left anterior fascicular block (left anterior hemiblock) following tricuspid valve replacement.*Circulation*, 1970. 42(5): 895–902.

- Jensen, T. J., Haarbo, J., Pehrson, S. M. and Thomsen, B. Impact of premature atrial contractions in atrialfibrillation. *Pacing and clinical electrophysiology*, 2004. 27(4): 447–452.

- Kraus, J. and Förster, M. Efficient AMG on heterogeneous systems. In: *Facing the Multicore-Challenge II*. Springer. 133–146. 2012.

- 27. Shen, J. P. and Lipasti, M. H.*Modern processor design: fundamentals of superscalar processors*. Waveland Press. 2013.

- Aithal, S. and Kumar, S. K. Reconfigurable Triple Modular Redundant and N-Modular Redundant systems with variable Reliability in multi-processor environment.2012 18th International Conference on Advanced Computing and Communications (ADCOM). IEEE. 2012. 33–38.

- 29. nRF52832 Product Specification v1.4, 2017. URLhttps://infocenter. nordicsemi.com/pdf/nRF52832\_PS\_v1.4.pdf.

- Novickis, R. and Greitāns, M. FPGA Master based on chip communications architecture for Cyclone V SoC running Linux.2018 5th International Conference on Control, Decision and Information Technologies (CoDIT). IEEE. 2018. 403–408.

- 31. Devboards DBM-SoC1 module, 2015. URLhttps://rocketboards.org.

- 32. Maxfield, C.Designus Maximus Unleashed!Newnes. 1998.

- Moore, A. FPGAs for dummies. *Altera Special Edition. Hoboken: John Wiley* & Sons, Inc, 2014.

- Hagl, J., Mann, O. and Pirker, M. Securing the Linux Boot Process: From Start to Finish.*ICISSP*. 2021. 604–610.

- 35. Zairi, H., Kedir Talha, M., Meddah, K. and Ould Slimane, S. FPGAbased system for artificial neural network arrhythmia classification.*Neural Computing and Applications*, 2020. 32(8): 4105–4120.

- Dell'aquila, C. R., Cañadas, G., Sistena, C. and Laciar, E. Implementation of a simple real-time algorithm for ventricularfibrillation detection in a microcontroller. *VI Latin American Congress on Biomedical Engineering CLAIB 2014, Paraná, Argentina 29, 30 & 31 October 2014*. Springer. 2015. 655–658.

- Przystup, P., Przystup, A., Bujnowski, A. and Wtorek, J. ECG-based prediction of ventricularfibrillation by means of the PCA.2014 IEEE International Symposium on Medical Measurements and Applications (MeMeA). IEEE. 2014. 1–5.

- Bote, J. M., Recas, J., Rincón, F., Atienza, D. and Hermida, R. A modular low-complexity ECG delineation algorithm for real-time embedded systems. *IEEE Journal of Biomedical and Health Informatics*, 2017. 22(2): 429–441.

- de Carvalho Junior, H. H., Moreno, R. L., Pimenta, T. C., Crepaldi, P. C. and Cintra, E. A heart disease recognition embedded system with fuzzy cluster algorithm.*Computer methods and programs in biomedicine*, 2013. 110(3): 447–454.

- 40. Railis, K., Tsoutsouras, V., Xydis, S. and Soudris, D. Energy profile analysis of Zynq-7000 programmable SoC for embedded medical processing: Study on ECG arrhythmia detection.2016 26th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS). IEEE. 2016. 275–282.

Tze Kian, O.Smart Home-Based Heart Monitoring Device Design based on Intel ARM-SoC Technology for Self-Detection of Cardiovascular Diseases. Bachelor's fyp. Universiti Teknologi Malaysia. 2019.